主从jk触发器工作原理

电工电子技术基础知识点详解1-4-JK触发器

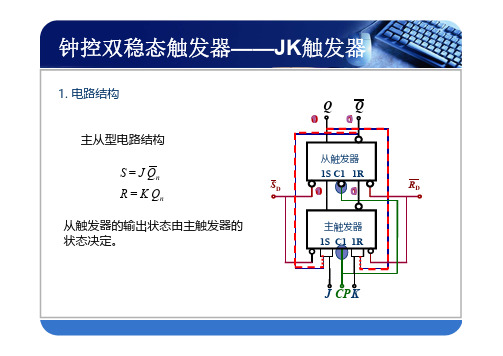

钟控双稳态触发器——JK 触发器1. 电路结构主触发器J KR DCP 1S C1 1RS DQQ1S C1 1R从触发器0111010S = J Q nR =K Q n主从型电路结构从触发器的输出状态由主触发器的状态决定。

钟控双稳态触发器——JK 触发器主触发器J KR DCP 1S C1 1RS DQ Q1S C1 1R从触发器CPF 主打开F 主状态由J 、K 决定,接收信号。

F 从关闭Q 状态保持不变。

1状态保持不变。

F 从打开F 主封锁从触发器的状态取决于主触发器,并保持主、从状态一致。

2. 触发方式主从触发钟控双稳态触发器——JK触发器S D Q Q1K1JC1R DJ KCP S DQ Q1K1JC1R DJ KCP后沿主从触发前沿主从触发3. 逻辑符号钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQ Q1S C1 1R从触发器J KQ n +10 00 11 01 1S = J Q nR =K Q n0 0Q n保持不变0010Q n4. 逻辑功能钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQQ1S C1 1R从触发器J KQ n +10 00 11 01 10 10 10010Q n设原态为00 14. 逻辑功能钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQ Q1S C1 1R从触发器J KQ n +10 00 11 01 10 10 10110Q n设原态为11 00 104. 逻辑功能钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQ Q1S C1 1R从触发器J KQ n +10 00 11 01 11 01 01010Q n设原态为00 101 014. 逻辑功能钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQQ1S C1 1R从触发器J KQ n +10 00 11 01 11 01 00010Q n设原态为11 0014. 逻辑功能钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQ Q1S C1 1R从触发器J KQ n +10 00 11 01 11 11 01010Q n设原态为00 101 0114. 逻辑功能钟控双稳态触发器——JK 触发器主触发器J K R D1S C1 1RS DQ Q1S C1 1R从触发器J KQ n +10 00 11 01 11 10 10110Q n设原态为11 000 110Q n记忆置数计数4. 逻辑功能钟控双稳态触发器——JK 触发器【例】已知后沿主从触发的JK 触发器,J 和K 端的输入信号波形如图所示,而且已知触发器原为0 态,求输出端Q 的波形。

jk边沿触发器工作原理

jk边沿触发器工作原理小伙伴!今天咱们来唠唠JK边沿触发器这个超有趣的东西。

JK边沿触发器呢,就像是一个超级聪明又有点小脾气的小机灵鬼。

它呀,主要是用来处理数字信号的,在数字电路的世界里可是个相当重要的角色哦。

咱先从它的基本结构说起。

它是由一些逻辑门组成的,这些逻辑门就像是一群小伙伴,各自有着不同的任务,然后组合在一起就干出了大事。

这里面有与门、非门之类的逻辑门,它们相互连接,就构建起了JK边沿触发器这个独特的存在。

那它到底是怎么工作的呢?想象一下,JK触发器有两个输入,J和K,就像它的两只小耳朵,在时刻等着信号输入呢。

当有合适的时钟信号到来的时候,它就开始“行动”啦。

在时钟信号的边沿,也就是时钟信号从低电平变成高电平(上升沿)或者从高电平变成低电平(下降沿)的时候,JK触发器就像是被施了魔法一样开始工作。

如果J 输入是高电平,K输入是低电平,那这个触发器就会被置成高电平状态,就好像它听到了J的召唤,然后说“那我就变成高电平啦”。

反之,如果J是低电平,K是高电平,它就会被置成低电平状态,就像很听话地按照输入的指示来改变自己的状态。

你看,这个JK边沿触发器是不是很有趣呢?它在很多数字电路的应用里都发挥着巨大的作用。

比如说在计数器里,它就像是一个小管家,一个一个地数着脉冲信号,靠的就是它这种对输入信号和时钟信号的巧妙处理。

还有在寄存器里,它能够准确地存储数据,就像一个小盒子,按照时钟信号的节奏把数据好好地保存起来。

而且哦,它的这种边沿触发的特性让它在处理信号的时候非常精确。

不像有些电路可能会对信号的整个电平变化过程都有反应,容易出现混乱,JK边沿触发器就只在时钟信号的边沿这一特定时刻做出反应,就像一个精准的小闹钟,到点了才响。

它就像是数字电路这个大家庭里的一个小精灵,虽然小小的,但是功能超级强大。

每一个逻辑门的组合,每一次对J、K输入和时钟信号的响应,都像是它在这个数字世界里独特的舞步。

它用自己独特的工作方式,为数字电路的正常运行和各种功能的实现默默贡献着自己的力量。

数字电子技术-主从RS触发器

1.电路结构 2、工作原理

第二节、 JK触发器

Q Q

(a)当CP=1时,主触发器工作,接收

G1 & G3 & Q' G5 & G7 &

&

G2 G4

输入信号。从触发器被封锁,保持原状

态不变:

& Q' &

(b)当CP由1跃变到0时,即CP=0、

CP’=1。主触发器被封锁,输入信号

G6 1

G9

不再影响主触发器的状态;从触发器

(1) RS触发器 (2) JK触发器 5 .同一电路结构的触发器可以做成不同的逻辑功能;同一逻辑功能的触 发器可以用不同的电路结构来实现。 6.利用特性方程可实现不同功能触发器间逻辑功能的相互转换。

VOC

DC

330ΩBiblioteka + Vcc +5V

利用触发器的“记忆”作用,使抢答电路工作更可靠、稳 定。

QA KA FFA Q S R KR GA & VOA DA 330Ω

R

R QB Q S R

GB &

VOB

DB

330Ω

KB

FFB

R

R QC

GC &

VOC

DC

330Ω

KC

FFC

Q S R

R

R

7、本课小结

1.触发器有两个基本性质:(1)在一定条件下,触发器可维持在两种稳 定状态(0或1状态)之一而保持不变;(2)在一定的外加信号作用下, 触发器可从一个稳定状态转变到另一个稳定状态。 2 .描写触发器逻辑功能的方法主要有特性表、特性方程、驱动表、状态 转换图和波形图(又称时序图)等。 3.按照结构不同,触发器可分为: (1) 基本RS触发器,为电平触发方式。 (2) 同步触发器,为脉冲触发方式。 (3) 主从触发器,为脉冲触发方式。 (4) 边沿触发器,为边沿触发方式。 4.根据逻辑功能的不同,触发器可分为:

RS JK触发器

使用时有约束条件

从

触

RS=0

发

器

为此,将触发器

的两个互补的输出

端信号通过两根反

主

馈线分别引到输入

触

端的G7、G8门,这 样,就构成了JK触

发 器

发器。

从从 触触G1GG1&1

&&

发发

器器

G3GG3&3 &&

Q'QQ''

主主 G5GG5&5 && 触触 发发 器器G7GG7&7 &&

& && G2GG22

(3)波形分析

例4.1.1 在用与非门组成的基本RS触发器中,设初始状态为0,已

知输入R、S的波形图,画出两输出端的波形图。 Q n1 S RQ n RS 0 (约束条件)

R

1 1 1 1 1 0 1 0 11

S

1 0 1 0 1 1 1 1 11

Q Q

基本触发器的特点总结:

(1)具有直接置1、置0 、 保持功能。 (2)与非门组成的基本RS触发器中,触发信号

Q

Q

1R C1 1S CP

R

CP

S

有效翻转

空翻

由于在CP=1期间,G3,G4门都是开着的,都能接收R、S信号,所以,如果在 CP=1期间R、S发生多次变化,则触发器的状态也可能发生多次翻转。

在一个时钟脉冲周期中,触发器发生多次翻转的现象叫做空翻。

三. 主从RS触发器

1.电路结构

Q

从 触

G1 &

由两级同步RS触发器串联

入信号;从触发器保持。

触发器的电路结构和工作原理

主锁存器维持原态不变。

TG3导通,TG4断开——从锁存器Q的信号送Q端。

触发器的状态仅仅取决于CP信号上升沿到达前瞬间的D信号

14

3. 典型集成电路

74HC/HCT74 中D触发器的逻辑图

D1 1

C 。 TG1 ≥1 TG

G1 C TG2

C TG3 ≥1

TG G3

C TG4

1Q 1Q

C C TG C

C TG C

C

1C

P

RD 1

≥1 G2

≥1 G4

SD 1

15

74HC/HCT74的逻辑符号和功能表

74HC/HCT74的功能表

1S S 1DC C1

1Q

P1D 1D 1R R

1Q

D2S S

2Q

2DC C2

P2D 2D 2R R

2Q

D

国标逻辑符号

输入

输出

S D R D CP D Q

Q

L H× × H L

40

小结

锁存器和触发器都是具有存储功能的逻辑电路,是构成 时序电路的基本逻辑单元。每个锁存器或触发器都能存储1位 二值信息。

锁存器是对脉冲电平敏感的电路,它们在一定电平作用 下改变状态。

触发器是对时钟脉冲边沿敏感的电路,它们在时钟脉冲 的上升沿或下降沿作用下改变状态。

触发器按逻辑功能分类有D触发器、JK触发器、T(T') 触发器和SR触发器。它们的功能可用特性表、特性方程和状 态图来描述。触发器的电路结构与逻辑功能没有必然联系。

典型集成电路74hchct74中d触发器的逻辑图74hchct74的功能表国标逻辑符号74hchct74的逻辑符号和功能表具有直接置1直接置0正边沿触发的d功能触发器532维持阻塞触发器置0维持线响应输入d和cp信号根据确定触发器的状态在cp脉冲的上升沿触法器按此前的d信号刷新当cp在cp脉冲的上升沿到来瞬间使触发器的状态变化d信号不影响534触发器的动态特性动态特性反映其触发器对输入信号和时钟信号间的时间要求以及输出状态对时钟信号响应的延迟时间

边沿JK触发器工作原理及动作特点

边沿JK触发器工作原理及动作特点

主从触发器可以有效克服钟控触发器的空翻现象,但主从触发器还存在一次翻转现象,降低了抗干扰能力。

边沿触发器:只有在CP的上升沿(前沿)或下降沿(后沿)时刻才对输入信号响应(不管CP=1的时间有多长)。

在CP=0、CP=1期间,输入信号变化不会引起触发器状态的变化。

因此触发器不但克服了空翻现象,而且大大的提高了抗干扰能力,工作更为可靠。

边沿JK触发器

边沿JK触发器不仅可以克服电位触发方式的多次翻转现象,而且仅仅在时钟脉冲CLK的上升沿或下降沿才对激励信号相应,如此可大大提高了抗干扰能力。

边沿JK触发器工作原理

边沿JK触发器的特点

①边沿触发,无一次变化问题。

②功能齐全,使用方便灵活。

③抗干扰能力极强,工作速度很高。

14.JK触发器

CP J K Q Q

课堂导入

新课教学

动手实践

课堂小结

二、工作原理

JK触发器状态表

CP 1 1 1 1 J 0 0 1 1 K 0 1 0 1 Qn+1 Qn 0 1 Qn 功能 保持 置0 置1 翻转(计数)

(1) 当J=0,K=1时,Qn+1=JQn+KQn , 置“0”。 (2) 当J=1, K=0时, Qn+1 =JQn+KQn ,置“1”。

课堂导入

新课教学

动手实践

课堂小结

电路组成

JK触发器

波形测量

工作原理JK触发器来自D触发器课堂导入

新课教学

动手实践

课堂小结

一、电路组成

Q Q & & SD R & & K K CP (a ) J (b ) S Q RD CP Q SD

SD

J

逻辑电路 图4.8(a)

逻辑符号

课堂导入

新课教学

动手实践

课堂小结

一、电路组成

课堂导入

新课教学

动手实践

课堂小结

动一动

同学们两人为一小组,根据JK触发器电路图和输入

课堂导入

新课教学

动手实践

课堂小结

课堂导入

新课教学

动手实践

课堂小结

在观看电视里的竞赛节目时,我们经常能 看到抢答器,只要一按下开关,屏幕就会有相 应的显示。

课堂导入

新课教学

动手实践

课堂小结

触发器是具有记忆功能的单元电路,由门电路 构成,专门用来接收存储输出0、1代码。 触发器

基本RS触发器

同步RS触发器

电工电子技术基础知识点详解1-4-2-主从JK触发器

1

主从型JK触发器

功能分析 (J=1 K=0)

J=1 CP=1

K=0

1 S=0 1 R=0 0

1

触发器的初始状态为1 Q=1

主从型JK触发器

功能分析 (J=1 K=0)

J=1

1 S=0 1

Q=1

CP=0 K=0

R=0 0 1

1

主从型JK触发器

逻辑状态表

主从型JK触发器是一种边沿型触发器

主从型JK触发器

R=0

R=0

1

触发器的初始状态为0 Q=0

主从型JK触发器

功能分析 (J=1 K=1)

J=1

1

Q=1

S=1

S=1

CP=0 K=1

R=0

R=0 1

1

主从型JK触发器

功能分析 (J=0 K=0)

J=0

1

S=0

CP=1

K=0

R=0 1

触发器的初始状态为 K=0)

主从型JK触发器

主从型JK触发器

主触发器

主从型JK触发器

从触发器

主从型JK触发器

S JQ

R = KQ

时钟脉冲

主从型JK触发器

功能分析 (J=1 K=1)

J=1

1

S=1

CP=0

K=1

R=0 1

触发器的初始状态为0 Q=0

主从型JK触发器

功能分析 (J=1 K=1)

J=1 CP=1

K=1

1 S=1 Q=1 S=1

逻辑符号

输入为 J 端和 K 端,脉冲时钟 CP ,由于是下降沿触发,在 CP端画个小圆圈。

主从型JK触发器

已知CP脉冲是一个连续脉冲,J信号和K信号的输入波形已 给出。画出主触JK发器输出 Q 的波形。初始状态为0.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主从jk触发器工作原理

主从JK触发器工作原理是指在数字电路中,使用JK触发器来实现主从工作方式。

这种工作方式可以用来存储、延时和同步数据。

主从JK触发器由两个触发器组成,一个被称为主触发器,另一个被称为从触发器。

主触发器用于接收输入信号,从触发器用于输出信号。

主从JK触发器的工作原理如下:

1. 当时钟输入为高电平时,主触发器的状态开始变化。

主触发器的状态取决于JK输入端的状态。

如果J和K都为低电平,则主触发器的输出保持不变。

如果J 为低电平,而K为高电平,则主触发器的输出为高电平。

如果J为高电平,而K 为低电平,则主触发器的输出为低电平。

如果J和K都为高电平,则主触发器的输出将翻转。

2. 主触发器的输出被连接到从触发器的输入端。

当时钟输入为下降沿时,从触发器的状态开始变化。

从触发器的状态取决于主触发器的输出。

如果主触发器的输出为低电平,则从触发器的输出将保持不变。

如果主触发器的输出为高电平,则从触发器的输出将翻转。

通过这种方式,主从JK触发器可以实现数据的存储和同步。

主触发器接收输入信号,并根据输入信号的状态改变自己的状态。

然后,主触发器的状态通过从触发器传递,从而延时输出信号。

因为主从JK触发器具有存储功能,所以它通常用于时序电路和状态机等应用中。

总结起来,主从JK触发器通过主触发器和从触发器的组合来实现数据存储和同步功能。

它的工作原理是根据触发器输入端的状态和时钟信号的变化来改变触发器的输出状态。

这种触发器在数字电路设计中起着重要的作用。