基于ADS三阶电荷泵锁相环的分析和仿真

基于ADS三阶电荷泵锁相环的分析和仿真

求得滤波器的电

容 和 电 阻 参 数 如 下 : C1=

Cto·t ττ12 ,

C2

=Ctot-

C1,

R2=

τ2 C2

其 中 , Ctot

=

" C1τ2 τ1

=

kvΙcp 2πωc2N

1+( ωcτ2) 2 1+( ωcτ1) 2

5 参数确定和仿真结果

我们的目标是设计一个三阶电荷泵锁相环, 输入参考频率

本栏目责任编辑: 谢媛媛

开发研究与设计技术

基于 ADS 三阶电荷泵锁相环的分析和仿真

张明, 吴秀龙, 张兴建, 王诗兵 ( 安徽大学电子科学与技术学院, 安徽 合肥 230039)

摘要: 在分析锁相环基本原理和线性化模型的基础上, 给出了基于锁相环系统环路带宽和相位裕度的环路滤波器参数的计算公式。 结合具体的参数计算,给出系统参数, 然后用 ADS 工具对系统进行仿真, 结果 表 明 利 用 给 出 的 方 法 来 设 定 锁 相 环 的 参 数 , 通 过 反 复 几 次 的调节能得到一组很好的系统参数, 仿真结果于预期的相吻合, 对三阶电荷泵锁相环的系统设计和仿真有一定的指导意义。

fref=2MHZ 、VCO 的 灵 敏 度 kv=3.3MHZ/V、 输 出 的 目 标 频 率 参 数 fvout=8MHZ、电 荷 泵 电 流 Icp=100uA、环 路 带 宽 fc=100KHZ , 相 位 裕 度 Φ=60°。通过自己编写的 MATLAB 程序计算出满足上述条件的

滤 波 器 的 参 数 , 结 果 见 表 1,锁 相 环 的 开 环 、闭 环 传 递 函 数 的 波 特

2 锁相环的基本原理和线性化模型

一 个 基 本 的 电 荷 泵 锁 相 环 由 鉴 频 鉴 相 器 ( PFD) 、 电 荷 泵 ( CP) 、低通滤波器( LPF) 和压控振荡器( VCO) 组成。系统示意图如 图 1, 其中 N 是分频器的分频比。

毕业论文-CMOS电荷泵锁相环的研究与设计

CMOS电荷泵锁相环的研究与设计摘要锁相环设计是现代集成电路设计中一个重要的话题,在射频无线通信、高速有线通信、光纤通信以及高性能数字电路等领域中占有重要的地位。

电荷泵锁相环是锁相环应用中最广泛的一种,因为它具有易集成、低功耗、低抖动、低噪声、捕获范围宽等特点。

因此电荷泵锁相环成为IC领域研究中的热点。

本论文首先介绍了锁相环的背景与现状,分析了一般锁相环的组成结构与基本原理并逐步引出电荷泵锁相环,研究了锁相环的非理想特性,并推导了部分组成部分的参数,最终得到锁相环的数理模型。

在此基础上,设计了一个工作在10MHz~100MHz的电荷泵锁相环,包括鉴频鉴相器、电荷泵、环路滤波器、压控振荡器以及分频器电路模块。

本文鉴相器是由两个RS触发器与一些非门、与非门构成,具有较大的鉴相灵敏度、较小的纹波输出、工作线性区域大和零点漂移小的特点。

电荷泵采用全差分设计,使用了镜像电流源,这样就使电荷泵受温度影响大大减小,同时也稳定了电流的输入。

低通滤波器使用无源二阶滤波器,既降低了制造成本,又避免了极点的产生,提高了电路的稳定性。

本实验的锁相环使用的是电荷泵锁相环基于CSMC0.6um标准CMOS工艺。

仿真结果要求锁相环在5V电源电压下可以在5MHz~120MHz的频率范围内正常工作,占空比为50%±3%,锁定时间小于8μs。

经仿真试验,本设计达到了课题的要求。

关键词:锁相环;鉴频鉴相器;电荷泵;压控振荡器;COMSAbstractPLL design is a modern integrated circuit design is an important topic, occupies an important position in the field of radio frequency wireless communications, high-speed wired communications, optical communications, and high-performance digital circuits and the like . CPPLL is locked loop applications, the most widely used , because it has easy integration, low-power, low-jitter , low -noise , wide capture range of features. Thus IC CPPLL become a hot research field .This paper introduces the background and status of the PLL , followed by analysis of the structure and composition of the basic principles of the general phase-locked loop and gradually leads CPPLL study the non-ideal characteristics of the PLL and derive some parameter components , and ultimately get the PLL mathematical models. On this basis , the design of a work in 10MHz ~ 100MHz charge pump PLL, including phase frequency detector, charge pump , loop filter , VCO and divider circuit modules.This article is some phase NAND gate NAND gate consists of two RS flip-flop having a phase sensitivity of the larger , the smaller the output ripple , and the work of the linear region of the large zero drift characteristics. A fully differential charge pump design, a current mirror , so that the charge pump is reduced greatly affected by temperature , but also the stability of the input current. Second-order low-pass filter using passive filters , not only reduces manufacturing costs, and avoid the extreme generation, but also allows the circuit is very stable.In this study, using a phase-locked loop based TSMC0.35um CPPLL standard CMOS process . The simulation results require phase-locked loop can operate at 3.3V supply voltage in the frequency range of 5MHz ~ 120MHz normal duty cycle of 50% ± 3%, the lock time is less than 8μs. The simulation test, the design meets the requirements of the subject .Key words: low voltage; Low power; CMOS operational amplifier; Rail to rail input目录摘要 (I)Abstract (II)第一章绪论 (5)1.1 锁相环的背景 (5)1.2 锁相环的发展、现状和应用 (5)1.3 论文的章节安排 (7)第二章 CMOS电荷泵锁相环的基本原理及组成 (8)2.1 电荷泵锁相环的基本原理 (8)2.2 CMOS电荷泵锁相环的基本组成 (9)2.2.1 鉴频鉴相器 (9)2.2.2 电荷泵 (10)2.2.3 延时电路 (11)2.2.4 环路滤波器 (12)2.2.5 PFD/CP的非理想效应 (13)2.2.6 压控振荡器 (17)2.2.7 分频器 (17)2.2.8 锁相环的基本性能 (17)2.3 电荷泵锁相环的相位噪声 (18)2.4 本章小结 (19)第三章电荷泵锁相环电路的设计 (20)3.1 电荷泵锁相环电路简介 (20)3.2鉴频鉴相器电路设计与仿真 (20)3.2.1 鉴频鉴相器的 (20)3.2.2仿真波形 (23)3.3 电荷泵和滤波器的设计和仿真 (24)3.3.1电荷泵的设计 (24)3.3.2 环路滤波器的结构 (26)3.3.3 电荷泵和滤波器的仿真 (29)3.4 环路整体仿真 (30)3.5 小节 (31)第四章结论 (32)参考文献 (32)致谢 (33)第一章绪论1.1 锁相环的背景锁相环电路(PLL)是一个能够跟踪输入信号相位的闭环自动控制系统。

跳频系统中电荷泵锁相环的事件驱动仿真

跳频系统中电荷泵锁相环的事件驱动仿真

苏彦锋;王涛;衣晓峰;洪志良

【期刊名称】《系统工程与电子技术》

【年(卷),期】2003(025)008

【摘要】为了快速仿真单片集成跳频系统中的电荷泵锁相环,在比较几种常见仿真方法的基础上,重点介绍了电荷泵锁相环的事件驱动模型,并针对这种模型的具体实现提出了一些改进.改进后的模型主要应用于跳频系统中频率合成锁相环的稳定性和建立时间的快速仿真.讨论了电荷泵锁相环事件驱动模型中的近似问题和这种模型同其它模型之间的联系.

【总页数】4页(P925-927,945)

【作者】苏彦锋;王涛;衣晓峰;洪志良

【作者单位】复旦大学微电子学系,上海,200433;复旦大学微电子学系,上

海,200433;复旦大学微电子学系,上海,200433;复旦大学微电子学系,上海,200433【正文语种】中文

【中图分类】TN911

【相关文献】

1.水声信道中跳频通信系统设计与仿真 [J], 岳玲;钱建平;王明洲

2.跳频码分多址系统中混沌跳频序列的优选与仿真 [J], 张琪;郑君里;刘栩

3.三阶电荷泵锁相环系统级设计与仿真验证 [J], 陈文焕;叶星宁

4.电荷泵锁相环的事件驱动建模与仿真 [J], 赵赛果;李巍;王子立

5.跳频锁相环路暂态响应对系统性能的影响 [J], 郑光永

因版权原因,仅展示原文概要,查看原文内容请购买。

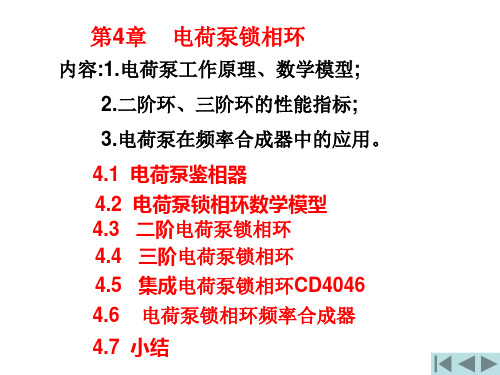

电荷泵锁相环..

环路传递函数

F(s)=(1+τ 2s)/τ 1s

(4.3.4)

可得此环路的数学模型,如图4.3.2和图4.3.3(复频域) 所示。

θi(s)

+ -

+

θe(s)

ud(s)

Kd

1 2s 1 s

uc(s)

Ko/s

θo(s)

图4.3.2 二阶电荷泵PLL的相位模型 △ω i(s) △ω (s) + K’d + - ud(s) 1 2 s uc(t)

4.1 电荷泵锁相环(CPPL) 电荷泵锁相环如图4.1.1所示。

ui(t) FPD CP LF VCO uo(t)

图4.1.1

电荷泵锁相环

图中: FPD是鉴频鉴相器;

CP是电荷泵;

是模数混合环,与模拟锁相环唯一不同的是鉴相器包 括FPD和CP,称为电荷泵鉴相器。它是数字式的,具有 鉴频鉴相功能,CP为LF提供充放电电荷。 为简化分析过程,以图4.1.2所示的双D鉴相器为例, 来说明鉴频鉴相器的工作原理。

设电荷泵能提供的充放电电流为Ip,则充放电电流在一 个周期内的平均值为: id(t)=Ipθe(t)/2π

e (t ) 2

(4.1.1)

上式即为这种电荷泵鉴相器的鉴相特性。考虑到相位 的周期性,式(4.1.1)所表示的鉴相特性可用图4.1.4表 id(t) 示。

I

-4π

-2π

P

0 -IP

2π

o (t )

o c

p

(4.2.2)

V (t ) K ouc (t )

(4.2.3)

综合考虑(4.1.1) ~(4.1.4)式及(4.2.1)~(4.2.3), 可得环路的相位模型和频率模型分别如图4.2.2和 4.2.3所示。

基于电荷泵锁相环的有源环路滤波器的设计

基于电荷泵锁相环的有源环路滤波器的设计刘健余【摘要】Loop filter is a key module of the phase-locked loop,it often uses active filter to tune the broadband high-voltage VCO.The paper discusses the basic principles of charge-pump phase-locked loop,then analyzes the structure of the active loop filter and the effects of filter to PLL performance,and derivates the design methods of an active loop filter parameters.The third-order active loop filter is designed according to the subject,and simulated the phase-locked loop system performance using ADS tools,the results coincide with the theory.The experimental results show that the designed filter can satisfy the requirements of the subject,and verify the correctness of this method.%环路滤波器是锁相环中的一个关键模块,对宽带高压VCO进行调谐时,常采用有源滤波器。

在论述了电荷泵锁相环基本原理的基础上,对有源环路滤波器的结构以及滤波器对锁相环性能的影响进行了分析,推导出有源环路滤波器参数的设计方法。

锁相技术第5章 电荷泵锁相环

3

5.1 电荷泵鉴频鉴相器数学模型

电流型电荷泵鉴频鉴相器

“1”

DQ

UP

FF

u1

s 1

s

2

C1

(

s

b

1

1)

Ho(

j)

KVCO I 2

p

(b) b 1

(

j 1

j

)

2

C1

(

j b 1

1)

Ho(

j)

KVCO I p 2

b

1 ( )2

()

b 1 2C1

1 ( j )2 b 1

Ho ( j) 1 c 为环路带宽(也称穿越频率),此时相角位移为:

号的信道噪声; 环路内部噪声:PLL内部各模块产生的噪声,如鉴相器

和压控振荡器等部件。

若环路用作频率信号源,噪声与干扰会使输出信号频谱不 纯,输出相位产生随机的抖动,频率稳定度变差;若环路 用作通信的收发射机,则输出信噪比下降。较强的噪声与 干扰还会使环路跟踪性能下降,失锁。同时,必然会增加 环路捕获困难。

周期抖动(period jitter)一般有两种表示值: Peak-to-Peak值(峰-峰值):在第N个周期的上升沿

可能出现的最大偏移值。 RMS值(均方根值):指第N个周期上升沿相位变化的

标准方差。

24

周期抖动(period jitter)

在周期抖动(period jitter)的测量中: 如果N<10,那么周期抖动(period jitter)称为

《【锁相环中电荷泵的研究】电荷泵锁相环》

《【锁相环中电荷泵的研究】电荷泵锁相环》[摘要]锁相环的运用已经越来越广泛,从时钟产生器到无线通信到有线通信,光通信等等。

在实际应用中,很多工程师都倾向于使用电荷泵型锁相环。

因为它更容易实现尽可能大的或者无限开环增益。

这样,电荷泵在该种结构中将充当非常重要的角色,其中的不理想性将会对整个系统的性能,比如时钟抖动,相位噪声,锁定时间,带宽,功耗等的设计带来挑战。

本文将就以上问题进行详细的分析和研究。

最后本文提出了一种改善性能的增益提高技术电荷泵。

[关键词]锁相环电荷泵相位噪声抖动[中图分类号]tn4[文献标识码]a[文章编号]1007-9416(xx)03-0127-02引言基于电荷泵型的锁相环已经被广泛采用与无线通信系统中,特别是射频收发机的频率综合器中。

随着无线通信不断地发展,通信系统对终端的要求不断地提高,诸如集成度,功耗,噪声等等。

而在无线收发机中,频率综合器是一个非常关键的部分,它的性能将影响整个系统是否能够正常工作。

作为基于电荷泵的频率综合器,电荷泵在其中起着非常关键的作用。

本文接下来几个部分将对电荷泵做一详细全面的研究。

1设计中的不理想性一般的电荷泵型锁相环如图1所示[1]。

理想情况下,电荷泵和鉴频鉴相器为系统提供了无限的直流增益,于是输入和输出的相位差为0。

但是,作为电荷泵,其本身存在很多固有的不理想性,致使实际的频率综合器会有很多不理想效应产生,从而导致性能的降低。

因此,下面将对其中重要的不理想效应进行研究和分析。

1.1漏电流漏电流是电荷泵固有的不理想性,或者说是和完全和工艺相关的。

随着工艺的不断改进,特别是深亚微米级的cmos工艺,漏电流的问题变得越来越严重。

因为漏电流而导致的相位失配相对来说问题不大,但是由此而产生的参考毛刺在频率综合器中是值得特别注意的。

由于漏电流造成的相位失配可以有下式得出[2],其中是相位失配,是漏电流大小,表示电荷泵的电流大小。

由于相位失配所导致的边带,也就是参考毛刺的大小为:其中,为环路滤波器的极点,是环路滤波器的电阻值,是压控振荡器的增益。

电荷泵锁相环的模型研究和电路设计

结论

本次演示对电荷泵锁相环的模型研究和电路设计进行了详细探讨。通过建立 数学模型并简化分析,我们发现电荷泵锁相环的性能主要受到电荷泵增益、环路 滤波器时间常数以及输入信号频率的影响。在此基础上,我们设计了一款电荷泵 锁相环电路,并对关键元件进行了选择和优化。然而,该电路仍存在一些不足之 处,需要进一步改进。

2、低功耗:该设计方案采用了先进的工艺和电路设计,使得芯片的功耗较 低,延长了设备的使用寿命。

3、高集成度:所设计的锁相环集成电路芯片具有高集成度,减小了设备的 体积和重量,方便了实际应用。

结论:

本次演示通过对高速锁相环集成电路芯片的深入研究和实验验证,提出了一 种针对高速条件下的高效设计方案。实验结果表明,所设计的芯片在高速条件下 具有良好的性能和可靠性。但是,我们也意识到该设计方案仍存在一些不足之处, 例如在复杂电磁环境下的稳定性等问题。

近年来,随着太阳能技术的快速发展,光伏并网逆变器在太阳能发电系统中 得到了广泛应用。三相锁相环设计在光伏并网逆变器控制中具有重要意义,是实 现并网稳定运行的关键技术之一。本次演示将阐述三相锁相环设计及光伏并网逆 变器控制的研究内容和方法。

在光伏并网逆变器控制领域,文献综述表明,现有的研究主要集中在逆变器 拓扑结构、控制策略和并网保护等方面。其中,三相锁相环设计是逆变器控制策 略中的重要组成部分。已有的三相锁相环设计方法主要包括基于PI调节器和基于 同步检测器的设计方法。然而,这些方法在实时性、准确性和稳定性方面仍存在 一定的问题,特别是在复杂环境和恶劣条件下。

模型研究

1、电荷泵锁相环的原理和内部 机制

电荷泵锁相环主要由电荷泵、环路滤波器(Loop Filter)和电压控制振荡 器(VCO)三个主要部分组成。其工作原理是,通过电荷泵将输入信号的相位差 转化为电压,再经环路滤波器滤除高频成分,得到控制VCO的直流电压,最终实 现输出信号与输入信号的相位和频率同步。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图分别见图 5、6。从图 5 可以看出环路带宽 100KHZ, 相位裕度为

60°。

表 1 参数计算结果

图 6 三阶电荷泵锁相环闭环波特图 图 7 VCO 的控制电压曲线

图 5 三阶电荷泵锁相环开环波特图 用 Agilent 公司的 ADS 软件做系统仿真, 在实际的仿真中, 把 VCO 的固有振荡频率设定在 , 图 7 为 VCO 控制电压 随 时 间 的 变 化 曲 线 , 开 始 出 现 了 振 荡 , 最 后 稳 定 的 电 压 约 为 0.6V , 也 可 以 看 出环路开始 锁 定 时 间 大 约 在 22(s。 图 8 为 锁 相 环 锁 定 后 输 入 信 号和 VCO 输出 信 号 的 波 形 图 , 可 以 看 出 VCO 的 输 出 频 率 为 输 入

491

开发研究与设计技术

本栏目责任编辑: 谢媛媛

在 45°- 60°环路稳定性较好。增益交点对应相位特性曲线的峰值, 我们说相位裕度达在增益交点达到最大, 可获得最大的相位裕度 , 环路的稳定性最佳。( 如图 4)

图 3 二阶无源环路滤波器

频率的 4 倍, 这也是锁相环在频率合成器中的一个方面的应用。

锁相环系统的整个锁定过程是个复杂的非线性过程, 对于二 阶以上的系统, 非线性微分方程的求解非常困难。当相位差很小 时, 我们可以把它近似为一个线性模型[3]。为了进一步的研 究 锁 相环的系统特性,我们给出它的线性模型。如图 2, 其中, κ是 VCO 的灵敏度, Icp 是电荷泵的泵出电流 , 在 单 片 集 成 锁 相 环 中 , 低 通 滤波器通常采用的是无源滤波器, 因为有源滤波器占用芯片面积 大, 容易引入了外界噪声。整个系统是个带二阶低通滤波器的三 阶 电 荷 泵 锁 相 环 , 系 统 的 开 环 传 递 函 数 H0(s) 和 闭 环 传 递 函 数 H (s) 。

图 8 基准输入频率和 VCO 输出频率

参考文献: [1]Razivi B.Design of analog COMS integrated circuit NewYork: MsGraw- Hill Inc,2001,532- 562. [2]Guan- Chyan Hsich,Jams C.Huang.Phase- Lockedloop Techn- iques - A Survey.IEEE TRANSACTION ON INDUSTRIAL ELECTRONICS.ELECTRONICS.VOL.43,NO.6,1996,609- 613. [3]Pavan Kumar Hanumolu.Analysis of Charge Pump Phase - Loc - ked Loops [M].IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS. VOL.51,NO.9,1665- 1667. [4]EM.Gardner,Charge - pump phase - lock loops,IEEE Trans. Commun.Vol.COM- 28,pp.1849- 1858,Nov 1980. [5]Paemel M.V.Analysis of a Charge Pump PLL a New Model. IEEE Transactions on Communications vol.42 no.7,July 1994.

求得滤波器的电

容 和 电 阻 参 数 如 下 : C1=

Cto·t ττ12 ,

C2

=Ctot-

C1,

R2=

τ2 C2

其 中 , Ctot

=

" C1τ2 τ1

=

kvΙcp 2πωc2N

1+( ωcτ2) 2 1+( ωcτ1) 2

5 参数确定和仿真结果

我们的目标是设计一个三阶电荷泵锁相环, 输入参考频率

本栏目责任编辑: 谢媛媛

开发研究与设计技术

基于 ADS 三阶电荷泵锁相环的分析和仿真

张明, 吴秀龙, 张兴建, 王诗兵 ( 安徽大学电子科学与技术学院, 安徽 合肥 230039)

摘要: 在分析锁相环基本原理和线性化模型的基础上, 给出了基于锁相环系统环路带宽和相位裕度的环路滤波器参数的计算公式。 结合具体的参数计算,给出系统参数, 然后用 ADS 工具对系统进行仿真, 结果 表 明 利 用 给 出 的 方 法 来 设 定 锁 相 环 的 参 数 , 通 过 反 复 几 次 的调节能得到一组很好的系统参数, 仿真结果于预期的相吻合, 对三阶电荷泵锁相环的系统设计和仿真有一定的指导意义。

关键词: 电荷泵; 锁相环; 低通滤波器; ADS 仿真 中图分类号: TN743 文献标识码: A 文章编号: 1009- 3044(2007)20- 40491- 02

Analys is and S imulation Three Order Charge P ump P has e Locked Loops Bas ed on ADS ZHANG Ming,WU Xiu- long,ZHANG Xing- jian,WANG Shi- bin

6 结论

电荷泵锁相环锁以其优越的性能被广泛的研究与应用, 本文 在分析电荷泵基本原理的基础上, 在保证最佳相位裕度和环路带 宽的条件下, 通过数学分析导出环路滤波器的参数。使用 Agilent 公司的 ADS 软件做了电荷泵的系统仿真, 达到了预期的结果。这 种方法同样适合高阶电荷泵锁相环的设计和分析, 对锁相环的系 统设计和仿真以一定的指导意义。

( 4) ( 5)

4 滤波器参数的确定

锁 相 环 中 滤 波 器[4]设 计 的 好 坏 关 系 到 锁 相 环 的 稳 定 性 和 捕 捉跟踪性能等的优劣, 优越的环路滤器参数不仅能减少环路捕 捉、锁定时间, 并能提高环路系统的稳定性能。一般认为相位裕度

收稿日期: 2007- 09- 03 基金项目: 安徽省教育厅自然科学研究重点项目( 2006kj012a) 作者简介: 张明( 1982- ) , 男, 安徽萧县人, 硕士研究生, 研究方向: 超大规模模拟集成电路设计。

492 电脑知识与技术

图 4 锁相环开环幅相特性曲线

由( 3) 式的相频特性得锁相环开环增益的相位裕: Φ( ω) PM=π+

arctan(ωτ2)- arctan(ωτ1),

!% !"

=0 得 ωc= 1

"="c

"τ1τ2

( 环路带宽) 。

则有,

τ1=

sec(ΦM)- tang(ΦM) ωc

,

τ2=

1 ωc2τ1

再结合 ( 4)

( 1) ( 2) 二阶无源低通滤波器的电路结构如图 3。

图 1 电荷泵锁相环的系统示意图

图 2 电荷泵锁相环频域模型 二阶低通滤波器的传递函数:

( 3) 其中, τ1=R2*[(C1*C2)/(C1+C2)], τ2=R2*C2,Ctot=C1+C2 把( 3) 分 别代入到( 1) , ( 2) 式中可得到锁相环的开环、闭环传递函数。

(Institute of Electronic Science and Technology, Anhui University, Hefei 230039,China) Abs tract: With the analysis of the fundamental of the third order charge pump phase locked loops, the formula of two order low pass filter is given on the based of phase margin and loop bandwidth of the CPLL, the formula is verified by the tool of ADS and MATLAB, The result indicates that set the parameter of CPPLL by the given method, A good group system parameter can be obtained by the several modifications, The simulation result meets the prospected data. Programming method will have certain significance in system level design and simulation of the CPPLL. Key words : charge pump;phase locked loops;low pass filter;ADS;simulation

1 引言

锁相环广泛应用于微处理器芯中的时钟发生 器 、硬 盘 驱 动 电 路模块、时钟恢复电路等以及便携式消费电子产品中 。 在 现 代 通 信系统中, 锁相环是收发机中的重要模块, 它和分频器一起产生 一系列稳定的频率点用作本振信号。近年来, 随着集成电路(IC)产 业的迅速发展和片上系统芯片(SoC)技术的日趋成熟, 单片集成锁 相环成为研究的热点, 采用电荷泵单元的的电荷泵锁相环 [1][2] (CPPLL)是 目 前 比 较 流 行 和 研 究 较 多 的 结 构 。

一个相位差 , 输出一个与相位差成正比的 电 压 脉 冲 信 号 μd , 其中 μd=κd( θ1- θ2) , κd (V/rad)为 鉴 频 鉴 相 器 的 增 益 。 鉴 频 鉴 相 器输出的 UP 和 DN 信号打开电荷泵开关, 并对后端的 电 容 充 放 电, 从电荷泵进入低通滤波器电路, 经二阶低通滤波器滤除高频 和 杂 波 信 号 产 生 一 个 比 较 稳 定 的 直 流 电 压 控 制 VCO 的 输 出 频 率 , VCO 的 输 出 频 率 经 分 频 器 降 频 后 返 回 鉴 频 鉴 相 的 输 入 端 , 与 参考信号的相位进行比较, 这就完成了一个循环过程。整个系统 是个相位负反馈系统, 系统在其可调节范围内系统可以自动的调 节, 使相位差逐渐向减小的方向变化, 最终相位差为零或维持在 一个固定的值, 从而 VCO 的输出稳定的频率。