电荷泵锁相环系统级功耗估计

基于CMOS工艺的电荷泵锁相环的设计的开题报告

基于CMOS工艺的电荷泵锁相环的设计的开题报告一、选题背景电荷泵锁相环(Charge Pump Phase-Locked Loop, CPPLL)是一种广泛应用于高速数据传输和数字通信领域的时钟同步电路。

CPPLL可以将参考时钟信号转换成锁定时钟信号,同时实现锁相输出和频率除法倍增功能。

因此,CPPLL在高速串行传输标准中被广泛使用,如USB、PCI Express和SATA等。

CMOS工艺是当今集成电路制造中最广泛采用的工艺,其制造成本低、可靠性高等优点使其成为了各种集成电路、微电子器件的主要工艺之一。

针对高速串行传输的应用,基于CMOS工艺的CPPLL设计具有成本低廉、性能高等优点,因此备受关注。

二、选题意义随着高速串行传输市场的不断扩大,对高速时钟同步电路的需求也不断增加。

CPPLL作为一种高速时钟同步电路,具有锁相输出和频率除法倍增等功能,广泛应用于高速串行传输标准中。

基于CMOS工艺的CPPLL设计不仅具有成本低廉的优势,而且可以实现集成化,因此在高速串行传输领域有着重要的应用价值。

三、研究内容及步骤本研究的主要内容为基于CMOS工艺的CPPLL设计,包括电荷泵、锁相环、倍频器等模块的设计。

研究步骤如下:1.研究CPPLL的基本原理和工作机理。

2.设计半导体工艺参数、电源电压等电路参数。

3.设计电荷泵电路,选择合适的电荷泵模型,并优化电荷泵性能参数。

4.设计PLL反馈环路,实现输入信号和输出信号的同步,并解决电路噪声干扰等问题。

5.设计倍频器模块,实现频率的倍增。

6.进行电路仿真和优化,将电路性能达到最佳。

7.进行电路实现和测试,验证电路的性能和可靠性。

四、预期成果本研究预期最终实现一个基于CMOS工艺的CPPLL电路,具有较高的工作性能和稳定性。

具体的预期成果如下:1.设计出符合高速串行传输标准要求的CPPLL电路。

2.优化电路性能,使其具有较高的输出频率和较低的相位噪声。

3.实现电路的自适应调整,提高电路的波动性能和稳定性。

《【锁相环中电荷泵的研究】电荷泵锁相环》

《【锁相环中电荷泵的研究】电荷泵锁相环》[摘要]锁相环的运用已经越来越广泛,从时钟产生器到无线通信到有线通信,光通信等等。

在实际应用中,很多工程师都倾向于使用电荷泵型锁相环。

因为它更容易实现尽可能大的或者无限开环增益。

这样,电荷泵在该种结构中将充当非常重要的角色,其中的不理想性将会对整个系统的性能,比如时钟抖动,相位噪声,锁定时间,带宽,功耗等的设计带来挑战。

本文将就以上问题进行详细的分析和研究。

最后本文提出了一种改善性能的增益提高技术电荷泵。

[关键词]锁相环电荷泵相位噪声抖动[中图分类号]tn4[文献标识码]a[文章编号]1007-9416(xx)03-0127-02引言基于电荷泵型的锁相环已经被广泛采用与无线通信系统中,特别是射频收发机的频率综合器中。

随着无线通信不断地发展,通信系统对终端的要求不断地提高,诸如集成度,功耗,噪声等等。

而在无线收发机中,频率综合器是一个非常关键的部分,它的性能将影响整个系统是否能够正常工作。

作为基于电荷泵的频率综合器,电荷泵在其中起着非常关键的作用。

本文接下来几个部分将对电荷泵做一详细全面的研究。

1设计中的不理想性一般的电荷泵型锁相环如图1所示[1]。

理想情况下,电荷泵和鉴频鉴相器为系统提供了无限的直流增益,于是输入和输出的相位差为0。

但是,作为电荷泵,其本身存在很多固有的不理想性,致使实际的频率综合器会有很多不理想效应产生,从而导致性能的降低。

因此,下面将对其中重要的不理想效应进行研究和分析。

1.1漏电流漏电流是电荷泵固有的不理想性,或者说是和完全和工艺相关的。

随着工艺的不断改进,特别是深亚微米级的cmos工艺,漏电流的问题变得越来越严重。

因为漏电流而导致的相位失配相对来说问题不大,但是由此而产生的参考毛刺在频率综合器中是值得特别注意的。

由于漏电流造成的相位失配可以有下式得出[2],其中是相位失配,是漏电流大小,表示电荷泵的电流大小。

由于相位失配所导致的边带,也就是参考毛刺的大小为:其中,为环路滤波器的极点,是环路滤波器的电阻值,是压控振荡器的增益。

锁相环中动态匹配电荷泵的分析与设计

r n e fo 0 3 o 1 3 ,c r e tmima c sl s h n 0 5 a g r m . 3 t . 4 V u r n s th i e s t a . 5

a d c r e td v a in i ls h n 0 4 . n u r n e i t e s t a . 5 o s

嘲

EE RN电 子S EET术CNLG L TOI MA RMN OOY C C E测 量技 T H U E

第 3 5 20 月 0 3年 5 1 期 卷第

锁 相 环 中动 态 匹 配 电荷 泵 的 分 析 与 设 计 *

赵 茂 何 书专1 潘 红兵 , 2 ,

( . 苏省 光 电信 息 功 能 材 料 重 点 实验 室 南京 2 0 9 ;2 南 京 大 学 微 电子 设 计 研 究 所 南京 2 0 9 ) 1江 103 . 1 0 3

0 1 m工 艺 , .8 静态 匹配 仿 真 结 果 表 明 输 出 电压 在 0 1 ~1 5 时 , 流 失 配 低 于 1 7 , 0 2 ~ 1 4 时 , 流 . 1 . 1V 电 . 在 . 1 . 6V 电 失 配 低 于 0 1 ; 态 匹配 的 后 仿 真 结 果 表 明输 出 电压 在 0 3 ~ 1 3 时 , . 动 . 3 . 4V 电流 失 配 低 于 0 5 , 移 低 于 04 。 .5 漂 .5

c r n im a c s ls ha . ur e tm s t h i e st n 1 7 ad0 n .1 o rt la a ve hevo tge r ngef o r m 0.1 t 1 51 1 o . V nd fom .21 o 1, 6 a r 0 t 4 V

CMOS电荷泵锁相环的研究与设计的开题报告

CMOS电荷泵锁相环的研究与设计的开题报告一、选题背景随着信息技术的迅猛发展,锁相环(PLL)已经成为了其中一个关键的技术,并广泛应用于通信、测量、控制等许多领域。

锁相环是一种基于反馈控制的电路,具有频率稳定、相位稳定等优点,能够对输入信号进行频率合成、频率分割、时钟恢复等操作。

在锁相环中,电荷泵是其中一个重要的模块,其作用是将相位比较器的输出相位误差转化成电荷泵电流,从而实现同步振荡。

随着制程技术的发展,CMOS工艺已经成为了最为常用的集成电路制造工艺,因此CMOS电荷泵的研究和设计也变得尤为重要。

二、研究目的本文的研究目的是通过对CMOS电荷泵锁相环的研究和设计,实现高性能、低功耗、小面积的电路设计,并探究其在PLL中的应用。

三、研究内容1. CMOS电荷泵的基本结构及工作原理。

2. PLL的基本原理及其各模块的设计(比如:相位比较器、环路滤波器、VCO等)。

3. CMOS电荷泵的设计方法和设计流程,包括各个环节的参数设计和优化。

4. CMOS电荷泵的性能参数分析与优化。

5. 最后,进行仿真验证,通过比较实验结果,评价该CMOS电荷泵的性能,验证其在PLL中应用的可行性。

四、研究意义本研究对于进一步推进锁相环技术的发展,促进了CMOS电路设计的研究和应用,提高了电路的性能指标以及系统的可靠性和稳定性,具有重要的理论和实际意义。

五、研究方法1.阅读相关的文献,对CMOS电荷泵、PLL等相关知识进行深入学习。

2.在了解了电路的工作原理后,根据其原理分析其关键性能参数,对传输线、晶体管、电容等元件进行参数设计和优化。

3.使用Cadence等相关软件进行电路仿真,评估各个模块的性能,寻找最佳设计方案。

4.使用TSMC0.18um CMOS工艺,进行电路的物理设计和版图布图。

5.最后,通过实验验证电路的性能指标,检验其在PLL中的应用效果。

六、预期成果1.完成CMOS电荷泵锁相环的设计,实现低功耗、高性能、小面积的电路结构。

一种应用于CMOS锁相环的电荷泵设计

一种应用于CMOS锁相环的电荷泵设计简元凯;解光军;毛佳佳【摘要】电荷泵是CMOS锁相环中的一个重要模块,其性能决定了整个锁相环系统的工作稳定性和各项指标的优劣.针对传统结构电荷泵存在的电荷共享、电流失配等问题,文章设计了一个基准电压源的电荷泵电路,外接一个2pF的负载电容,用于将电流转化为电压.该电路基于SMIC0.13μmCMOS工艺库,使用Cadence完成整体电路的仿真.仿真结果表明,该CMOS电荷泵具有输出电压平滑、充放电电流匹配等优良特性,很好地抑制了电荷共享、电流失配等寄生效应.该电荷泵应用在锁相环中,能实现快速锁定.%10.3969/j.issn.1003-5060.2012.11.016【期刊名称】《合肥工业大学学报(自然科学版)》【年(卷),期】2012(000)011【总页数】4页(P1506-1509)【关键词】电荷泵;电荷共享;电流失配;锁相环;锁定时间;电路仿真【作者】简元凯;解光军;毛佳佳【作者单位】合肥工业大学电子科学与应用物理学院,安徽合肥 230009;合肥工业大学电子科学与应用物理学院,安徽合肥 230009;合肥工业大学电子科学与应用物理学院,安徽合肥 230009【正文语种】中文【中图分类】TN432锁相环(Phase-Locking Loop)在电子学、通信领域中有着广泛的应用,一般用在相位锁定、频率合成以及时钟恢复电路中。

随着人们对CMOS工艺研究的不断深入,器件的特征尺寸不断缩小,因而高速度、高频率和低功耗已成为锁相环电路的发展方向。

一个基本CMOS电荷泵锁相环主要包括鉴频鉴相器(PFD)、电荷泵(CP)、低通滤波器(LPF)和压控振荡器(VCO)[1]。

电荷泵是CMOS锁相环中的重要模块,其作用是把PFD输出的数字信号转化为电压信号,以控制压控振荡器(VCO)的振荡频率。

在锁相环实现过程中,通常会遇到电荷共享、电流失配、电荷注入以及时钟馈通等问题。

超高频RFID阅读器电荷泵锁相环设计

超高频RFID阅读器电荷泵锁相环设计锁相环是在模拟/数字电路设计中的一种非常重要和实用的电路结构[1]。

锁相环[2-3]由鉴频鉴相器、电荷泵、滤波器、压控振荡器以及分频器等构成,在具体电路设计中还可能涉及到基准(PTAT)电路和一些简单的数字电路。

由于锁相环正常工作时能通过内部电路中精准的负反馈机制提供稳定的输出频率作为本振信号,因此,该结构广泛应用于数字及模拟电路设计之中。

1 电荷泵锁相环电路设计1.1 电荷泵锁相环原理与整体结构图1所示为电荷泵锁相环[4]的系统结构图。

620)this.style.width=620;" border=0 alt=超高频RFID阅读器电荷泵锁相环设计src="技术2021/ddk0lludrsi2021.gif"> 锁相环系统的基本原理为:最初外部参考信号与分频器输出信号同时输入给系统,送入鉴频鉴相器;鉴频鉴相器检测ωout与ωin两路信号的相位差和频率差以及上升沿和下降沿,并随时根据它们的上升、下降变化决定电荷泵的开启和关断状态;电荷泵的输出电压Ud经过滤波器滤波,产生输出电压Vctrl,Vctrl作用在压控振荡器上,产生输出频率;压控振荡器的作用是使输出频率随输入控制电压的变化按照一定比例变化,分频比为N的分频器保证:fvco=fref×N,其中fvco为VCO的输出频率,fref为参考频率。

锁相环内部负反馈机制使整个系统达到锁定状态。

620)this.style.width=620;" border=0 alt=超高频RFID阅读器电荷泵锁相环设计src="技术2021/5ojmqpg2zol2021.gif"> 出信号被送入鉴频鉴相器,初始相位差使环路无法锁定,经过一段时间的相位积累就能达到频率捕获。

针对死区问题,本设计所采用的去死区的方法是增加延时单元,延时单元应用串联连接的反相器链。

第4章 电荷泵锁相环

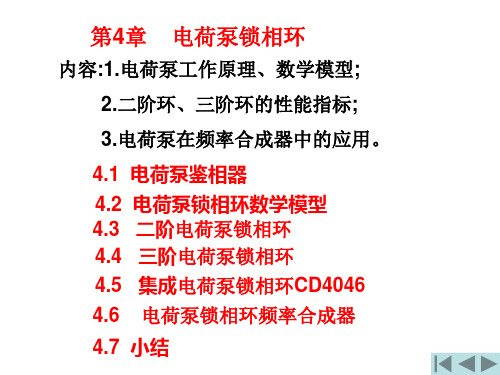

设电荷泵能提供的充放电电流为Ip,则充放电电流在一 个周期内的平均值为: id(t)=Ipθe(t)/2π

e (t ) 2

(4.1.1)

上式即为这种电荷泵鉴相器的鉴相特性。考虑到相位 的周期性,式(4.1.1)所表示的鉴相特性可用图4.1.4表 id(t) 示。

I

-4π

-2π

P

0 -IP

2π

Ko/s

θo(s)

图4.3.2 二阶电荷泵PLL的相位模型

图4.1.8 ωr固定时电流型鉴相器的鉴频特性

由此可得到它的鉴频特性为:

id (t )

r

IP

(t )

(t ) r

(4.1.2)

由上式(4.1.1)及(4.1.2),

id (t )

Ip 2

(t ) e (t ) 2

(4.1.3) (4.1.4)

(4.1.1)

可得电流型鉴相器的鉴相增益及鉴频增益分别为: 鉴相增益: KdI=IP/2π 鉴频增益: K’dI=IP/ωr

C1

(4.3.1)

图4.3.1 电流型 二阶环的环路滤 波器

Vc (s) 1 2 S Z F ( s) R2 I d ( s) 1S

(4.3.1)

式中τ1=τ2=R2C1。为了得到与模拟环相似的数学模 型,将R2与KdI、K’dI合并,令: 鉴相增益 Kd=IpR2/(2π) 鉴频增益 K’d=IpR2/ω r (4.3.2) (4.3.3)

这样就得到两种数学模型,一个描述环路的锁定或跟 踪性能,另一个描述环路的捕捉性能。前者称为相位 模型,后者称为频率模型。 4.2.1 电流型电荷泵锁相环 常用的电流型鉴相器—滤波器组合电路及其等效 电路如图4.2.1所示。

一种快速锁定电荷泵锁相环的设计解读

一种快速锁定电荷泵锁相环的设计

自从上个世纪30年代锁相环理论被提出来以后,锁相环在电子和通讯等领域得到了迅速而广泛的应用。

在数模混合系统中,锁相环是最基本的模块之一,它们被用来进行时钟和数据恢复,解调或者频率合成。

本文设计了一个快速锁定的电荷泵锁相环电路,可以作为800MHz和640MHz时钟发生器,用作单片机等的基准时钟信号的产生模块。

对于传统的电荷泵锁相环,环路带宽

ω_c的选择需要在锁定时间和输出相位噪声之间进行折衷,为了最小化输出噪声抖动,锁相环的环路带宽应当尽可能小,但减小环路带宽会增加锁定时间,为了获得最好的跟踪和捕获特性,环路带宽应尽可能的大。

为了得到快速锁定的锁相环同时满足好的噪声性能,通常采用双斜率鉴频鉴相器,它包含一个用于细调的PFD和一个用于粗调的锁定检测器。

本文所采用的结构能够有效地减小锁定时间,同时环路的稳定性没有改变。

本文设计的锁相环采用SMIC

0.18um CMOS工艺,工作电源电压为3.3V。

使用Mentor公司的射频电路仿真工具EldoRF进行电路仿真。

仿真结果表明,改进的锁相环的锁定时间小于

1.2us,比普通的锁相环的锁定时间减小了很多。

工作在800MHz频率下时,整个锁相环的功耗是21mW。

本文分析和总结了锁相环系统的设计理论,并对电路中的各个子模块做了优化。

文中给出了一个带差分控制的三级环形压控振荡器,该压控振荡器的调谐范围为560MHz到1020MHz,相位噪声在1MHz频偏时为-101.2dBc/Hz,功耗为16.8mW。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. School of MathemБайду номын сангаасtics and Computer Science,Anhui Normal University,Wuhu 241003,China)

电荷泵锁相环系统级功耗估计

作者:魏建军王振愿陈付龙刘乃安李晓辉

来源:《湖南大学学报·自然科学版》2019年第02期

摘;;要:功耗问题是制约集成电路设计的一个重要因素.分析了CMOS集成电路中功耗的来源,集成电路设计中功耗设计的目的,估算方法和功耗模型.研究模拟集成电路的特点和相应的功耗估计方法.针对采用环形振荡器的电荷泵锁相环,研究电荷泵锁相环的组成,各模块的工作原理及对功耗的贡献,提出了电荷泵锁相环系统级功耗估计模型.与实际测量结果相比,相对误差小于22%.该模型易于植入集成电路设计工具,可以对锁相环系统级设计提供功耗方面的参考,提高集成电路的设计质量.

Key words:power estimation;power model;energy transfer;charge pump PLL

集成電路集成度和时钟频率的大幅度提高,导致功耗问题日益突出,功耗已成为许多ASIC设计中的关键因素之一.但是,由于满足功耗设计需要的EDA软件发展缓慢,设计者不得不在设计后期反复验证以满足功耗特性,延长了产品设计周期,推迟了上市时间.为使功耗设计能溶入集成电路设计方法学,使得设计者在考虑延迟、噪声和芯片面积等因素的同时,也能对功耗进行分析权衡,高层次的功耗估计越来越迫切.电荷泵型锁相环频率综合器是一数模混合系统,大量使用在芯片中,提供精确的时钟或载波信号,虽然占用的面积不大,但功耗却很显著,在芯片系统设计阶段对其进行功耗估计,便于芯片的功耗分配.目前数字集成电路存在较为成熟的功耗估计算法,可以从系统级到晶体管级估计功耗.模拟集成电路功耗估计算法研究很少,主要集中在晶体管级,系统级较少.仅有部分文献针对模拟滤波器和ADC提出了系统级功耗估计算法,而且限制了滤波器的类型[1],本文从系统级提出一种电荷泵锁相环的功耗估计算法,在系统设计阶段提供功耗方面的参考.

Abstract:Power is an important factor that restricts the design of Integrated Circuit(IC). The power origin in CMOS IC,the aim of power estimation in IC design,the estimation method,and the power model were analyzed. The characteristic of analog integrated circuit and the corresponding way for power estimation were studied. In order to distribute the power at system level,the construction of charge pump PLL,the principle of every module and the contribution to power were also studied. The power estimation model of charge pump PLL with ring oscillator was proposed at system level. The relative error is less than 22% when compared with the actual measurement. This model is easy to be integrated into design tools and can give guidance on power consumption for PLL at system level to improve the quality of Integrated Circuit design.

1 ;;CMOS集成电路中的功耗

CMOS工艺是集成电路领域最普遍采用的工艺,所实现的电路的功耗由动态功耗和静态功耗组成,来源主要有三个方面:开关功耗(Pactive)、短路功耗(Pshort)和漏电功耗(Pleak).动态功耗包括开关功耗和短路功耗,静态功耗主要指漏电功耗.

开关功耗是电路的逻辑发生改变时对负载电容的充电/放电而引起的功耗,当CMOS电路进行开关操作时,需对输出节点的负载电容进行充电/放电操作,存在有电流流动,需要消耗能量.短路功耗是由于电路中NMOS和PMOS晶体管同时导通时,从电源端到地的导通电流形成的,功耗的大小与输入信号的上升时间、下降时间、工作频率、负载电容、器件尺寸等有关.优化设计门的尺寸尽可能保证输入、输出信号的上升时间、下降时间相等,短路功耗将小于动态功耗的15%[2].漏电功耗主要由三部分构成:MOS晶体管中源、漏扩散区和体区间所形成pn结的反向电流Ipn;次开启电压下存在的反型电荷形成的亚阈值漏电流Isub;由于薄的栅氧化层导致的栅漏电流Ig.在CMOS器件中,反向pn结偏置电流与亚阈值漏电流均在pA级,在特征尺寸为1 μm的情况下,二极管的泄漏电流一般为1 pA. Ipn正比于源、漏扩散区的面积,主要由制造工艺决定.Isub随着晶体管宽长比的增加而线性增加,随着Vgs-VT的减少而呈指数关系下降.与动态功耗相比,静态功耗的影响较小,但随着深亚微米CMOS工艺的发展,器件的阈值电压越来越低,漏电流的影响不容忽视,限制了工作电压的进一步降低.

关键词:功耗估计;功耗模型;能量转移;电荷泵锁相环

中图分类号:TM935 ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;文献标志码:A

Power Estimation of Charge Pump PLL at System Level

WEI Jianjun1,WANG Zhenyuan1,CHEN Fulong2,LIU Naian1,LI Xiaohui1