EDA一位二进制全减器设计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 1位二进制全减器设计

一、实验目的

1.熟悉EDA 技术开发流程;

2.熟悉Quartes II 集成开发软件的使用; 3.初步熟悉PH-1V 型实验装置的使用;

4.学习用原理图输入法和文本输入法进行简单的数字电路设计。

二、实验要求

1.用文本输入法和原理图输入法分别实现一位二进制全减器的设计。

2.进行时序波形仿真,并分析仿真波形图

3.在仿真正确的情况下,对1位二进制全减器分别下载到实验箱中做硬件测试。

三、设计思路/原理图

(1)一位全减器的设计

表一、半减器真值表(so 差值 co 向高位的借位) 表二

表二、全减器真值表(cin 低位来的借位 cout 向高位的借位)

根据半减器真值表可以用文本输入法(VHDL 语言)设计出半减器,,再根据全减器的真值表通过文本输入法(VHDL 语言)调用两个半减器构成一个全减器。

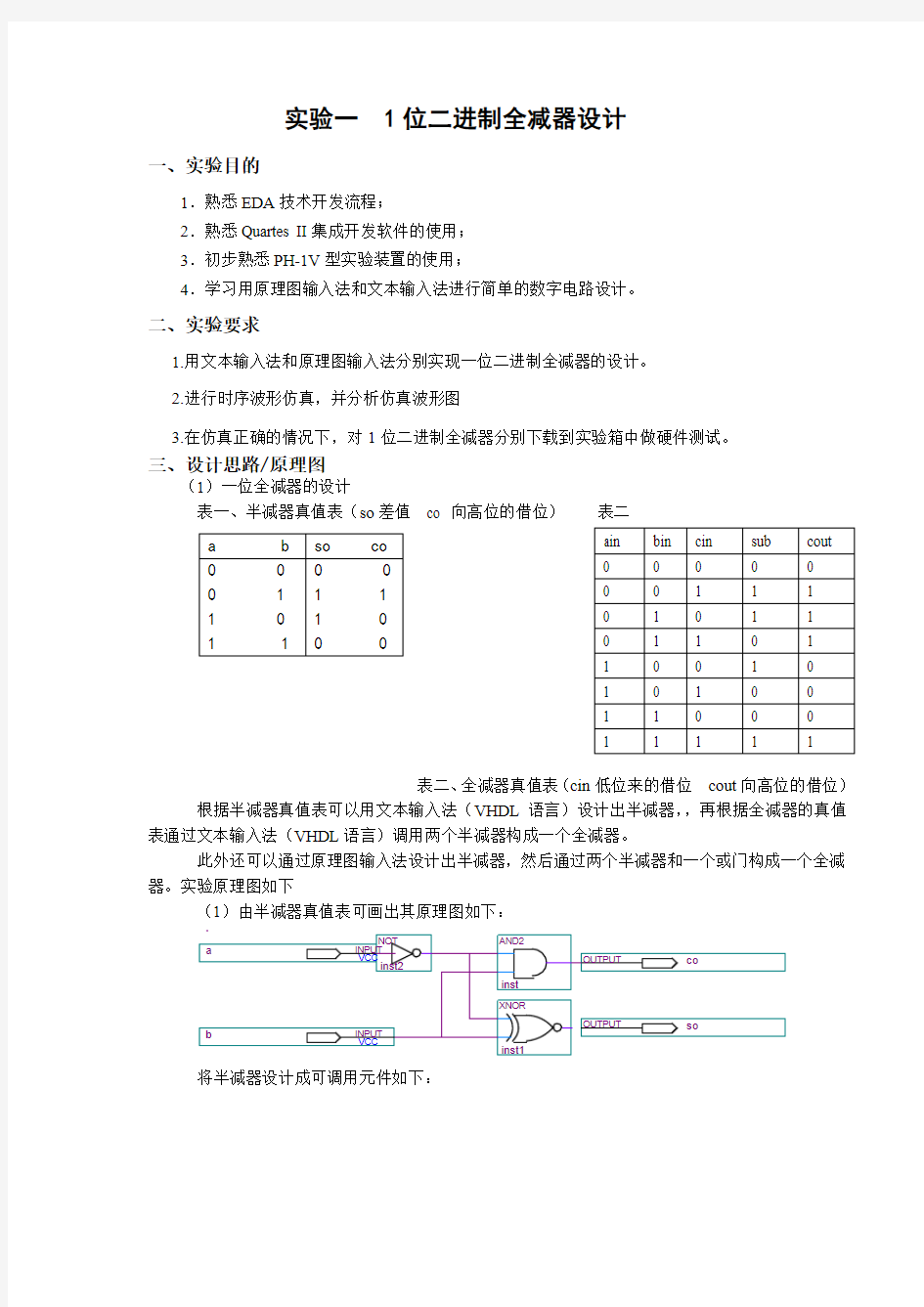

此外还可以通过原理图输入法设计出半减器,然后通过两个半减器和一个或门构成一个全减器。实验原理图如下

(1)由半减器真值表可画出其原理图如下:

将半减器设计成可调用元件如下:

h_sub inst

a b

co so

(2)由全减器的真值表可以画出原理图如下:

四、实验程序

(1)一位半减器文本描述 LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_sub IS

PORT(a,b:IN STD_LOGIC; co,so:OUT STD_LOGIC); END ENTITY h_sub;

ARCHITECTURE fh1 OF h_sub is BEGIN

so<=NOT(a XOR (NOT b));co<=(NOT a)AND b; END ARCHITECTURE fh1; (2)或门逻辑描述 LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS

PORT(a,b:IN STD_LOGIC; c:OUT STD_LOGIC); END ENTITY or2a;

ARCHITECTURE one OF or2a IS BEGIN c<=a OR b;

END ARCHITECTURE one;ne;

(3)一位二进制全减器顶层文件描述 LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_sub IS

PORT (ain,bin,cin:IN STD_LOGIC; cout,sub:OUT STD_LOGIC); END ENTITY f_sub;

ARCHITECTURE fd1 OF f_sub IS

COMPONENT h_sub—调用半减器的声明语句

PORT(a,b:IN STD_LOGIC;

co,so:OUT STD_LOGIC);

END COMPONENT;

COMPONENT or2a—调用或门的声明语句

PORT(a,b:IN STD_LOGIC;

c:OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f:STD_LOGIC;

BEGIN

u1:h_sub PORT MAP(a=>ain,b=>bin,co=>d,so=>e);--例化语句

u2:h_sub PORT MAP(a=>e,b=>cin,co=>f,so=>sub);

u3:or2a PORT MAP(a=>d,b=>f,c=>cout);

END ARCHITECTURE fd1;

五、实验步骤

1、建立工作库文件和编辑设计文件

(1)在D盘新建一个文件夹用来保存工程文件

(2)打开QuartusⅡ8.0软件,选择菜单File->New->VHDL File,点击OK后在打开的界面下输入已经设计好的程序。

(3)输入完程序后,保存文件选择菜单File->Save as,将文件保存到工程文件夹中,文件名不能含有中文字符,最好与程序实体名一样。

(4)保存好文件后,一般会提示是否新建一个工程,选择是,如果没有就在菜单打开File->New project Wizard项,将出现工程项目建立向导。

(5)按照工程项目向导提示设计好工程中要用到的文件放到同一个工程文件夹中,选择实验中用到的芯片和第三方工具(一般默认EDA自带的工具箱,在这里不做任何选择)。

(6)完成工程项目建立后选择processing->start compilation或选择按钮开始全程编译,如果编译过程中出现错误或警告提示,则双击错误或警告提示就可以找到该错误或警告在设计文件的位置。

(7)在完成设计输入和综合编译以后,可以通过时序仿真来检查设计是否符合要求,这里我们可以通过建立波形文件(.vmf)。在选择File->New->Vetor Waveform File项后选择OK。

(8)设计Edit栏选择End Time设计时间为50 us ,在View->ulitity windows中选择Node Finder 或按Alt+1,然后将所有的输入输出拖到波形文件中,设计好输入时序和输出方式后保存文件。选择

processing栏中的Start simulation或选择按钮开始波形仿真。

(9)仿真成功后得到了预期的设计效果后,将引脚锁定。方法如下:选择assignment 中的pins,将To栏的信号锁定到相应的Location引脚列中。引脚号对应关系可以从实验手册中查找。

(10)引脚锁定以后,再编译全程编译一次,然后编程下载,选择Tools->programmer 菜单,设计好编程硬件后点击Start开始下载。

(11)下载成功后在硬件上检测设计思路的是否正确。

六、仿真波形分析

下图为实验所得的波形图