10数字逻辑试卷A

电子技术及数字逻辑试卷A及答案

绝密★启用前黑龙江外国语学院继续教育学院 2014 年 秋 季学期《电子技术及数字逻辑》试卷( A 卷)一、 填空题(本大题共 9小题,每空 1分,共 15分)1.N 型半导体是在本征半导体中掺入 价元素,其多数载流子是 ,少数载流子是 。

2.稳压管的稳压区是其工作在 。

3.数字系统使用 的物理元件,与此相对应,采用的记数制和编码制也都以 数 为基础。

4.使用布尔代数定律时,利用 规则. 规则. 规则可得到更多的公式。

5.放大电路必须加上合适的 才能正常工作。

6.运放的共模抑制比定义为 。

7.直接写出函数F=[(AB+C)D+E]B 的反演函数为 。

8.三极管工作在饱和区时,发射结应为 偏置,集电结应为 偏置。

9.为提高放大电路的输入电阻,应引入 反馈;为降低放大电路输出电阻。

二、选择题(本大题共15小题,每题2分,共30分)1.当温度升高时,二极管的反向饱和电流将 。

A .增大 B.减小 C.不变2.互补输出级采用共集形式是为了使 。

A.电压放大倍数大B.不失真输出电压大C.带负载能力强3.测试放大电路输出电压幅值与相位的变化,可以得到它的频率响应,条件是 。

A. 输入电压幅值不变,改变频率B. B.输入电压频率不变,改变幅值C.输入电压的幅值与频率同时变化 4.交流负反馈是指 。

A .阻容耦合放大电路中所引入的负反馈B .只有放大交流信号时才有的负反馈C .在交流通路中的负反馈5.功率放大电路的最大输出功率是在输入电压为正弦波时,输出基本不失真情况下,负载上可能获得的最大 。

A .交流功率B .直流功率C .平均功率 6.滤波电路应选用 。

A .高通滤波电路 B. 低通滤波电路 C. 带通滤波电路7.放大电路中,测得某三极管三个电极电位U 1.U 2.U 3分别为U 1=3.3V ,U 2=2.6V ,U 3=15V 。

由此可判断该三极管为 。

A .NPN 硅管 B. NPN 锗管 C. PNP 硅管 d.PNP 锗管8.与八进制数(47.3)8等值的数为 。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分)1、为了表示104个信息,需7位二进制编码[V ]2、BCD码能表示0至15之间的任意整数[X ]3、余3码是有权码[X ]4、2421码是无权码[X ]5、二值数字逻辑中变量只能取值6、计算机主机与鼠标是并行通信7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ][X ][V ][V ]9、上升时间和下降时间越长,器件速度越慢[V ]10、卡诺图可用来化简任意个变量的逻辑表达式[X ]、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B2、F= AB CD2分,共20分)1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A °TTL 电路(A) F = ABCD(B) F = AH ・ CD -(C) F= A + B + C + D(D) F = A + B • C + D (E) F= A BCD4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _°(A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q.(D) BC= 1 , D= 15、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。

(A) AB + AC + BC (B) AB + C (A4-B)(C) AB + CABA — O ?=11 QA |— I1 F •-&1 Q AB L Il —(B)悬0----空。

—A — &Bo —Co- &BA3 •满足如图所示电路的输岀函数F 的表达式为丄3B 1 o — VOF(D) AB +C (E) 19.图示电路中,当各触发器的状态为C 时.再输入一个CP 脉冲,融发器的 状态为QiQ 严0 0。

《数字逻辑与数字系统》期末考试试题(A)

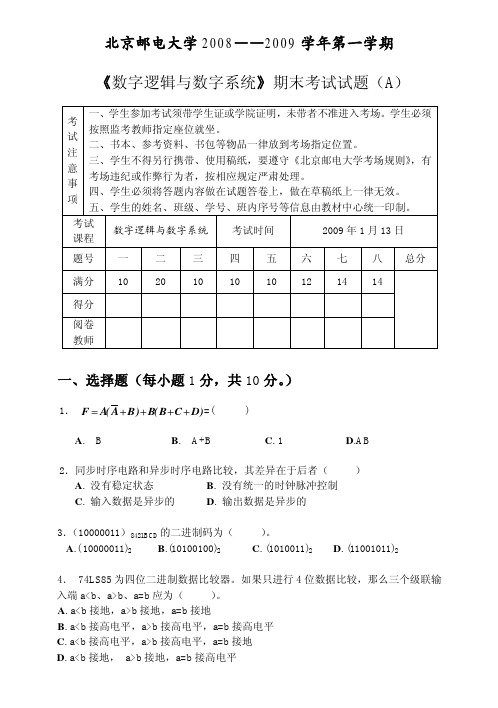

北京邮电大学2008——2009学年第一学期《数字逻辑与数字系统》期末考试试题(A )考试注意事项一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必须按照监考教师指定座位就坐。

二、书本、参考资料、书包等物品一律放到考场指定位置。

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。

四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。

五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。

考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分满分 10 20 10 10 10 12 14 14 得分 阅卷 教师一、选择题(每小题1分,共10分。

)1. )D C B (B )B A (A F ++++==( )A .B B . A+BC . 1D .AB2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。

A .( 10000011)2B .(10100100)2C . (1010011)2D . (11001011)24. 74LS85为四位二进制数据比较器。

如果只进行4位数据比较,那么三个级联输入端a<b 、a>b 、a=b 应为( )。

A . a<b 接地,a>b 接地,a=b 接地B . a<b 接高电平,a>b 接高电平,a=b 接高电平C . a<b 接高电平,a>b 接高电平,a=b 接地5. N 个触发器可以构成能寄存( )位二进制数码的寄存器。

A. NB. 2NC. 2ND. N 26.时序电路中对于自启动能力的描述是( )。

A . 无效状态自动进入有效循环,称为具有自启动能力。

2020—2021学年非毕业班集成电路设计与集成系统专业《数字逻辑电路》期末考试题及答案(试卷A)

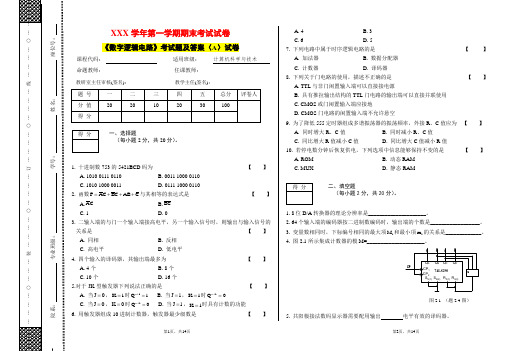

院系: 专业班级: 学号: 姓名: 座位号:XXX 大学2020—2021学年非毕业班集成电路设计与集成系统专业《数字逻辑电路》期末考试题及答案(试卷A )题 号 一 二 三 四 五 总分 评卷人 分 值 20 20 10 20 30 100得 分得 分一、 选择题;(每小题2分,共20分)。

1、将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为( )。

A 、采样;B 、量化;C 、保持;D 、编码;2、8个输入端的编码器按二进制数编码时,输出端的个数是教研室主任审核(签名): 教学主任(签名):课程代码: 适用班级:命题教师:任课教师:院系: 专业班级: 学号: 姓名: 座位号:( )。

A 、2个;B 、3个;C 、4个;D 、8个;3、下列电路中,不属于组合逻辑电路的是( )。

A 、译码器;B 、全加器;C 、寄存器;D 、编码器;4、CMOS 数字集成电路与TTL 数字集成电路相比突出的优点是( )。

A 、微功耗;B 、高速度;C 、高抗干扰能力;D 、电源范围宽;5、指出下列各式中哪个是四变量A 、B 、C 、D 的最大项( )。

A 、ABC ;B 、A+B+C+D ;C 、D ABC ; D 、B AC ;6、同步时序电路和异步时序电路比较,其差异在于后者( )。

院系: 专业班级: 学号: 姓名: 座位号:A 、没有触发器;B 、没有统一的时钟脉冲控制;C 、没有稳定状态;D 、输出只与内部状态有关;7、两片74LS290芯片扩展而成的计数器,最大模数是( )。

A 、80;B 、20;C 、54;D 、100;8、由与非门组成的基本RS 触发器不允许输入的变量组合S 、R 为( )。

A 、1==S R ; B 、10==S R 、; C 、01==S R 、;D 、==S R ;9、逻辑函数的表示方法中具有唯一性的是( )。

A 、真值表;B 、表达式;C 、表达式;D 、卡诺图;10、将TTL 与非门作非门使用,则多余输入端应做的处理是( )。

数字逻辑10套题

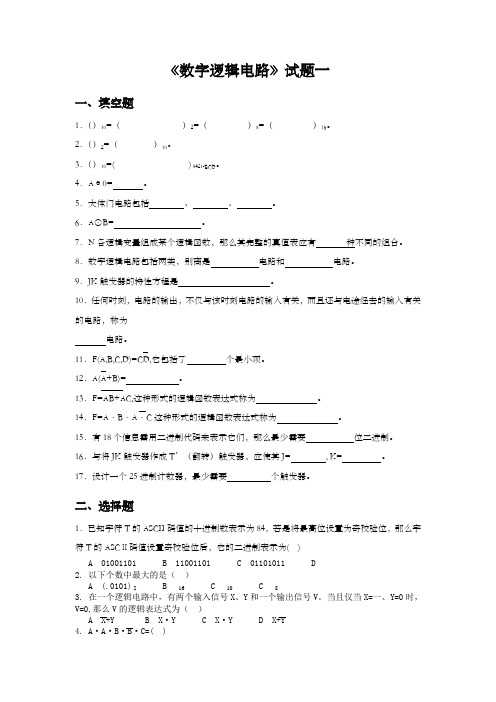

《数字逻辑电路》试题一一、填空题1.()10=()2=()8=()16。

2.()2=()10。

3.()10=( ) 8421-BCD。

4.A⊕0= 。

5.大体门电路包括、、。

6.A⊙B= 。

7.N各逻辑变量组成某个逻辑函数,那么其完整的真值表应有种不同的组合。

8.数字逻辑电路包括两类,别离是电路和电路。

9.JK触发器的特性方程是。

10.任何时刻,电路的输出,不仅与该时刻电路的输入有关,而且还与电途经去的输入有关的电路,称为电路。

11.F(A,B,C,D)=CD,它包括了个最小项。

12.A(A+B)= 。

13.F=AB+AC,这种形式的逻辑函数表达式称为。

14.F=A·B·A·C这种形式的逻辑函数表达式称为。

15.有18个信息需用二进制代码来表示它们,那么最少需要位二进制。

16.与将JK触发器作成T’(翻转)触发器,应使其J= , K= 。

17.设计一个25进制计数器,最少需要个触发器。

二、选择题1.已知字符T的ASCII码值的十进制数表示为84,若是将最高位设置为奇校验位,那么字符T的ASCⅡ码值设置奇校验位后,它的二进制表示为( )A 01001101B 11001101C 01101011 D2. 以下个数中最大的是()A (.0101) 2B 16C 10 C 83. 在一个逻辑电路中,有两个输入信号X、Y和一个输出信号V。

当且仅当X=一、Y=0时,V=0,那么V的逻辑表达式为()A X+YB X·YC X·YD X+Y4. A·A·B·B·C=( )A ABC C 1D 05. A+BC+AB+A=( )A AB AC 1D 06. F(A,B,C)=ABC+ABC+ABC=( )A ∑m(0,2,4)B ∑m(3,5,7)C ∑m(1,3,5)D ∑m(4,5,7)7. A⊕B=( )A AB+ AB B AB + ABC A BD A B8. 对正逻辑而言,某电路是与门,那么对负逻辑而言是()A 与门B 与非门C 或非门D 或门触发器在同步工作时,假设现态Q n=0,要求抵达次态Q n+1=1,那么应使JK=( )A 00B 01C 1XD X110.图(1)中要求输出F=B,那么A应为( )A 0B 1 A =1 FC B BD B 图(1)三、化简以下函数表达式一、代数化简:Y=(AB+A B+A B)(A+B+D+A B D)二、Y=AB+A B+A B3、卡诺图化简:F=(A,B,C,D)=∑m(0,1,2,3,4,6,8,9,10,11,12,14)四、芯片的应用1.别离用74138和74153实现逻辑函数表达式F=AB+BC+AC2.用1.用与非门设计一个组合电路,用来检测并行输入的四位二进制数B4B3B2B1当其值大于或等于5时,输出F=1,反之F=0。

计算机科学与技术专业《数字逻辑电路》考试题及答案(A)试卷

院系: 专业班级: 学号: 姓名: 座位号:A. 4B. 3C. 6D. 57. 下列电路中属于时序逻辑电路的是 【 】A. 加法器B. 数据分配器C. 计数器D. 译码器8. 下列关于门电路的使用,描述不正确的是 【 】A. TTL 与非门闲置输入端可以直接接电源B. 具有推拉输出结构的TTL 门电路的输出端可以直接并联使用C. CMOS 或门闲置输入端应接地D. CMOS 门电路的闲置输入端不允许悬空 9. 为了降低555定时器组成多谐振荡器的振荡频率,外接R 、C 值应为 【 】A. 同时增大R 、C 值B. 同时减小R 、C 值C. 同比增大R 值减小C 值D. 同比增大C 值减小R 值 10. 若停电数分钟后恢复供电,下列选项中信息能够保持不变的是 【 】A. ROMB. 动态RAMC. MUXD. 静态RAM1. 8位D/A 转换器的理论分辨率是_____________________。

2. 64个输入端的编码器按二进制数编码时,输出端的个数是__________________。

3. 变量数相同时,下标编号相同的最大项i M 和最小项i m 的关系是_____________。

4. 图2.1所示集成计数器的模M=_____________________。

图2.1 (题2.4图)5. 共阳极接法数码显示器需要配用输出 电平有效的译码器。

二、填空题(每小题2分,共20分)。

6. 对于T 触发器,当T=______时,触发器处于保持状态。

7. 逻辑函数C B AB F +=的反函数F 为_____________________。

8. 5个变量的逻辑函数全部最大项有_____________________个。

9. 二进制数()20110.101110转换成十进制数是___________________。

10. 同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为_____________________。

2016-2017学年1学期数字逻辑电路期末考试试卷_A卷_

3

vO

6

vI2 555

2

15

0.01µF

5.逻辑函数

P=A

⊕B

⊕C,写成最小项和的形式应为

P(A,B,C)=

∑ m

(

)。

评卷人

得分

三、综合题(8 小题,1-5 题每题 8 分,6 题 10 分, 7-8 题每题 15 分,共 80 分)

4.在 10 位二进制数 D/A 转换器中,已知其最大满刻度输出模拟电压 Vom=5V,求最小分辨

电压 VLSB 和分辨率。

5.图为由中规模 4 位二进制同步加法计数器 74LS161(同步置数,异步清零,QD 最高位)

构成的电路,试画出完整状态转换图,说明它是几进制计数器?

1.化简逻辑函数 P=AB+ A C+ B C+CD,用与非门实现该逻辑函数。 2.分析图逻辑电路,写出输出 Y0、Y1、Y2 和 Y3 的表达式和真值表,说明该电路的逻辑功能。

6. 试分析图所示电路的逻辑功能,列出特性表,写出特性方程。

队别__________

3.图题为一通过可变电阻 RW 实现占空比调节的多谐振荡器,图中 R W = RW1 + RW 2 ,试分

析电路的工作原理,求振荡频率 f 和占空比 q 的表达式。

试卷 第 2 页 (共 3 页)

…………………………密………………………………封………………………………线………………………………………

南京信息工程大学 2015-2016 学年第二学期《数字电子技术基础》期末考试试卷

南京信息工程大学

2016-2017 年 第 1 学期 数字逻辑电路 课程 期末 试卷(A 卷)

本试卷共 3 页;考试时间 120 分钟;出卷时间 2016 年 12 月

数字逻辑技术试卷及解析

数字逻辑技术试卷-第2章一、填空题1.逻辑电路中,电平接近0时称为低电平,电平接近V CC或V DD时称为高电平。

2.数字电路中最基本的逻辑门有与、或和非门。

常用的复合逻辑门有与非门、或非门、与或非门、异或门和同或门。

3.图腾结构的TTL集成电路中,多发射极三极管可完成与门逻辑功能。

4.CMOS反相器是两个增强型的MOS管组成,且其中一个是N沟道管,另外一个是P沟道管,由于两管特性对称,所以称为互补对称CMOS反相器。

5.TTL与非门输出高电平U OH的典型值是 3.6V,低电平U OL的典型值是0.3V。

6.普通的TTL与非门具有图腾结构,输出只有高电平和低电平两种状态;TTL三态与非门除了具有1态和0态,还有第三种状态高阻态,三态门可以实现总线结构。

7.集电极开路的TTL与非门又称为OC门,几个OC门的输出可以并接在一起,实现线与逻辑功能。

8.TTL集成电路和CMOS集成电路相比较,其中TTL集成电路的带负载能力较强,而CMOS集成电路的抗干扰能力较强。

9.用三态门构成总线连接时,依靠使能端的控制作用,可以实现总线的共享而不至于引起总线冲突。

10. TTL集成与门多余的输入端可与有用端并联或接高电平;TTL集成或门多余的输入端可与有用端并联或接低电平。

二、判断下列说法的正误1.所有的集成逻辑门,其输入端子均为两个或两个以上。

(错)2.根据逻辑功能可知,异或门的反是同或门。

(对)3.具有图腾结构的TTL与非门可以实现“线与”逻辑功能。

(错)4.基本逻辑门电路是数字逻辑电路中的基本单元。

(对)5.TTL和CMOS两种集成电路与非门,其闲置输入端都可以悬空处理。

(错)6.74LS系列产品是TTL集成电路的主流产品,应用最广泛。

(对)7.74LS系列集成电路属于TTL型,CC4000系列集成电路属于CMOS型。

(对)8.与门多余的输出端可与有用端并联或接低电平。

(错)9.OC门不仅能够实现“总线”结构,还可构成与或非逻辑。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试A卷参考答案一、判断题:下面描述正确的打‘√’,错误的打‘×’(每小题1分,共10分)1、为了表示104个信息,需7位二进制编码[√]2、BCD码能表示0至15之间的任意整数[×]3、余3码是有权码[×]4、2421码是无权码[×]5、二值数字逻辑中变量只能取值0和1,且表示数的大小[×]6、计算机主机与鼠标是并行通信[×]7、计算机主机与键盘是串行通信[√]8、占空比等于脉冲宽度除于周期[√]9、上升时间和下降时间越长,器件速度越慢[√]10、卡诺图可用来化简任意个变量的逻辑表达式[×]二、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)AB+1、F=A⊕B2、F=CD三、选择题:(多选题,多选或少选不得分,每小题2分,共20分)四、填空题(每空1分,共20分)1、一个触发器可表示__1__位二进制码,三个触发器串接起来,可表示__3__ 位二进制数。

2、欲表示十进制的十个数码,需要__4__个触发器。

3、寄存器中,与触发器相配合的控制电路通常由_门电路_(选择提示:门电路、触发器、晶体二极管)构成。

4、一个五位的二进制加法计数器,由00000状态开始,问经过75个输入脉冲后,此计数器的状态为__01011_。

5、四位移位寄存器可以寄存四位数码,若将这些数码全部从串行输出端输出,需经过__3__个时钟周期。

6、_RS_触发器存在输入约束条件,_主从JK_触发器会出现一次翻转现象。

7、负跳沿触发翻转的主从JK触发器的输入信号应该在CP为_低电平_时加入,在CP为_高电平_时输入信号要求稳定不变。

8、正跳沿触发翻转的D触发器的输入信号在CP _上升沿_前一瞬间加入。

9、由与非门组成的基本RS触发器当输入R=0,S=0时,同向输出端Q=__1__,反向输出端Q=__1__,当_R、S同时由0变1_时,输出不定状态。

数字逻辑电路期末试卷及答案 (3)

第1页,共8页第2页,共8页院系: 专业班级: 学号: 姓名: 座位号:20 -20 学年第 学期期末考试试卷《数字逻辑电路》(A )卷一、选择题(每小题2分,共20分)1、下列数中最大的数是 【D 】 A 、(3C )16 B 、(57)8C 、(70)10D 、(1110010)22、8个输入端的编码器按二进制数编码时,输出端的个数是 【B 】 A 、2个 B 、3个C 、4个D 、8个3、逻辑电路中的晶体管一般工作在【B 】A 、放大区B 、饱和区或截至区C 、截至区D 、饱和区4、同步时序电路和异步时序电路比较,其差异在于后者 【B 】 A 、没有触发器; B 、没有统一的时钟脉冲控制; C 、没有稳定状态; D 、输出只与内部状态有关;5、n 个变量的逻辑函数全部最大项的个数有 【C 】 A 、n B 、2n C 、2nD 、2n -16、555定时器的结构如图1.1所示,如果芯片的5脚悬空;RD =V CC =5V ,6脚输入4V 电压,2脚输入2V 电压,下列关于555电路说法正确的是 【 A 】U CC U CO U 6(TH)(TR)U oR D U 2放电端图1.1(题1.6图)A 、U O 输出低电平,放电开关V 1导通;B 、U O 输出高电平,放电开关V 1截止;C 、U O 输出低电平,放电开关V 1截止;D 、U O 输出高电平,放电开关V 1导通; 7、图1.2所示用74LS161(同步16进制计数器,Cr 异步清零端、LD 同步置数端、OC 进位输出端,P 、T 计数允许端)构成的计数器正确的说法是 【D 】A 、同步置数法组成的9进制计数器;B 、异步置数法组成的8进制计数器;C 、同步置数法组成的10进制计数器;D 、异步复位法组成的9进制计数器; 图1.2( 题1.7图) 8、要使由与非门组成的基本RS 触发器保持原状态不变,D S 、D R 端输入的信号应取 【A 】 A 、1==D D S RB 、10==D D S R 、C 、01==D DS R 、 D 、0==D D S R9、为获得输出频率非常稳定的脉冲信号,应采用 【C 】A 、对称多谐振荡器B 、555定时器组成的对称多谐振荡器第3页,共8页第4页,共8页装订线内不许答题 C 、石英晶体振荡器 D 、单稳态触发器 10、下列关于TTL 与非门闲置输入端的处理不正确的是 【D 】 A 、直接接电源电压VccB 、与有用输入端并联使用C 、外界干扰小时,可以剪断或悬空D 、直接接地1、二进制数-110011的补码是 1001101 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

…………….……………..装……………………订………………..线…………….

……………..

阜阳师范学院 2010 ——

2011 学年度第 一 学期考试卷(A )

计算机与信息

学院 2009级计科、10专升本

专业

数字逻辑

课程,共 2 页, 第1页,共印刷

份, 2011 年 01 月 14 日 10:00 — 11:40 考试,任课教师 王诗兵王中心 拟题 集体

学号

一、 判断题(每题2分,共10分)

1、在逻辑代数中由AB=AC 能推出B=C 。

( )

2、触发器的电路结构和逻辑功没有必然的联系。

( )

3、相同波特率传输的数字信号,它们的占空比可以不同。

( )

4、组合电路中有竞争一定能产生冒险。

( )

5、所有TTL 逻辑门芯片,其14或16引脚都是V CC 输入端。

( )

二、 填空题(每题3分,共24分)

1、-1011001的原码为( ),反码为( ),补码为( );

2、4位扭环形计数器的计数进制为( ),若此扭环形计数器工作的时钟频率为8KHz ,其输出波形的频率为( );

3、根据反演规则,写出逻辑函数A CD AB F ++=的非函数=F ( );

4、三态门的三态是指:(____________、_____________和___________________);

5、十进制数100对应的二进制数是(___________),对应的八进制数是(_________);

6、为使B F =,则A 应为何值(高电平或低电平)?

A=( ) A=( ) A=( ) ;

7、有一移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数除以十进制数2,则需要将该移位寄存器中的数( )移( )位,需要( )个移位脉冲;

8、对250个不同符号进行二进制编码时,至少需要( )位二进制编码,其中有( )种组合是无效的。

三、 选择题(每题3分,共24分)

1、下列编码技术中属于有权码的是( )

A. ASCII 码

B. 余3码

C. 5421BCD 码

D. 格雷码

2、若已知XY+YZ+XZ=XY+Z ,判断(X+Y )(Y+Z )(X+Z )=(X+Y)Z 成立的最简单方法是依据下面哪个规则?( )

A . 代入规则 B. 对偶规则 C. 反演规则 D. 互补规则

3、8-3线的优先编码器的优先权由高到低的顺序为I 7、I 6、I 5、I

4、I 3、I 2、I 1、I 0,输出为Y 2Y 1Y 0,输入为高电平有效,反相输出,当输入I 7I 6I 5I 4I 3I 2I 1I 0为01111011时,输出

Y 2Y 1Y 0为( ) A.110 B.101 C.001 D.010 4、同步时序逻辑电路与异步时序逻辑电路的差别在于后者( ) A.没有触发器; B.没有统一的时钟控制;

C.没有稳定的状态;

D.输出只与内部状态有关

5、一个4位二进制计数器的初始状态是0000,当输入35个记数脉冲后,计数的状态

是( )

A.0100

B.0101

C.0011

D.1111

6、在下列电路中,在时序逻辑电路中一般都会包含的是( ) A.编码器 B.移位寄存器 C.触发器 D.译码器

7、2011个A 进行异或运算,结果为( ) A. 0 B. 1 C. A D. A

8、下列各种电路中不属于时序逻辑电路的是( ) A.加法器; B.触发器; C.移位寄存器; D.计数器

班 姓名

级

学院

…………….……………..装……………………订………………..线…………….……………..

计算机与信息 学院 2009级计科、10专升本 专业 数字逻辑 课程 共 2 页,第2页,共印刷 份, 2011 年 01 月 14 日 10:00 — 11:40 考试,任课教师

四、证明题(6分)

用逻辑代数公式证明若0AB =,则有A B A B ⊕=+。

五、分析设计题(1题10分,2题8分,3题8分,4题10分,共36分)

1、根据图示电路图,(1)、写出驱动方程、状态方程;(2)、画出状态表、状态转换图,指出可以做几进制计数器,并分析是否具有自启动能力。

2、试用8选1数据选择器74HC151产生逻辑函数AB C B A BC A L ++=,画出设计逻辑图。

3、下图是一种正向四位二进制集成计数器74LS161,具有异步清零和同步预置数的功能。

请用反馈清零法或反馈置数法将其设计成十进制计数器,要求:1)画出电路连接图;2)画出设计后电路的状态转换图。

4、举重比赛的裁判由一个主裁判和两个副裁判组成,当主裁判认可且至少一名副裁判也认可时,选手的成绩才有效。

请设计举重比赛的判决逻辑电路,写出逻辑抽象过程,列出真值表、逻辑表达式,并画出逻辑图。

(1)采用普通逻辑门电路实现。

(2)采用3-8线变量译码器74LS138和其它门电路实现。

…………….……………..装……………………订………………..线…………….……………..

…………….……………..装……………………订………………..线…………….……………..

…………….……………..装……………………订………………..线…………….……………..

…………….……………..装……………………订………………..线…………….……………..。