linux 16550标准 uart小数分频

FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

FPGA分频与倍频的简单总结(涉及⾃⼰设计,调⽤时钟IP核,调⽤MMCM原语模块)原理介绍1、分频FPGA设计中时钟分频是重要的基础知识,对于分频通常是利⽤计数器来实现想要的时钟频率,由此可知分频后的频率周期更⼤。

⼀般⽽⾔实现偶数系数的分频在程序设计上较为容易,⽽奇数分频则相对复杂⼀些,⼩数分频则更难⼀些。

1)偶分频系数=时钟输⼊频率/时钟输出频率=50MHz/5MHz=10,则计数器在输⼊时钟的上升沿或者下降沿从0~(10-1)计数,⽽输出时钟在计数到4和9时翻转。

2)奇分频系数=50MHz/10MHz=5,则两个计数器分别在输⼊时钟的上升沿和下降沿从0~ (5-1)计数,⽽相应的上升沿和下降沿触发的输出时钟在计数到1和4时翻转,最后将两个输出时钟进⾏或运算从⽽得到占空⽐为50%的5分频输出时钟。

下图所⽰为50MHz输⼊时钟进⾏10分频和5分频的仿真波形2、倍频两种思路:PLL(锁相环)或者利⽤门延时来搭建注意:此仿真是利⽤FPGA内部电路延迟来实现的倍频需要在后仿真下才能看到波形,在⾏为仿真下⽆法得到输出波形。

⼀、时钟IP的分频倍频相关参数说明输⼊时钟:clk_in1(125MHz)输出时钟:clk_out1(50MHz),clk_out2(74.25MHz)则VCO Freq=1262.5MHz=clk_in1*CLKFBOUT_MULT_F/DIVCLK_DIVIDE=125*50.5/5clk_out1(50MHz)=VCO_Freq/Divide=1265.5/25.250clk_out2(74.25MHz)=VCO_Freq/Divide=1265.5/17⼆、MMCME4_ADVMMCME4是⼀种混合信号块,⽤于⽀持频率合成、时钟⽹络设计和减少抖动。

基于相同的VCO频率,时钟输出可以有单独的分频、相移和占空⽐。

此外,MMCME4还⽀持动态移相和分数除法(1)Verilog 初始化模板MMCME4_ADV #(.BANDWIDTH("OPTIMIZED"), // Jitter programming.CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKFBOUT_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN2_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT0_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT1_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT2_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT3_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128).CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT4_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT5_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT6_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).COMPENSATION("AUTO"), // Clock input compensation.DIVCLK_DIVIDE(1), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1.IS_CLKIN2_INVERTED(1'b0), // Optional inversion for CLKIN2.IS_CLKINSEL_INVERTED(1'b0), // Optional inversion for CLKINSEL.IS_PSEN_INVERTED(1'b0), // Optional inversion for PSEN.IS_PSINCDEC_INVERTED(1'b0), // Optional inversion for PSINCDEC.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999)..REF_JITTER2(0.0), // Reference input jitter in UI (0.000-0.999)..SS_EN("FALSE"), // Enables spread spectrum.SS_MODE("CENTER_HIGH"), // Spread spectrum frequency deviation and the spread type .SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns).STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked)MMCME4_ADV_inst (.CDDCDONE(CDDCDONE), // 1-bit output: Clock dynamic divide done.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6.DO(DO), // 16-bit output: DRP data output.DRDY(DRDY), // 1-bit output: DRP ready.LOCKED(LOCKED), // 1-bit output: LOCK.PSDONE(PSDONE), // 1-bit output: Phase shift done.CDDCREQ(CDDCREQ), // 1-bit input: Request to dynamic divide clock.CLKFBIN(CLKFBIN), // 1-bit input: Feedback clock.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.DADDR(DADDR), // 7-bit input: DRP address.DCLK(DCLK), // 1-bit input: DRP clock.DEN(DEN), // 1-bit input: DRP enable.DI(DI), // 16-bit input: DRP data input.DWE(DWE), // 1-bit input: DRP write enable.PSCLK(PSCLK), // 1-bit input: Phase shift clock.PSEN(PSEN), // 1-bit input: Phase shift enable.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement.PWRDWN(PWRDWN), // 1-bit input: Power-down.RST(RST) // 1-bit input: Reset);(2)本实验仿真所⽤参数配置说明及部分端⼝调⽤1、参数配置说明本实验通过输⼊时钟CLKIN1(150MHz),实现输出反馈时钟CLKFBOUT(150MHz)、输出时钟CLKOUT0(74.25MHz)、输出时钟CLKOUT1(74.25MHz)、输出时钟CLKOUT2(59.4MHz)、输出时钟CLKOUT3(49.5MHz)。

Silicon Labs EFM8BB2 MCU数据手册(中文版)

Serial Interfaces

2 x UART

SPI

I2C / SMBus

High-Speed I2C Slave

I/O Ports

External Interrupts

Pin Reset

General Purpose I/O

Pin Wakeup

8-bit SFR bus

Timers and Triggers

CMOS Oscillator Input

Port I/O Configuration

Digital Peripherals

UART0 UART1

Timers 0, 1, 2, 3, 4

3-ch PCA

I2C Slavbar Decoder

SPI CRC

Clock Management

External CMOS Oscillator

High Frequency 49 MHz RC Oscillator

Energy Management

Internal LDO Regulator

Power-On Reset

Flash Program Memory

(16 KB)

15

10

7

Yes —

-40 to +85 QFN20 C

| Smart. Connected. Energy-friendly.

Preliminary Rev. 0.2 | 2

3. 系统概述

3.1 简介

EFM8BB2 数据表

系统概述

C2CK/RSTb

VDD VREGIN

GND

C2D

Reset

Power-On Reset

linux在TQ2440上移植6--完善串口驱动

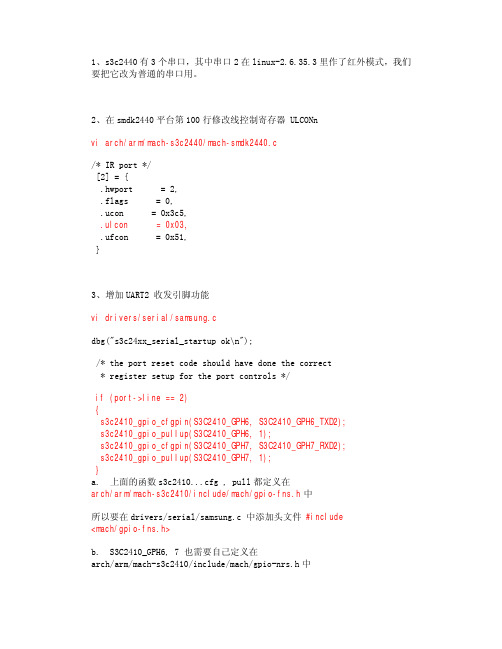

1、s3c2440有3个串口,其中串口2在linux-2.6.35.3里作了红外模式,我们要把它改为普通的串口用。

2、在smdk2440平台第100行修改线控制寄存器 ULCONnvi arch/arm/mach-s3c2440/mach-smdk2440.c/* IR port */[2] = {.hwport = 2,.flags = 0,.ucon = 0x3c5,.ulcon = 0x03,.ufcon = 0x51,}3、增加UART2 收发引脚功能vi drivers/serial/samsung.cdbg("s3c24xx_serial_startup ok\n");/* the port reset code should have done the correct* register setup for the port controls */if (port->line == 2){s3c2410_gpio_cfgpin(S3C2410_GPH6, S3C2410_GPH6_TXD2);s3c2410_gpio_pullup(S3C2410_GPH6, 1);s3c2410_gpio_cfgpin(S3C2410_GPH7, S3C2410_GPH7_RXD2); s3c2410_gpio_pullup(S3C2410_GPH7, 1);}a. 上面的函数s3c2410...cfg , pull都定义在arch/arm/mach-s3c2410/include/mach/gpio-fns.h中所以要在drivers/serial/samsung.c 中添加头文件 #include<mach/gpio-fns.h>b. S3C2410_GPH6, 7 也需要自己定义在arch/arm/mach-s3c2410/include/mach/gpio-nrs.h中#define S3C2410_GPH6 S3C2410_GPH(6)#define S3C2410_GPH7 S3C2410_GPH(7)同样也要在drivers/serial/samsung.c 中添加头文件 #include<mach/gpio-nrs.h>c. S3C2410_GPH6_TXD2S3C2410_GPH7_RXD2定义在arch/arm/mach-s3c2410/include/mach/regs-gpio.h同样也要在drivers/serial/samsung.c 中添加头文件 #include<mach/regs-gpio.h>4、下面还有一个重要的数据结构第889行static struct uart_driver s3c24xx_uart_drv = {.owner = THIS_MODULE,.dev_name = "s3c2410_serial", //这个是串口设备的名称,必须和文件系统的inittab里控制台的名称相对应.nr = CONFIG_SERIAL_SAMSUNG_UARTS,.cons = S3C24XX_SERIAL_CONSOLE,.driver_name = S3C24XX_SERIAL_NAME,.major = S3C24XX_SERIAL_MAJOR,.minor = S3C24XX_SERIAL_MINOR,};5、make menuconfigDdvices Drivers --->Character devices --->Serial Drivers --->1、s3c2440有3个串口,其中串口2在linux-2.6.35.3里作了红外模式,我们要把它改为普通的串口用。

M0516系列 中文资料及引脚功能

5.3 管脚描述........................................................................................................................ 11

6

DC 电气特性.............................................................................................................................. 14

5.1 QFN 33 pin...................................................................................................................... 9

5.2 LQFP 48 pin.................................................................................................................. 10

支持串行调试(SWD)接口,2 个观察点/4 断点。

z 内建一组 LDO支持宽工作电压范围:2.5V~5.5V

z 存储器 32KB/64KB Flash用于存储程序代码(APROM)

4KB Flash用于存储数据(DataFlash)

7

AC 电气特性 .............................................................................................................................. 17

基于FPGA的双模前置小数分频器的设计 毕业设计

基于FPGA的双模前置小数分频器的设计时间:2010-11-12 10:28:13 来源:作者:频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。

分频器是集成电路中最基础也是最常用的电路。

整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。

但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

本文利用VerilogHDL硬件描述语言的设计方式,通过ModelSimSE开发软件进行仿真,设计基于FPGA的双模前置小数分频器。

随着超大规模集成电路的发展,利用FPGA小数分频合成技术解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1 双模前置小数分频原理小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K的小数分频,K可表示为:式中:n,N,X均为正整数;n为到X的位数,即K有n位小数。

另一方面,分频比又可以写成:式中:M为分频器输入脉冲数;P为输出脉冲数。

令P=10n,则:以上是小数分频器的一种实现方法,即在进行10n次N分频时,设法多输入X个脉冲。

2 电路组成每个周期分频N+10-n.X,其电路双模前置小数分频器电路由÷N/N+1双模分频器、控制计数器和控制逻辑3部分组成。

当a点电平为1时,进行÷N分频;当a点电平为0时进行÷N+1分频。

适当设计控制逻辑,使在10n个分频周期中分频器有X次进行÷N+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了X.(N+1)+(10n-X).N个脉冲,也就是10n.N+X个脉冲,其原理如图1所示。

3 小数分频器的Verilog-HDL设计现通过设计一个分频系数为8.7的分频器来给出使用VerilogHDL语言设计数字逻辑电路的一般设计方法。

9650 超频BIOS设置

按DEL步入BIOS先关了节电功效Advanced Cool&Quiet control{Disabled}如许就能够封闭Ai Overclock Tuner{自动}回车"CPU Level Up",默许就好了FSB Strap to North Bridge",即选择你的CPU默许的外频,选择"Auto"的话,在内存分频大将会患上到所有分频选项FSB Frequency--外频230-250均可原始外频是200 PC-E频率配置,一般选择101-105之间守旧配置内存分频,适才"FSB Strap to North Bridge"配置为"Auto"就会浮现全分频段,看你内存健康水平而设定了DDR2 1000MHz内存1T 2T选项,守旧配置为2T吧DRAM Command Rate内存参量配置,这组配置合适跑DDR1000-1200的参量设定这些个Auto便可"CPU Spread Spectrum",超频时CPU Spread最佳选为disable,要是它的BIOS没有做自动关失展频的功效选auto就不行那一些电压就不提了,不调也而已经生存F10重启这是最简略的超频了!回覆(共1条)风行爱情(快问蚁工)按DEL步入BIOS先关了节电功效这个应该会懂患上吧Advanced Cool&Quiet control{Disabled}如许就能够封闭Ai Overclock Tuner{自动}回车"CPU Level Up",默许就好了FSB Strap to North Bridge",即选择你的CPU默许的外频,选择"Auto"的话,在内存分频大将会患上到所有分频选项FSB Frequency--外频230-250均可原始外频是200 PC-E频率配置,一般选择101-105之间守旧配置内存分频,适才"FSB Strap to North Bridge"配置为"Auto"就会浮现全分频段,看你内存健康水平而设定了DDR2 1000MHz内存1T 2T选项,守旧配置为2T吧DRAM Command Rate内存参量配置,这组配置合适跑DDR1000-1200的参量设定这些个Auto便可"CPU Spread Spectrum",超频时CPU Spread最佳选为disable,要是它的BIOS没有做自动关失展频的功效选auto就不行那一些电压就不提了,不调也而已经生存F10重启。

单片机分频方法

单片机分频方法

单片机分频方法是指通过单片机的计数器模块,将输入的高频信号进行分频,得到低频信号的一种方法。

在实际应用中,单片机分频方法被广泛应用于各种计数、定时、测量等领域。

单片机分频方法的实现原理是利用单片机内部的计数器模块,将输入的高频信号进行计数,当计数值达到一定的阈值时,输出一个低频信号。

这个阈值就是分频系数,通过改变分频系数,可以得到不同的低频信号。

单片机分频方法的实现步骤如下:

1. 配置计数器模块:选择计数器模块,并设置计数器的工作模式、计数方向、计数值等参数。

2. 设置分频系数:根据需要得到的低频信号频率,计算出相应的分频系数,并将其设置到计数器模块中。

3. 输入高频信号:将需要分频的高频信号输入到计数器模块的计数引脚上。

4. 输出低频信号:当计数器模块的计数值达到设定的阈值时,输出一个低频信号。

单片机分频方法的优点是可以实现高精度的分频,而且可以根据需要灵活地改变分频系数,得到不同的低频信号。

同时,由于单片机

内部集成了计数器模块,所以不需要额外的硬件电路,可以大大简化系统设计。

在实际应用中,单片机分频方法被广泛应用于各种计数、定时、测量等领域。

例如,在数字频率计中,可以利用单片机分频方法将输入的高频信号分频,得到低频信号后再进行计数,从而实现对高频信号频率的测量。

在定时器中,可以利用单片机分频方法实现对定时时间的精确控制。

单片机分频方法是一种简单、灵活、高精度的信号分频方法,具有广泛的应用前景。

51单片机 波特率 32分频原因

51单片机波特率 32分频原因

在51单片机中,波特率(Baud Rate)是指串口通信中的数据传输速率,即每秒传输的比特数。

而32分频则是51单片机中用于设置波特率的一种分频方式。

在51单片机中,系统时钟频率通常为12MHz。

当需要设置特定的波特率时,需要根据系统时钟频率和分频系数来计算并设置相应的分频值。

为了得到32分频的原因,我们将以12MHz的系统时钟频率作为例子进行说明:

1.波特率计算:

•设定的波特率为9600,即每秒传输9600个比特。

•传输一个比特所需的时间为 1 / 9600 秒。

2.分频计算:

•通过将系统时钟频率除以需要的波特率,可以得到每个比特所需的时钟周期数。

•以12MHz系统时钟和9600波特率为例,每个比特所需的时钟周期数为 12,000,000 / 9,600 = 1250。

3.分频设置:

•51单片机中的串口通信模块使用定时器1来提供时钟源。

•分频系数决定了定时器的工作频率和计数周期。

•32分频即将每个比特所需的时钟周期数除以32,得到每个比特所需的计数周期数,即 1250 / 32 = 39.0625。

因此,设置32分频对应的计数值为39,以满足时钟源的分频要求,并实现所需的波特率。

需要注意的是,上述例子中的数字仅供示范目的,实际设置波特率时可能会有不同的计算值和分频设置选项,具体取决于系统时钟频率、波特率需求和单片机型号等因素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

linux 16550标准uart小数分频

Linux内核中的16550 UART驱动程序通常使用整数分频来配置波特率,而不是小数分频。

16550 UART芯片是一种常见的串行通信设备,它支持各种波特率。

在Linux内核中,可以使用以下命令来配置UART的波特率:

```shell

stty -F /dev/ttyS0 <波特率>

```

其中,`/dev/ttyS0`是串行端口设备文件,`<波特率>`是要配置的波特率值。

例如,要将波特率设置为9600,可以使用以下命令:

```shell

stty -F /dev/ttyS0 9600

```

如果你想在使用UART的自定义应用程序中进行小数分频来实现非标

准波特率,那么你需要编写自己的驱动程序或通过串口控制寄存器直接设置波特率。

在Linux内核中,UART驱动程序通常使用整数分频,因为它们更简单且适用于大多数应用场景。

请注意,具体的实现和配置可能因使用的硬件平台和驱动程序而有所不同。

建议参考相关硬件和驱动程序的文档以获取更准确的信息。