关于奇数分频和小数分频

任意数(整数、小数)分频器

任意数(整数、小数)分频器一、分频原理1.1偶数倍分频偶数倍分频通过计数器计数是很容易实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

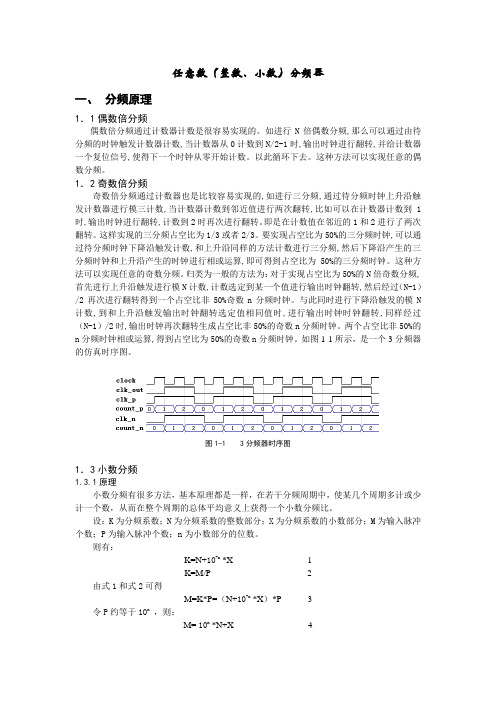

1.2奇数倍分频奇数倍分频通过计数器也是比较容易实现的,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

与此同时进行下降沿触发的模N 计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

如图1-1所示,是一个3分频器的仿真时序图。

图1-1 3分频器时序图1.3小数分频1.3.1原理小数分频有很多方法,基本原理都是一样,在若干分频周期中,使某几个周期多计或少计一个数,从而在整个周期的总体平均意义上获得一个小数分频比。

设:K为分频系数;N为分频系数的整数部分;X为分频系数的小数部分;M为输入脉冲个数;P为输入脉冲个数;n为小数部分的位数。

FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

FPGA分频与倍频的简单总结(涉及⾃⼰设计,调⽤时钟IP核,调⽤MMCM原语模块)原理介绍1、分频FPGA设计中时钟分频是重要的基础知识,对于分频通常是利⽤计数器来实现想要的时钟频率,由此可知分频后的频率周期更⼤。

⼀般⽽⾔实现偶数系数的分频在程序设计上较为容易,⽽奇数分频则相对复杂⼀些,⼩数分频则更难⼀些。

1)偶分频系数=时钟输⼊频率/时钟输出频率=50MHz/5MHz=10,则计数器在输⼊时钟的上升沿或者下降沿从0~(10-1)计数,⽽输出时钟在计数到4和9时翻转。

2)奇分频系数=50MHz/10MHz=5,则两个计数器分别在输⼊时钟的上升沿和下降沿从0~ (5-1)计数,⽽相应的上升沿和下降沿触发的输出时钟在计数到1和4时翻转,最后将两个输出时钟进⾏或运算从⽽得到占空⽐为50%的5分频输出时钟。

下图所⽰为50MHz输⼊时钟进⾏10分频和5分频的仿真波形2、倍频两种思路:PLL(锁相环)或者利⽤门延时来搭建注意:此仿真是利⽤FPGA内部电路延迟来实现的倍频需要在后仿真下才能看到波形,在⾏为仿真下⽆法得到输出波形。

⼀、时钟IP的分频倍频相关参数说明输⼊时钟:clk_in1(125MHz)输出时钟:clk_out1(50MHz),clk_out2(74.25MHz)则VCO Freq=1262.5MHz=clk_in1*CLKFBOUT_MULT_F/DIVCLK_DIVIDE=125*50.5/5clk_out1(50MHz)=VCO_Freq/Divide=1265.5/25.250clk_out2(74.25MHz)=VCO_Freq/Divide=1265.5/17⼆、MMCME4_ADVMMCME4是⼀种混合信号块,⽤于⽀持频率合成、时钟⽹络设计和减少抖动。

基于相同的VCO频率,时钟输出可以有单独的分频、相移和占空⽐。

此外,MMCME4还⽀持动态移相和分数除法(1)Verilog 初始化模板MMCME4_ADV #(.BANDWIDTH("OPTIMIZED"), // Jitter programming.CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKFBOUT_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN2_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT0_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT1_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT2_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT3_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128).CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT4_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT5_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT6_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).COMPENSATION("AUTO"), // Clock input compensation.DIVCLK_DIVIDE(1), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1.IS_CLKIN2_INVERTED(1'b0), // Optional inversion for CLKIN2.IS_CLKINSEL_INVERTED(1'b0), // Optional inversion for CLKINSEL.IS_PSEN_INVERTED(1'b0), // Optional inversion for PSEN.IS_PSINCDEC_INVERTED(1'b0), // Optional inversion for PSINCDEC.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999)..REF_JITTER2(0.0), // Reference input jitter in UI (0.000-0.999)..SS_EN("FALSE"), // Enables spread spectrum.SS_MODE("CENTER_HIGH"), // Spread spectrum frequency deviation and the spread type .SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns).STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked)MMCME4_ADV_inst (.CDDCDONE(CDDCDONE), // 1-bit output: Clock dynamic divide done.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6.DO(DO), // 16-bit output: DRP data output.DRDY(DRDY), // 1-bit output: DRP ready.LOCKED(LOCKED), // 1-bit output: LOCK.PSDONE(PSDONE), // 1-bit output: Phase shift done.CDDCREQ(CDDCREQ), // 1-bit input: Request to dynamic divide clock.CLKFBIN(CLKFBIN), // 1-bit input: Feedback clock.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.DADDR(DADDR), // 7-bit input: DRP address.DCLK(DCLK), // 1-bit input: DRP clock.DEN(DEN), // 1-bit input: DRP enable.DI(DI), // 16-bit input: DRP data input.DWE(DWE), // 1-bit input: DRP write enable.PSCLK(PSCLK), // 1-bit input: Phase shift clock.PSEN(PSEN), // 1-bit input: Phase shift enable.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement.PWRDWN(PWRDWN), // 1-bit input: Power-down.RST(RST) // 1-bit input: Reset);(2)本实验仿真所⽤参数配置说明及部分端⼝调⽤1、参数配置说明本实验通过输⼊时钟CLKIN1(150MHz),实现输出反馈时钟CLKFBOUT(150MHz)、输出时钟CLKOUT0(74.25MHz)、输出时钟CLKOUT1(74.25MHz)、输出时钟CLKOUT2(59.4MHz)、输出时钟CLKOUT3(49.5MHz)。

分频

在数字逻辑电路设计中,分频器是一种基本电路,通常用来对某个给定频率进行分频,从而得到所需的频率。

数字分频器一般有两大类:一类是脉冲波形均匀分布的分频器,即常规分频器;另一类是脉冲波形非分布均匀的分频器。

常规分频器只能进行整数或半整数分频,即分频倍数只能是整数或半整数。

但在某些应用场合,时钟源与所需的频率不一定成整数或半整数倍关系,这时就需要脉冲波形非均匀分布的分频器,这种分频器不仅能实现整数或半整数分频,还应能进行任意小数倍分频。

文献[1,2]给出了实现整数和半整数分频的常规分频器的两种设计方法,文献[3]则提出了一种可实现任意小数分频的设计方法——双模前置小数分频的实现方法。

在文献[1-3]研究的基础上,文献[4]总结归纳了实现任意数分频的设计方法。

在文献[1-3]研究的基础上,本文提出了一种改进的小数分频器设计方法,相对双模前置小数分频器,该方法使总体意义上与小数分频比等效的计数周期减小一半,并进一步减小了分频后得到的信号的相位抖动。

1整数和半整数分频对于N整数倍分频,可以方便地用模N的计数器来简单实现分频输出,其设计方法常用数字电子技术教程都有相关论述,这里就不赘述。

对于半整数分频N/2 (N为奇数),可以采用―脉冲周期剔除法‖来进行设计,即让触发前移半个周期的方式来剔除半个脉冲周期[4]。

假定输入计数脉冲周期为T,则当计数器计数到第(N+1)/2个周期时,只计数半个周期,即下一个计数循环到来时改变计数器的脉冲触发沿极性,这样一来,一个计数循环持续时间为计数脉冲周期的(N+1)/2-0.5 = N/2倍,即(N/2)T,从而输出信号频率为输入信号频率的1/(N/2)。

只要将整数和半整数分频器与一个T’触发器(二分频器)级联,就可以实现任意占空比为50%的整数倍分频。

2双模前置小数分频[3]2.1 分频原理在若干个分频周期中采取某种方法使某几个周期多计或少计一个脉冲,从而在整个计数周期的总体平均意义上获得一个小数分频比。

奇数分频器设计实验报告

奇数分频器实验报告1. 背景奇数分频器是一种电子电路模块,主要用于将输入的时钟信号进行分频,并输出比输入频率低的信号。

奇数分频器的主要应用场景包括计数器、时钟频率降低等。

2. 分析2.1 奇数分频器的工作原理奇数分频器通常采用了三角波类型的振荡器来产生输入时钟信号,并通过相应的逻辑门电路对时钟信号进行分频。

常见的奇数分频器包括模2、模4和模8等。

以模8奇数分频器为例,其工作原理如下:1.奇数分频器接收输入时钟信号,并通过一个振荡器产生三角波类型的输入信号。

2.输入信号经过逻辑门电路进行分频,产生分频后的信号。

3.输出信号经过滤波电路以去除杂散信号。

4.输出信号即为输入信号的1/8。

2.2 奇数分频器的主要特点奇数分频器的主要特点包括:•输入输出频率比例为奇数,如1/2、1/4、1/8等;•分频系数固定,无法调节;•输出信号的相位与输入信号相同;•输出信号的波形稳定,幅值与输入信号相同。

2.3 奇数分频器的设计要求为了设计一个稳定可靠的奇数分频器,需要满足以下要求:•选用合适的逻辑门电路,以实现所需的分频倍数;•设计合适的滤波电路,以去除杂散信号;•保证输入输出电路的匹配性,以确保信号的传输稳定性;•选择合适的元器件,以满足设计要求,并考虑成本和可获得性。

3. 实验步骤及结果3.1 实验步骤本实验以模8奇数分频器为例,设计了以下实验步骤:1.准备实验所需的元器件和设备。

2.搭建电路原型。

3.设计逻辑门电路,实现1/8分频。

4.测试电路,检查信号传输和波形稳定性。

5.调整滤波电路,优化输出信号质量。

6.记录实验数据。

3.2 实验结果在实验中,成功搭建了模8奇数分频器电路,并进行了测试。

实验结果表明,输入信号的频率为100kHz,输出信号的频率为12.5kHz,且波形稳定。

4. 结论在本次实验中,我们成功设计了一个模8奇数分频器,实现了1/8分频。

实验结果表明,输入信号经过分频后,输出信号的频率比例为奇数,并且波形稳定,符合设计要求。

小数分频器的拓展。

郑州航空工业管理学院毕业论文(设计)2012 届通信工程专业0813073 班题目基于FPGA分频器的设计姓名刘洋学号081307317指导教师张松炜职称讲师二О一二年五月二十日内容提要分频器是数字系统设计中的基本电路,在复杂数字逻辑电路设计中,根据不同设计的需要,会遇到偶数分频、奇数分频、半整数分频、小数分频等,有时要求等占空比,也有要求非等占空比。

在同一个设计中有时要求多种形式的分频,通常由计数器或计数器的级联构成各种形式的偶数分频和奇数分频,实现较为简单,但在某些场合下,时钟源与所需要的频率并不成整数关系,此时便需要采用小数分频器进行分频。

这时设计师希望有一种比较方便实用的设计方法,根据情况的需要,在实验室就能设计分频器并且可以马上检测使用,只需要更改分频系数而不修改其他器件或是电路板。

此次设计利用V erilog HDL硬件描述语言的设计方式,采用频率合成技术,通过QuartusⅡ5.0开发平台,使用Altera公司的FPGA器件,设计并实现了一种使小数分频“掺匀”更均匀的任意小数分频器。

只需在输入端更改分频系数,便可以得到所需的频率。

关键词分频器;整数;小数;分频系数; FPGAResearch and design of FPGA-based dividerAuthor: Liu Y ang Tutor: Zhang SongweiAbstractThe frequency divider is a basic circuit design of digital systems. In complex digital logic circuit design, according to different design needs, will meet the even number of odd divider, half integer divider, fractional divider and so on . Sometimes requirements so occupies emptiescompared, also have the required v. In the same design sometimes require various forms of points frequency, usually by a counter or counter of a cascade of all forms of frequency and odd number even points separate frequency, achieve comparatively simple,but in some cases, the clock frequency of the source and need not into integer relationship, at this time will need to adopt the decimal prescaler for points frequency.Designers hope to have a more convenient and practical design methods, according to the needs of the laboratory condition, can design frequency device and can immediately detection using, only need to change frequency coefficients and not modify other device or circuit board.This design using Verilog HDL hardware description language design methods, the frequency synthesis technology, through the Quartus Ⅱ5.0 development platform, and use of Altera company FPGA device, we design and implement a decimal points frequency "mixed well" more uniform any decimal prescaler. Just in the input frequency coefficient change points, and have a frequency required.KeywordsFrequency divider;Integer;Decimal,;Frequency coefficient ;FPGA目录内容提要 (1)目录 (III)第一章绪论 (1)1.1FPGA简介 (1)1.2选题的意义和目的 (3)1.3国内外应用现状及研究现状 (6)1.3.1应用现状 (6)1.3.2研究现状 (7)第二章整数分频器的设计及其分频原理 (10)2.1偶数分频 (10)2.1.1分频原理 (10)2.1.2软件仿真 (10)2.2奇数分频 (12)2.2.1分频原理 (12)2.2.2软件仿真 (13)第三章小数分频器的设计 (14)3.1小数分频器基本原理 (14)3.2小数分频器的设计方案及功能实现 (16)3.2.1半整数分频 (16)3.2.2任意小数分频器的设计与实现 (17)3.2.3小数分频器的应用 (20)致谢 (24)参考文献 (25)附录 (26)基于FPGA分频器的研究与设计081307317刘洋指导教师:张松炜讲师第一章绪论1.1FPGA简介FPGA是现场可编程门阵列的简称,是可编程逻辑器件(PLD)问世以来的第四代产品,适合于时序、组合等逻辑电路的应用。

fpga实现奇分频和偶分频的方法

fpga实现奇分频和偶分频的方法FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以通过重新编程来实现不同的功能。

在数字电路设计中,奇分频和偶分频是常见的需求,本文将介绍如何使用FPGA实现奇分频和偶分频的方法。

奇分频是指将输入信号的频率除以一个奇数,得到输出信号的频率。

而偶分频则是将输入信号的频率除以一个偶数,得到输出信号的频率。

在FPGA中,可以通过计数器和比较器来实现奇分频和偶分频。

我们需要明确需要实现的分频比例。

假设我们要实现一个2分频的功能。

对于奇分频,我们可以使用一个计数器来计数输入信号的上升沿或下降沿的个数,当计数器的值达到一定阈值时,输出一个脉冲信号,从而实现奇分频。

对于2分频,我们可以设置计数器的阈值为2,也就是每两个上升沿或下降沿输出一个脉冲信号。

在FPGA中,我们可以使用Verilog或VHDL等硬件描述语言来描述奇分频和偶分频的逻辑。

下面以Verilog为例,给出奇分频和偶分频的代码示例。

```verilogmodule OddDivider(input wire clk_in,output wire clk_outreg [1:0] count;wire tick;always @(posedge clk_in) begin if(count == 2'b00) begincount <= 2'b01;tick <= 1;end else if(count == 2'b01) begin count <= 2'b10;tick <= 0;end else begincount <= 2'b00;tick <= 0;endendassign clk_out = tick; endmodulemodule EvenDivider(input wire clk_in,output wire clk_outreg [2:0] count;wire tick;always @(posedge clk_in) beginif(count == 3'b000) begincount <= 3'b001;tick <= 1;end else if(count == 3'b001) begin count <= 3'b010;tick <= 0;end else if(count == 3'b010) begin count <= 3'b011;tick <= 0;end else begincount <= 3'b000;tick <= 0;endendassign clk_out = tick; endmodule在上面的Verilog代码中,OddDivider模块实现了奇分频的功能,EvenDivider模块实现了偶分频的功能。

数字系统设计hdl课后答案

数字系统设计hdl课后答案【篇一:数字系统设计与verilog hdl】ss=txt>(复习)eda(electronic design automation)就是以计算机为工作平台,以eda软件工具为开发环境,以pld器件或者asic专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子cad(computer aided design)2.电子cae(computer aided engineering)3.eda(electronic design automation)eda技术及其发展p2eda技术的应用范畴1.3 数字系统设计的流程基于fpga/cpld的数字系统设计流程1. 原理图输入(schematic diagrams )2、硬件描述语言 (hdl文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(rtl)◆逻辑综合:rtl级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到pld器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或hdl语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对cpld器件而言,产生熔丝图文件,即jedec文件;对fpga器件则产生bitstream位流数据文件p8仿真(simulation)功能仿真(function simulation)时序仿真(timing simulation)仿真是对所设计电路的功能的验证p9编程(program)把适配后生成的编程文件装入到pld器件中的过程,或称为下载。

通常将对基于eeprom工艺的非易失结构pld器件的下载称为编程(program),将基于sram工艺结构的pld器件的下载称为配置(configure)。

VERILOG 分频原理

VERILOG 分频原理众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

因此很多招聘单位在招聘时往往要求应聘者写一个分频器(比如奇数分频)以考核应聘人员的设计水平和理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于奇数分频和小数分频

小数分频

举例,对于8.7分频,先进行几次8分频,后进行几次9分频,这样平均下来就是小数分频,至于具体几次就是靠公式了:

这其中K就是8.7,N等于8,-n就是-1,X就是7。

这样,其中就会有X(也就是7)次9分频,按照平均,就有3次8分频(87-7*9)/8。

还有一个问题,就是从N 分频切换到N + 1 分频和从N + 1 分频切换到N 分频都会产生一个随时间增长的相位移, 如果简单的先进行3 次8 分频后做7 次9 分频将会产生很大的相位

波动。

解决方法是将这两种分频混合。

怎样混合就有要牵扯到另一个控制逻辑:每进行分频,就用10减去小数部分(10-7),这个结果值累加,小于10的次数进行N+1

分频,然后进行N分频,但是每次超过又要减去10重新累加:

这个过程有一个变量控制。

奇数分频

N倍奇数分频,要使占空比为50%,以如下思路实现:

A、以原时钟周期的N倍作为一个处理周期;(用计数器计数的作用)

B、生成占空比为N/2 :N/2+1(除法取整)的波形;(以计数器值采样)

C、将B生成的波形相移原时钟的半个周期;(用负沿打的作用)

D、若高电平占N/2宽,输出将B和C的波形相或;若高电平占N/2+1宽,输出将B和C 的波形相与

具体代码如下:

module odddiv(rst,clk,clkout);

parameter N=3; //计数器的位数N的最大计数值要大于或等于M parameter M=7; //要分频的模,取奇数

input rst;

input clk;

output clkout;

reg tempp,tempn;

//assign clkp=clk;

//assign clkn=~clk;

reg [N-1:0] count;

always @(negedge rst or posedge clk)

if(!rst)

begin

count<=0;

tempp<=0;

end

else

begin

count<=count+1;

if(count==M/2)

tempp<=1;

else if(count==M-1)

begin

tempp<=0;

count<=0;

end

end

always @(negedge rst or negedge clk)

if(!rst)

tempn<=0;

else

tempn<=tempp;

assign clkout=tempp|tempn;

endmodule。