新型高速高精度CMOS预充电比较器

一种高精度动态CMOS比较器的设计与研制

种 高精度 动态 C MOS比较器 ,采用 二级 差分 比较和 一级动 态 正反馈 lth结构实现 了高比较 精度 。预增益 和 L th a c ac

级 的应 用 降低 了 功 耗 。设 计 中 充 分 考 虑 了 工 艺 离 散 性 和 使 用 环 境 温 度 与 电 源 变 化 的 影 响 ,保 证 了 成 品 率 和 电 路 在 变 化

工作环 境下性 能指标 的实现 。仿真 结果表 明 ,设计 的 高速 动态 比较器 L B ( es Sg i cn i)为士 .5 S L at inf a t t i B 01 mV,输入 动 态范 围为 D( 为地 电压 , D为 电源 电压 ) ,相应 于 l 4位 比较精 度 。功耗 62 mW,工 作频率 36 z .8 .MH 。电路

境 的适 应 能 力 。该 比较器 可 以应 用于 高 精 度模 数 转 换 器 中 ,实 现 1 4位 以上 的模 数 转换 。

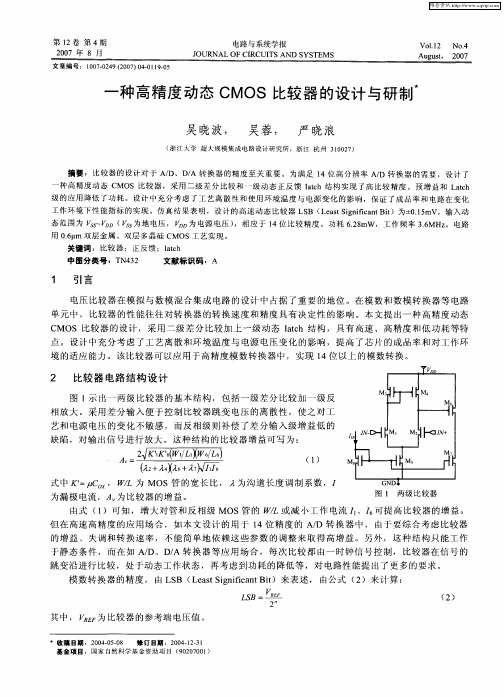

2 比较 器 电路 结 构 设 计

图 l 出一 两级 比较 器 的基 本 结构 ,包 括 一 级 差 分 比较 加 一级 反 示 相放 大 。采 用 差 分输 入 便 于 控 制 比较 器 跳 变 电压 的离 散性 ,使 之 对 工 艺和 电源 电压 的变 化 不敏 感 ,而 反 相级 则 补 偿 了差 分输 入 级增 益 低 的 缺 陷 ,对 输 出信 号 进 行放 大 。 这种 结 构 的 比较 器 增益 可 写为 :

但 在 高 速 高 精 度 的应 用 场 合 ,如 本 文设 计 的 用 于 l 精 度 的 A/ 转 换 器 中 ,由于 要 综 合 考虑 比较 器 4位 D 的增 益 、 失调和 转 换 速 率 ,不 能 简 单地 依 赖 这 些 参 数 的调 整 来 取 得 高 增 益 。 另外 ,这 种 结 构 只 能工 作 于静 态 条 件 ,而在 如 A/ D、D/ 转 换 器 等 应 用 场 合 ,每 次 比较 都 由一 时钟 信 号 控 制 , 比较器 在 信 号 的 A 跳 变 沿 进 行 比较 ,处于 动 态 工作 状态 ,再 考 虑 到功 耗 的 降低 等 ,对 电路 性 能提 出了 更 多 的要 求 。

一种与比较器延迟无关的高精度CMOS振荡器

一种与比较器延迟无关的高精度CMOS振荡器秦松;王磊【摘要】提出了一种采用0.18 μm CMOS工艺制作的浮动初始电压(FIV)型高精度振荡器电路.浮动初始电压(FIV)技术用以消除比较器延迟对振荡器频率的影响,同时利用器件的匹配特性使得振荡频率仅和RC相关.此外通过适当的温度系数补偿,此振荡器可以在-40 ~125℃达到+0.5%的精度,并且仅占0.035 mm2的芯片面积.【期刊名称】《电子科技》【年(卷),期】2017(030)005【总页数】4页(P94-97)【关键词】浮动初始电压;RC振荡器;CMOS;比较器延迟【作者】秦松;王磊【作者单位】帝奥微电子有限公司研发部,上海201103;帝奥微电子有限公司研发部,上海201103【正文语种】中文【中图分类】TN432当前,片上基准振荡器被广泛应用于各种集成电路中,如生物医学传感器、MCU、无线传感器网络、DDR接口、SoC等[1-2]。

阻容型振荡器,包括张弛振荡器,通常可以通过标准CMOS工艺实现。

晶体振荡器能够达到10 ppm的精度级别,然而由于晶体无法集成,所以晶体振荡器的体积大,成本高并且起振慢。

LC振荡器可以实现和晶振相近的精度和相位噪声,然而其功耗却在数百mW以上,并不适合当前大部分设备对低功耗的要求。

此外,传统的补偿型RC振荡器,如环形振荡器或含反馈环路的张弛振荡器,尽管也可以实现约1%的精度,但其电路结构比较复杂,导致功耗和面积较大[3-7]。

本文对传统张弛振荡器进行了改进,提出了浮动初始电压(FIV)技术,用简单的电路结构实现了高精度的振荡器,同时兼具低功耗和占用较小芯片面积的优点。

讨论了传统张弛振荡器存在的问题,同时分析了浮动初始电压振荡器的工作原理以及各种非理想因素对振荡器精度的影响。

1.1 传统张弛振荡器图1是一种常用的传统张弛振荡器结构[8-9]。

该振荡器通过给电容充放电实现振荡:(1)t1阶段,电容C通过Iref充电;(2)当VC电压超过Vref时,比较器翻转并使放电开关导通,给电容C放电;(3)当电容C放电到Vref以下,比较器再次翻转,放电开关关闭,电容开始充电。

一种用于流水线ADC的CMOS比较器的设计

一种用于流水线ADC的CMOS比较器的设计

周前能;向正煌

【期刊名称】《数字技术与应用》

【年(卷),期】2015(000)011

【摘要】本文基于SMIC018μmCMOS工艺设计了一种应用于流水线ADC的开关电容预放大锁存比较器。

开关电容预放大比较器整体功耗比静态比较器少,且具有速度快,踢回噪声小的特点。

且通过验证分析,可以知道开关电容预放大比较器能够很好的满足流水线子ADC对比较器的要求。

【总页数】1页(P142-142)

【作者】周前能;向正煌

【作者单位】重庆邮电大学光电工程学院重庆400065

【正文语种】中文

【中图分类】TP311

【相关文献】

1.适用于SAR ADC的CMOS比较器的设计 [J], 裴晓敏

2.用于低噪声CMOS图像传感器的流水线ADC设计及其成像验证 [J], 邓若汉;徐星;王洪彬;余金金;陈世军;陈永平

3.一种用于流水线ADC的CMOS比较器的设计 [J], 周前能;向正煌

4.一种用于流水线结构ADC中改进速度/功耗比的CMOS动态比较器(英文) [J], 刘珂;杨海钢

5.一种用于流水线ADC的高速电压比较器 [J], 殷湛;郭立;杨吉庆

因版权原因,仅展示原文概要,查看原文内容请购买。

高速电压比较器芯片

高速电压比较器芯片一、高速电压比较器芯片的工作原理高速电压比较器芯片是一种用于比较两个输入电压大小的电子器件。

它通常由一个差分输入级、一个比较器和输出缓冲器组成。

差分输入级将两个输入电压进行差分放大,以便于比较器进行比较。

比较器根据两个输入电压的大小关系输出高低电平信号,而输出缓冲器则对比较器的输出信号进行适当的放大和缓冲,以便于驱动后级电路。

高速电压比较器芯片的工作原理主要基于比较器内部的电压传输特性。

当输入电压发生变化时,差分输入级会将其转换为差分信号,并传送到比较器的输入端。

如果输入电压达到某个阈值时,比较器将输出高电平或低电平信号。

这个阈值通常由比较器的内部电路和电源电压决定。

二、高速电压比较器芯片的性能特点高速电压比较器芯片具有以下性能特点:1.高速响应:高速电压比较器芯片通常具有快速的响应时间,可以在毫秒甚至纳秒级别内完成电压比较。

这使得它在高速模拟-数字转换器(ADC)、波形生成和采样电路等应用中具有广泛的应用。

2.精度和线性度:高速电压比较器芯片通常具有较高的精度和线性度,可以用于高精度的测量和控制系统。

此外,一些高速电压比较器芯片还具有温度补偿功能,可以减少温度对精度的影响。

3.低功耗:随着技术的发展,高速电压比较器芯片的功耗越来越低,使得它在电池供电的应用中具有更长的使用寿命。

此外,低功耗设计还可以降低散热要求,使系统更加紧凑和可靠。

4.兼容多种接口:为了满足不同的应用需求,高速电压比较器芯片可以与多种接口兼容,如SPI、I2C等。

这使得它可以与其他数字器件方便地连接和通信,从而简化了电路设计和系统集成。

5.可靠性高:高速电压比较器芯片通常具有较高的可靠性,可以在恶劣的环境条件下稳定工作。

此外,一些高速电压比较器芯片还具有过热保护、过流保护等功能,可以有效地保护系统免受过载、短路等故障的损害。

三、高速电压比较器芯片的应用场景高速电压比较器芯片在各种应用场景中都发挥着重要的作用。

一种新型的高性能CMOS电流比较器电路

一种新型的高性能CMOS电流比较器电路1 引言随着VLSI 特征尺寸的不断缩小和高速?低功耗应用需求的不断增加,电流型电路逐渐受到广泛的重视。

与传统的电压型电路相比,电流型电路具有面积小、速度快、可在低电压下工作和与数字CMOS 集成电路工艺完全兼容的特点,成为取代电压型电路的一种有效方式,现已经广泛应用于A /D 变换器、滤波器和神经网络的VL S I 实现中。

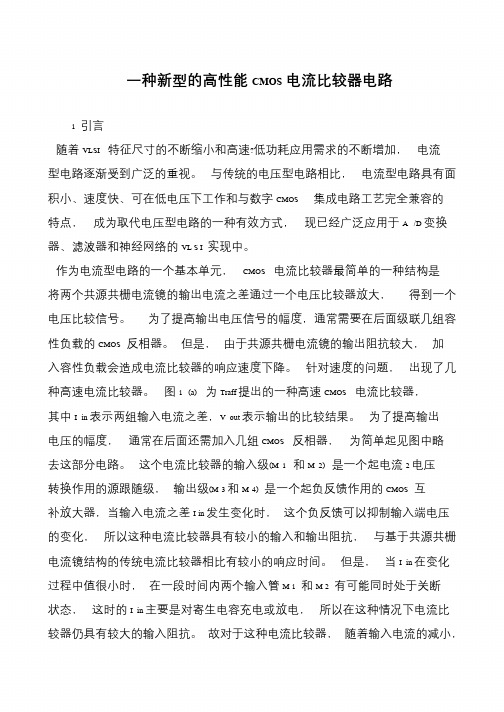

作为电流型电路的一个基本单元,CMOS 电流比较器最简单的一种结构是将两个共源共栅电流镜的输出电流之差通过一个电压比较器放大,得到一个电压比较信号。

为了提高输出电压信号的幅度,通常需要在后面级联几组容性负载的CMOS 反相器。

但是,由于共源共栅电流镜的输出阻抗较大,加入容性负载会造成电流比较器的响应速度下降。

针对速度的问题,出现了几种高速电流比较器。

图1 (a) 为Traff 提出的一种高速CMOS 电流比较器,其中I in 表示两组输入电流之差,V out 表示输出的比较结果。

为了提高输出电压的幅度,通常在后面还需加入几组CMOS 反相器,为简单起见图中略去这部分电路。

这个电流比较器的输入级(M 1 和M 2) 是一个起电流2 电压转换作用的源跟随级,输出级(M 3 和M 4) 是一个起负反馈作用的CMOS 互补放大器,当输入电流之差I in 发生变化时,这个负反馈可以抑制输入端电压的变化,所以这种电流比较器具有较小的输入和输出阻抗,与基于共源共栅电流镜结构的传统电流比较器相比有较小的响应时间。

但是,当I in 在变化过程中值很小时,在一段时间内两个输入管M 1 和M 2 有可能同时处于关断状态,这时的I in 主要是对寄生电容充电或放电,所以在这种情况下电流比较器仍具有较大的输入阻抗。

故对于这种电流比较器,随着输入电流的减小,。

一种高性能的CMOS电压比较器设计

一 种 高性能 的 CMOS电压 匕较器 设计

文 /苟欣 杨 鸣

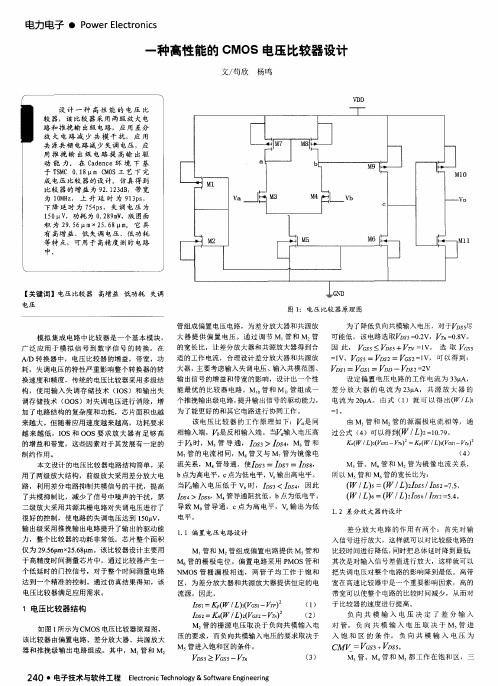

设 计 一 种 高性 能 的 电压 比 较 器 , 该 比较 器 采 用 两 级 放 大 电 路 和推 挽输 出级 电路,应 用 差分 放 大 电路 减 少 共 模 干 扰 , 应 用 共 源共 栅 电路 减 少失调 电压,应 用 推 挽 输 出 级 电路 提 高 输 出驱 动 能 力 。 在 Cadence环 境 下 基 于 TSMC 0.18 m CMOS工 艺 下 完 成 电压 比较 器 的设 计 。仿真 得 到 比较 器 的增 益 为 92.12 3dB,带 宽 为 10MHz, 上 升 延 时 为 91 3ps, 下 降延 时 为 7 54ps,失 调 电压 为 1 50 u V, 功 耗 为 0.289mW,版 图 面 积 为 29.56 gtm x 2 5.68 um。 它 具 有 高增 益、低 失调 电压、低 功耗 等特 点 ,可用 于 高精度 测 时 电路 中。

大 器提供 偏置 电压。通 过调 节 M 管 和 M,管 的宽长 比,让差分放大器和共源放大器得到合 适 的工作 电流 ,合理设计差分放大器和共源放 大器 ,主要考虑输入失调 电压、输入共模范 围、

可能低 ,该 电路 选取Vos5=O.2V,Vr,=0.8V。 因 此 , Vas5 Vos5+ VrN=lV。 选 取 VGs5 = IV。Vas5= 2= Vas2=IV, 可 以得 到 : VDSI= VGS1: D—Vvs2=2V

调 存储技术 (OOS)对失调 电压进行消 除,增 个推挽输 出级 电路 ,提升输 出信号的驱动 能力 , 电流 为 20gA。由式 (1)就 可 以得 出( /L)I

一种高速高精度CMOS电流比较器

针对输入失调问题 , 文献 [] 6 提出 了一种补偿方法 。

可是这种方法虽然从一定程度上降低 了输入失调 , 却 因为需要另加补偿 电路 , 使得 比较器 的电路形式

变得复杂 , 且引入了因调零而产生的延时。文献[] 7 报导的双输入结构的电流比较器 , 在文献[] 6 的基础

上从一定程度上进一步 降低 了延时 , 提高 了精度 。 然而, 比较器的偏置电路复杂且不对称 , 该 容易受工

艺偏差影 响, 引起较大的输入失调。另外 , 这个 比较 器的输入阻抗较大 , 在输入电流变化较小时会产生 较大的延时 。针对 以上 电路 的缺点, 本文提出了一

Hale Waihona Puke 结构由文献[] 5提出 , 如图 1 所示, 为简化起见 , 面 后

省去了反相器 。它是将两个共源共栅 电流镜 的输 出

电流之差通过 C S MO 反相器 比较放大 , 得到最后 的

维普资讯

第2 9卷 第 4期 20 0 6年 1 2月

电 子 器 件

Chn s or a fEe to vcs ie eJ un lo lcrn Deie

V0. 9 No. 12 4 De . 0 6 c20

A v lHi h S e d a d Hi h Ac u a y CM OS Cu r n mp r t r No e g p e n g c r c r e tCo a a o

EEA oC: 5 0 2 7 D

一

种高速高精度 C MO S电流 比较 器

柳娟娟 , 冯全源

( 西南交 通大学 微 电子研究所 , 成都 603 ) 101

摘

要: 针对传统 电流 比较器速度慢, 精度低 等问题 , 提出了一种新型 C S电流 比较器电路。我们采用 C S MO MO 工艺

一种高速高精度的CMOS比较器的电路

2009 年第 4 期

江 利, 等: 一种高速高精度的 CMOS 比较器的电路

45

根据 A/ D 转换器的不同性能, 出现了多种结构 形式的比较器电路。就工作速度而 言, 有低速、高 速和超高速; 就信号输入方式, 有单端输 入和双端 差分输 入 2 种。本 文提出 一种高 速高精 度的 CMOS 比较器的设计, 采用三级差分比较加上一级 动态 Lat ch 结构, 具有高速、高精 度和低功 耗等特 点。运用了一种先进的输入失调消除方法, 使比较 器的精度不受输入失调电压的影响, 从而实现了输 入失调 电压的 消除。同时, 对 该比 较器 的电 路结 构、增益、带宽、锁存时间常数也进行了分析。

第 2 卷第 4 期 2009 年 12 月

上海电气 技术 JOU RNAL OF SH ANGH AI ELECTR IC TECH NOLOGY

文章编号: 1674- 540X( 2009) 04- 044- 04

Vol. 2 No. 4 Dec. 2009

一 种 高 速 高 精 度 的 CMOS 比 较 器 的 电 路

换的关键器件, 也得到了广泛地应用。高速比较器 作为高速 A/ D 转换器的核心器件, 得到了很大地发 展。比较器的精度和速度对 A/ D 转换器的性能起 着至关重要的作用, 因此, 要实现高速 A/ D 转换期: 200 9- 1 0- 0 9 作者简介: 江 利( 1 976- ) , 男, 博士 研究生, 主要从事集成电路设计研究工作, E- mail: r iver0 556@ 1 63. com

Ke y words: high speed comparat or; CMOS comparat or; input offset cancellat ion; lat ch

高精度CMOS基准电压源设计

高精度CMOS基准电压源设计

宁江华

【期刊名称】《电子世界》

【年(卷),期】2017(000)014

【摘要】基准源是模拟集成电路中的基本单元之一,它在高精度ADC、DAC、SOC等电路中起着重要作用,基准源的精度直接控制着这些电路的精度.本文阐述了一个基于带隙基准结构的低功耗、低温度系数、高电源抑制比的CMOS基准电压源.该电路采用SMIC 0.18μm标准CMOS工艺实现,并用Spectre进行了仿真,得到理想的设计结果.

【总页数】2页(P117-118)

【作者】宁江华

【作者单位】贵阳学院电子与通信工程学院

【正文语种】中文

【相关文献】

1.一种高精度BiCMOS带隙基准电压源的实现 [J], 刘敏侠;李福德

2.高精度CMOS带隙基准电压源电路设计 [J], 刘鸿雁

3.一种新型高精度低压CMOS带隙基准电压源 [J], 陈迪平;吴旭;黄嵩人;季惠才;王镇道

4.一种低成本高精度CMOS基准电压源设计 [J], 肖海鹏;马卓;张民选;张正旭

5.一种高精度CMOS带隙基准电压源设计 [J], 沈菊;宋志棠;刘波;封松林;朱加兵因版权原因,仅展示原文概要,查看原文内容请购买。

一种高速低功耗迟滞CMOS比较器的分析与设计

为了防止 Vin 的变化范围过大而引起的前置放大级的一个支路截止,采用了二极管接法的 MC1 和 MC2 作为钳位 [7], 使 M31 管的漏端和 M41 管的漏端之间的压差总是小于 VTHN。 可减小比较器的失调。 M1 和 M2 管的尺寸决定了本级的跨导和输入电容, 进而决定了本级的增益和响应速度。 而前置放 大级的性能又直接决定了整个比较器电路的速度和敏感度。 2.2 正反馈级的分析与设计 正反馈级由 M5、 M6、 M7、 M8、以及 M9、 M10、 M11、 M12 管组成。 M5 和 M8 管采用二极管 连接的方式给 M6、 M7 和 M9、 M10 管提供稳定的栅压。通过把 M6 和 M7 管的栅极交叉互联,实现 正反馈,以提高本级增益。 M9、M10 和 M11、 M12 管的作用是为正反馈级提供一个缓冲 [8,9]。以实现 该级预加载和存储。

文章分析设计了一种具有内部迟滞效应的高速低功耗cmos比较器该比较器采用前置放大级正反馈级和输出驱动级级联的结构实现了对增益速度和功耗的优化

第 14 卷 第 3 期 2009 年 6 月

文章编号: 1007-0249 (2009) 03-0052-04

电路与系统学报 JOURNAL OF CIRCUITS AND SYSTEMS

[1] [2] [3] [4] [5] [6] [7] [8] [9]

测试环境温度 工作电压 直流功耗 (20MHZ) 响应速度 输入敏感电压 输入电压范围

R Jacob Baker, Harry W Li, David E Boyce. CMOS: Circuit Design, Layout, and Simulation [M]. China Machine Press, P525-528. Yukawa A. A CMOS 8-Bit High-Speed AD Converter IC [J]. Solid-State Circuits IEEE Journal of, 1985, 20(3): 775-779. Figueiredo P M, Vital J C. Low kickback noise techniques for CMOS latched comparators [A]. Circuits and Systems, 2004. ISCAS '04. Proceedings of the 2004 International Symposium on [C]. 2004-05, 1: I-537-40. Lourans Samid, Patrick Volz, Yiannos Manoli. A Dynamic Analysis of a Latched CMOS Comparator [A]. IEEE. Circuits and Systems, 2004. ISCAS '04. Proceedings of the 2004 International Symposium on [C]. 2004-05, 1: I-181-4. Yang Wen-rong, Wang Jia-dong. Design and Analysis of a High-speed Comparator in a Pipelined ADC [A]. IEEE High Density packaging and Microsystem Integration, 2007.International Symposium on [C]. 2007-07. 1-3. Hadidi K, Temes G C. A High Resolution, Low Offset And High Speed Comparator [A]. Custom Integrated Circuits Conference, 1992, Proceedings of the IEEE 1992 [C]. 1992-05. 16.1.1-16.1.4. 李杰 , 吴光林 , 吴建辉 , 戚韬 . 一种低失调 CMOS 比较器设计 [J]. 电路与系统学报 , 2007, 12(1). Guermaz M B, Bouzerara L, Slimane A, Belaroussi M T, Lehouidj B, Zirmi R. High Speed Low Power CMOS Comparator for Pipeline ADCs [A]. IEEE Microelectronics, 2006 25th International Conference on [C]. 2006-05. 428-431. Razavi B, Wooley B A. Design techniques for high-speed, high-resolution comparators [J]. Solid-State Circuits, IEEE Journal of, 1992, 27, (12): 1916-1926.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技2009年第22卷第5期电子#电路收稿日期:2008-12-10作者简介:王江燕(1981-),女,硕士,助教。

研究方向:信息与信号处理。

裴 杰(1982-),男,助教。

研究方向:航空电子。

新型高速高精度C MOS 预充电比较器王江燕1,裴 杰2(11空军第一航空学院航空电子工程系,河南信阳 464000;21空军第一航空学院军械工程系,河南信阳 464000)摘 要 采用预充电技术和合理的反馈结构设计了一种比较器,与一般的比较器相比,该电路具有更快的响应速度,更高的精度和灵敏度,较小的失调电压和较低的功耗。

该比较器采用典型的T S M C 016L m 硅C M OS 工艺模型,利用Cadence 进行模拟仿真。

结果表明,比较器的延时为01069L s ,精度为20mV,在5V 电源电压下,功耗为017765W 。

关键词 预充电;正反馈;响应速度;失调电压中图分类号 TN 432 文献标识码 A 文章编号 1007-7820(2009)05-031-03A NovelH igh -Speed H igh -A ccuracy C MO S P recharge Com paratorW ang Jiangyan 1,Pei Jie2(11D epart m ent of E l ectronic Eng i neeri ng ,The F irst Av iat i on College of A irf orce ,X inyang 464000,Chi na ;21Depart ment of O rdnance Eng i neering ,The F irst A viation Co llege of A i rforce ,X i nya ng 464000,China)Abstract A novel fra me co m par ator is desi gne d by the pre -c harge techno l ogy and reasonable feedbac k fra m e ,wh i ch has the advantages over the traditional co mparator of greater response speed ,h i gher acc uracy and se nsit i v ity ,lo w er o ffset volta ge and lo wer dissipati on .Sm i ulated using Cadence w ith the standard T S M C016L m S iCMO S mode,lthe co m parator has a transfer del ay tm i e of 01069L s ,accur acy of 20mV and po werd issi pation of 017765W at 5V.K ey words pre -charge ;positive feedbac k ;response speed ;offsets vo ltage在模数转换和许多具有特定功能的模拟电路中,经常会用到比较器。

比较器的重要性能指标包括:工作速度、比较精度、功耗、输入失调电压和正反馈产生的踢回噪声等[1]。

随着MOS 技术的不断发展,比较器的速度得到了很大的提高,但是由于MOS 器件之间的失配误差,使得在一定工艺条件下实现高速高精度比较困难。

为了减小输入失调电压和踢回噪声,提高比较器的速度和精度,通常采用由预放大级、判断级和输出级构成的比较器。

这种结构的比较器具有低输入失调电压和低踢回噪声的特性[1]。

其中,预放大级可以提高输入信号的灵敏度,并且隔开输入信号与来自正反馈级的噪声,使得比较器的性能得到大大的改善。

文中设计了一种加入预充电技术的正反馈比较器,其主要优势是提高了比较器的工作速度和比较精度,并有效地降低了失调电压和功耗。

1 电路结构设计文中介绍的比较器总体电路,如图1所示。

该比较器主要由预放大级、判断级和输出级构成。

该比较器的预放大级采用有源负载的差分放大器。

它的主要作用是将比较电压转换成比较电流,并将其进行差分放大。

由于三极管与一般的MOS 管相比,其失调电压比较小,并且对于电压的变化反应更灵敏,所以该比较器利用三极管Q 1和Q 2的基极作为电压比较信号的输入端,以此来电子#电路新型高速高精度C MO S 预充电比较器减小该比较器的失调电压并提高其精度,比较器的输入电容由Q 1和Q 2决定。

MOS 管M 17和M 20的栅极输入为输出信号Out 和XOu,t 构成正反馈环路,用来提高比较器的工作速度。

MOS 管M 18和M 19为预充电管,其栅极电压始终为偏置电压V B I AS ,因此,M 18和M 19的漏极(即Q 1和Q 2的集电极)电压始终被抬高到某一电位(假设为分别为V P 1和V P 2)。

当输入变化时,由于V P 1、V P 2的电位始终保持在一定的电位,处于最高最低电压之间,因此输出电压对输入电压变化的响应速度会更快。

次级放大管由MOS 管M 6和M 7组成。

图1 比较器整体电路图该比较器的判断级是由MOS 管M 11~M 14组成具有正反馈的电流比较器,它能分辨出很小的输入信号差,而且具有回滞效应可以抑制信号上的噪声[1-3]。

预放大级将电压转换成电流信号,输出到判断级的电流比较电路中,判断级的电路图,如图2所示。

图2 比较器判断级电路该电路将M 11和M 14的栅极交叉互联,构成正反馈,提高判断电路的增益。

假定I o 1远远大于I o 2,则MOS 管M 11和M 12导通,M 13和M 14截止。

假设其放大系数B 11=B 12=B o 1,B 13=B 14=B o 2,其中,B x =L o C ox W x /L x ,则V o 2约为0V;因为V o 1=2I o 1/B o 1+V T HN ,所以V o 1=2I o 1/B o 1+V THN 。

如果I o 2增大,I o 1减小,当M 12的漏源电压等于M 8的V T HN 时,电路的输出状态发生转换,此时M 13管分得本来流过M 11的电流,这样M 11的漏源电压开始下降并最终导致M 12截止。

在I o 2增大,I o 1减小过程中,当M 12的漏源电流增大到某一数值时,M 12的漏源电压也会上升到V THN ,这个临界的电流值为该电流的临界点,也是输出电压发生转换的临界点,即I o 2=B o 12(V o 1-V THN )2=B o 2B o 1I o 1(1)状态变换后,致使M 12截止,M 13导通。

对于I o 1增大,I o 2减小的情形,其转换点可以由式(2)表示I o 2=B o 2B o 1I o 1(2)其中,比较电流I o 1、I o 2之间的关系为I o 1+I o 2=W 6W 5I s(3)I o 1与输入的比较电压之间的关系为I o 1=W 6W 5g m 2(V I -V REF )+I s2(4)其中,g m 为Q 1或Q 2的跨导,I s 为差分三极管的尾电流。

比较器的输出级的主要作用是将判断级的输出信号转换成逻辑电平(0V 或5V ),它是由MOS 管M 9、M 10、M 15和M 16组成差分比较放大器再加两级推挽反相器构成。

由判断级输出的电压V o 1和V o 2分别加到NMOS 管M 16和M 10的栅极,经过差分比较放大器之后再经过两级推挽反相器的整形之后输出信号Out 和XOu,t 输出信号又加入输入端构成正反馈环路,提高了比较器的翻转速度。

比较器的精度主要受输入失调电压和比较器的增益与影响。

失调电压V off =V o ff1+V off2/A V 01,由于比较器预放大级的输入端是三极管,所以其失调电压V off1较小;由于在预放大级加入了正反馈,差分信号经过有源差分放大器之后,大大提高了其增益,所以V off2/A V 01也较小。

考虑图1中预放大级输出节点V G 5的增益,可以利用小信号等效电路,如图3所示进行分析,求解出电压增益G m 为新型高速高精度C M OS 预充电比较器电子#电路图3 小信号等效电路G m =V OV I N =-g O 1g m 5+1/r Q 1+1/r O 5=g Q 1(1/g m 5+r Q 1+r O 5)(5)仿真结果,如图4所示,增益约为34dB 。

图4 差分放大器的增益2 仿真结果采用典型的TS M C 016L m 硅C MOS 工艺模型,利用Cadence 进行模拟仿真。

比较器采用,如图1所示的结构,电源电压为5V,偏置电流I 1为516L A,三极管Q 1、Q 2采用典型NP N 模型,MOS 管的参数,如表1所示。

表1 比较器M OS 管参数表C MO S W /L m L /L m M 1/M 21210M 3/M 41010M 5/M 61010M 7/M 81010M 91010M 10610M 11/M 1451420M 12/M 1351410M 1581410M 16610M 17/M 20610M 18/M 1951410M 21~M 2351410非门1NM O S 112016非门1PM OS 2016非门2NM O S 112016非门2PM OS2016仿真结果表明:比较器的延时为01069L s ,精度为20mV,如图5所示。

在5V 电源电压条件下,功耗017765W 。

图5 比较器的输出波形文中设计的比较器,其反馈环路和预充电结构不仅可以提高比较器的响应速度,而且对比较器的精度也产生了很大的影响,若去掉反馈环路和预充电结构后,其精度也大大降低。

为了能够更好地说明反馈环路和预充电结构对比较器的精度的影响,在比较器的两个输入端分别加入中心电平在215V 的正弦信号和三角波信号,从仿真结果可以看出,加入反馈环路和预防大结构前比较器精度约为60mV,加入后为约20mV,精度提高了40mV 。

如图6所示,其中,(a)为输入比较信号,(b )为未加入反馈环路和预充电结构时的输出信号,(c)为加入反馈环路和预充电结构时的输出信号。

图6 比较器的输出波形(下转第46页)电子#电路星载DC/DC转换器辐射损伤预警方案设计图4星载DC/DC转换器辐射预警系统框图4结束语文中采用新兴的电子故障预测与健全管理(eP HM)方法,设计基于P WM的星载DC/DC转换器辐射损伤预警方案,可以在辐射致P WM损伤使基准电压漂移达到预警值时发出警报,为启动备用件赢得超前时间,避免灾难性故障发生。