基于FPGA与PC串口自收发通信-Verilog

基于fpga 的toe 系统设计与实现-概述说明以及解释

基于fpga 的toe 系统设计与实现-概述说明以及解释1.引言1.1 概述概述FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它可以根据用户的需求进行灵活的逻辑电路重构。

TOE(TCP/IP Offload Engine)系统是一种通过硬件加速的方式来提高网络性能的解决方案。

本文将介绍基于FPGA的TOE系统的设计与实现。

随着互联网的普及和发展,网络通信已经成为人们生活中不可或缺的一部分。

然而,传统的软件实现方式在高速网络环境下往往无法满足大规模数据通信的需求。

为了克服这样的问题,TOE系统应运而生。

TOE系统通过将TCP/IP协议的处理功能从通用计算机系统中分离出来,并放置在专用硬件中,以提高网络数据包的处理能力。

而FPGA作为一种灵活、可重构的芯片,能够满足TOE系统中对于高性能、低延迟的硬件加速需求。

本文将分析FPGA技术的基本原理和特点,探讨TOE系统的设计原理以及FPGA在TOE系统中的应用。

通过对TOE系统的设计与实现进行总结与展望,将提供对于基于FPGA的TOE系统设计的理论和实践指导。

通过本文的研究,我们可以深入了解基于FPGA的TOE系统在优化网络性能方面的巨大潜力,以及其在适应未来高速网络发展的前景。

我们相信,基于FPGA的TOE系统将在未来网络通信领域发挥重要作用,并为网络性能的提升做出积极的贡献。

1.2文章结构文章结构部分的内容可以按照以下方式编写:1.2 文章结构本文分为引言、正文和结论三个部分。

引言部分概述了文章的背景和目的,提供了对整篇文章的整体理解。

首先,概述了基于FPGA的TOE系统设计与实现的主题,并简要介绍了TOE系统和FPGA技术的背景和重要性。

接着,给出了整篇文章的结构和章节划分,以便读者能够清晰地了解每个部分的内容。

最后,说明了本文的目的,即通过对FPGA在TOE系统设计与实现中的应用进行探讨,促进TOE系统的发展和未来的研究。

基于FPGA的PID控制器研究与实现共3篇

基于FPGA的PID控制器研究与实现共3篇基于FPGA的PID控制器研究与实现1近年来,随着现代控制理论的快速发展,PID控制器已经成为了广泛应用的经典算法之一。

PID控制器通过比较目标值和实际值之间的误差,反馈调整控制器的输出信号,实现对被控对象的精确控制。

PID控制器不仅简单且易于实现,而且良好的性能使其在自动控制领域中得到广泛应用。

而FPGA技术的高速并列运算、低延迟和高精度特性,为PID控制器的实时性和精度提供了重要的支持。

本文旨在通过基于FPGA技术的PID控制器研究与实现,探索这一领域的新思路和新方法。

一、PID控制器的基本原理PID控制器基于被控对象的输出值和标准值之间的误差进行控制。

该算法包括比例(P)、积分(I)和微分(D)三个参数。

其中,比例参数是通过直接调整被控量的大小,使其不断靠近标准值;积分参数修正了长期误差,通过积分误差实现偏差的修正;微分参数反映了被控物理系统的动力学特性,通过比率误差的变化率,实现对被控量的快速响应。

二、基于FPGA的PID控制器实现方案基于FPGA的PID控制器比传统的PC或单片机进行控制有更快的响应速度和更低的延迟。

基于FPGA的PID控制器将提供实时数据采集和高速算法处理的结合。

其实现方案基本步骤如下:1. 选择合适的FPGA芯片并进行开发环境搭建,比如选用Xilinx的Vivado软件进行开发。

2. 实现PID控制器的最重要的步骤是设计算法。

基于FPGA的PID控制器主要分为两个部分:控制循环和存储器组件。

控制循环模块主要将控制信号输出给被控对象,从而实现对被控对象的控制;存储器组件则使用存储器来保存被控量及反馈量等数据。

3. 在FPGA芯片上进行系统的相关硬件配置并进行PID算法的编程。

4. 根据实际需要,实现PID控制器与外部设备通信及数据传输,比如串口通讯、以太网通讯等。

三、实验结果与分析为了验证基于FPGA的PID控制器的实现效果和精度,我们进行了一系列实验。

verilog编写的uart程序

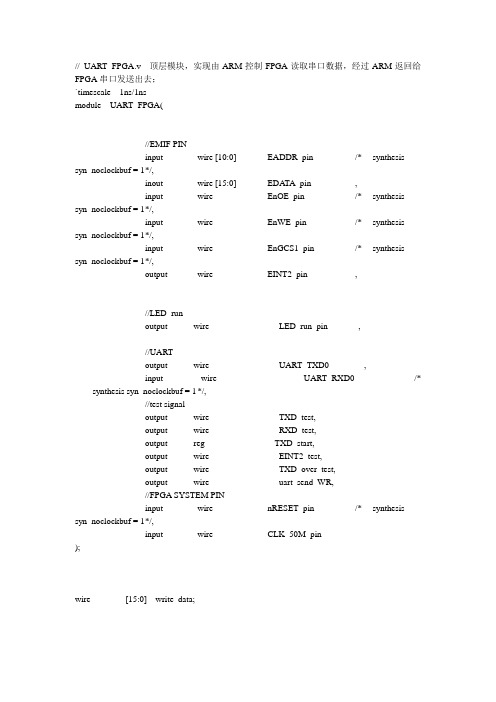

// UART_FPGA.v 顶层模块,实现由ARM控制FPGA读取串口数据,经过ARM返回给FPGA串口发送出去;`timescale 1ns/1nsmodule UART_FPGA(//EMIF PINinput wire [10:0] EADDR_pin /* synthesis syn_noclockbuf = 1 */,inout wire [15:0] EDATA_pin ,input wire EnOE_pin /* synthesis syn_noclockbuf = 1 */,input wire EnWE_pin /* synthesis syn_noclockbuf = 1 */,input wire EnGCS1_pin /* synthesis syn_noclockbuf = 1 */,output wire EINT2_pin ,//LED_runoutput wire LED_run_pin ,//UARToutput wire UART_TXD0 ,input wire UART_RXD0 /* synthesis syn_noclockbuf = 1 */,//test signaloutput wire TXD_test,output wire RXD_test,output reg TXD_start,output wire EINT2_test,output wire TXD_over_test,output wire uart_send_WR,//FPGA SYSTEM PINinput wire nRESET_pin /* synthesis syn_noclockbuf = 1 */,input wire CLK_50M_pin);wire [15:0] write_data;//-------------------DSP ARM uart to EMIF---------------------- reg [7:0] ARM_DSP_data;wire [7:0] DSP_ARM_data;reg uart_send_WR_reg;//reg [7:0] T_data;//reg [1:0] TXD_start_cnt;wire [7:0] R_data;wire R_ready;reg [2:0] UART_INT_cnt;wire TXD_over;wire [1:0] baud_select;reg [12:0] baud_devide;//wire clkrec;parameter baud_9600 = 5208; //50M/9600 parameter baud_19200 = 2604;parameter baud_38400 = 1302;parameter baud_115200 = 434;assign TXD_test = UART_TXD0;assign RXD_test = UART_RXD0;assign EINT2_test = EINT2_pin;assign TXD_over_test=TXD_over;/*--------------Program start-------------------*//*----------baud select------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginbaud_devide <= 'h1FFF;endelsebegincase ( baud_select )'d0 : baud_devide <= baud_9600 ;'d1 : baud_devide <= baud_19200 ;'d2 : baud_devide <= baud_38400 ;'d3 : baud_devide <= baud_115200 ;endcaseendend/*----------INT generator------------*/always @( negedge nRESET_pin or posedge R_ready )beginif( !nRESET_pin )beginARM_DSP_data <= 8'd0;endelsebeginARM_DSP_data <= R_data;endendalways @( negedge nRESET_pin or negedge R_ready or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginUART_INT_cnt <= 3'd5;endelse if( !R_ready )beginUART_INT_cnt <= 3'd0;endelse if( UART_INT_cnt < 3'd5 )beginUART_INT_cnt <= UART_INT_cnt + 1'b1;endassign EINT2_pin = ( UART_INT_cnt >= 3'd1 && UART_INT_cnt <= 3'd4 ) ? 1'b0 : 1'b1 ;/*---------------DSP to ARM data---------------*/always@(negedge nRESET_pin or posedge CLK_50M_pin) //当接收了一个数据后,把数据加1后发回PC机,注意串口一个一个数据发beginif( !nRESET_pin )beginuart_send_WR_reg <= 1'b0;TXD_start <= 1'b0;endelse if( uart_send_WR_reg != uart_send_WR )beginif( TXD_over )beginTXD_start <= 1'b1;uart_send_WR_reg <= uart_send_WR;endendelsebeginTXD_start <= 1'b0;endend//----------------EMIF read ,fpga TO ARM---------------------------EMIF_R EMIF_R_M(.EADDR_pin (EADDR_pin ),.EDA TA_pin (EDA TA_pin ),.EnOE_pin (EnOE_pin ),.EnGCS1_pin (EnGCS1_pin ),.write_data (write_data ),.ARM_DSP_data (ARM_DSP_data ),.nRESET_pin (nRESET_pin )// .CLK_50M_pin (CLK_50M_pin )//----------------EMIF write,ARM to fpga---------------------------EMIF_W EMIF_W_M(.EADDR_pin (EADDR_pin ),.EDA TA_pin (EDATA_pin ),.EnWE_pin (EnWE_pin ),.EnGCS1_pin (EnGCS1_pin ),//uart.DSP_ARM_data (DSP_ARM_data ),.uart_send_WR (uart_send_WR ),.write_data (write_data ),.baud_select (baud_select ),//LED run.LED_run_pin (LED_run_pin ),.nRESET_pin (nRESET_pin )// .CLK_50M_pin (CLK_50M_pin ) );UART_rec UART_rec_M (//input.RXD (UART_RXD0 ),.baud_devide (baud_devide ),//output.R_data (R_data ),.R_ready (R_ready ),//FPGA sys pin.nRESET_pin (nRESET_pin ),.CLK_50M_pin (CLK_50M_pin));UART_txd UART_txd_M (//input.TXD_start (TXD_start ),.T_data (DSP_ARM_data ),.baud_devide (baud_devide ),//output.TXD (UART_TXD0 ),.TXD_over (TXD_over ),//FPGA sys pin.nRESET_pin (nRESET_pin ),.CLK_50M_pin (CLK_50M_pin));Endmodule// UART_rec.v`timescale 1ns/1nsmodule UART_rec (//inputRXD,baud_devide,//outputR_data,R_ready,//FPGA sys pinnRESET_pin,CLK_50M_pin);input wire RXD;input wire [12:0] baud_devide;output reg [7:0] R_data;output reg R_ready;input wire nRESET_pin;input wire CLK_50M_pin;reg [1:0] RXD_sync;reg [2:0] RXD_cnt;reg RXD_bit;reg [3:0] rec_bit_cnt;//reg [8:0] baud_16_reg;reg [12:0] baud_cnt;reg [8:0] baud_16_cnt;wire baud_tick_16;wire baud_tick;wire [11:0] baud_devide_2;wire [8:0] baud_devide_16;/*----------Program start------------*/assign baud_devide_2 = baud_devide / 2;assign baud_devide_16 = baud_devide / 16;/*--------------baud 16 devided clk used in sample-----------*/ always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginbaud_16_cnt <= 'd0;endelsebeginif( baud_16_cnt < baud_devide_16 )beginbaud_16_cnt <= baud_16_cnt + 1'b1;endelsebeginbaud_16_cnt <= 'd0;endendendassign baud_tick_16 = ( baud_16_cnt == baud_devide_16 );//--------baud clk used in receiving data-------always @( negedge nRESET_pin or posedge CLK_50M_pin )beginif( !nRESET_pin )beginbaud_cnt <= 'd0;endelsebeginif( !R_ready )beginif( baud_cnt < baud_devide - 1'b1 )beginbaud_cnt <= baud_cnt + 1'b1;endelsebeginbaud_cnt <= 'd0;endendelsebeginbaud_cnt <= 'd0;endendendassign baud_tick = ( baud_cnt == baud_devide_2 );/*-----------jitter filter--------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin )beginif( !nRESET_pin )beginRXD_sync <= 2'd0;endelsebeginRXD_sync <= {RXD_sync[0], RXD};endendalways @( negedge nRESET_pin or posedge baud_tick_16 ) beginif( !nRESET_pin )beginRXD_cnt <= 3'd7;endelsebeginif( RXD_sync[1] && RXD_cnt != 3'd7 )beginRXD_cnt <= RXD_cnt + 1;endelsebeginif( ~RXD_sync[1] && RXD_cnt != 3'd0 )beginRXD_cnt <= RXD_cnt - 1;endendendendalways @( negedge nRESET_pin or posedge baud_tick_16 ) beginif( !nRESET_pin )beginRXD_bit <= 1'b1;endelsebeginif( RXD_cnt == 3'd7)beginRXD_bit <= 1'b1;endelse if( RXD_cnt == 3'd0 )beginRXD_bit <= 1'b0;endendend/*---------------receive data cnt---------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginR_ready <= 1'b1;rec_bit_cnt <= 4'd0;endelsebeginif( R_ready )beginrec_bit_cnt <= 4'd0;if( !RXD_bit )beginR_ready <= 1'b0;endendelse if( baud_tick )beginif( rec_bit_cnt < 4'd9 )beginrec_bit_cnt <= rec_bit_cnt + 1'b1;R_ready <= 1'b0;endelsebeginrec_bit_cnt <= 4'd0;R_ready <= 1'b1;endendendendalways @( negedge nRESET_pin or posedge baud_tick ) beginif( !nRESET_pin )beginR_data <= 8'd0;endelse if( !R_ready )beginif( rec_bit_cnt == 0 )beginR_data <= 8'd0;endelsebeginif( rec_bit_cnt >= 4'd1 && rec_bit_cnt<= 4'd8 )R_data[rec_bit_cnt - 1'b1 ] <= RXD_bit;endendendendmodule// UART_TXD.v`timescale 1ns/1nsmodule UART_txd (//inputbaud_devide,TXD_start,T_data,//outputTXD,TXD_over,//FPGA sys pinnRESET_pin,CLK_50M_pin);input wire TXD_start;input wire [7:0] T_data;input wire [12:0] baud_devide;output reg TXD;output reg TXD_over;input wire nRESET_pin;input wire CLK_50M_pin;//regs & wireswire baud_tick;//reg baud_ctrl;reg [3:0] T_state;reg [7:0] T_data_reg;reg [12:0] baud_cnt;/*----------Program start---------------*//*-----------------Baud generator------------------------*/assign baud_tick = ( baud_cnt == baud_devide - 1'b1 );always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginbaud_cnt <= 'd0;endelse if( baud_cnt < baud_devide - 1'b1 )beginbaud_cnt <= baud_cnt + 1'b1;endelsebeginbaud_cnt <= 'd0;endend/*----------transmit state machine---------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginT_state <= 4'd0;endelsebegincase(T_state)4'd0: if(TXD_start) T_state <= 4'd1;4'd1: if(baud_tick) T_state <= 4'd2; // 开始位04'd2: if(baud_tick) T_state <= 4'd3; // bit 04'd3: if(baud_tick) T_state <= 4'd4; // bit 14'd4: if(baud_tick) T_state <= 4'd5; // bit 24'd5: if(baud_tick) T_state <= 4'd6; // bit 34'd6: if(baud_tick) T_state <= 4'd7; // bit 44'd7: if(baud_tick) T_state <= 4'd8; // bit 54'd8: if(baud_tick) T_state <= 4'd9; // bit 64'd9: if(baud_tick) T_state <= 4'd10; // bit 74'd10: if(baud_tick) T_state <= 4'd0; // 停止位1default: if(baud_tick) T_state <= 4'd0;endcaseendendalways @(negedge nRESET_pin or posedge baud_tick ) beginif( !nRESET_pin )beginTXD <= 1'b1;T_data_reg <= 8'd0;endelsebegincase(T_state)// 4'd0: TXD <= 1'b1;4'd1: beginTXD <= 1'b0;T_data_reg <= T_data;end4'd2: TXD <= T_data_reg[0];4'd3: TXD <= T_data_reg[1];4'd4: TXD <= T_data_reg[2];4'd5: TXD <= T_data_reg[3];4'd6: TXD <= T_data_reg[4];4'd7: TXD <= T_data_reg[5];4'd8: TXD <= T_data_reg[6];4'd9: TXD <= T_data_reg[7];4'd10: TXD <= 1'b1;default: TXD <= 1'b1;endcaseendend//assign TXD = TXD;always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginTXD_over <= 1'b0;endelsebeginif( T_state ==4'd0 )TXD_over <= 1'b1;elseTXD_over <= 1'b0;endendendmodule。

C# 实现PC与PLC(三菱Fx系列)串口通信

}

}

//The return code of the method is displayed by the hexadecimal.

txt_ReturnCode.Text = String.Format("0x{0:x8} [HEX]", iReturnCode);

C# 实现 PC 与 PLC(三菱 Fx 系列)串口通信 串口是计算机上一种非常通用的设备通信协议。 大多数计算机包含两个基于 RS-232 的串口。 PLC 采用的是三菱公司的 FX1N©系列产品,支持的串口通信协议是 422,不支持 232 协议, 所以要 调用第三方提供的动态库实现 PC 与 PLC 之间串口通信。 1.首先到三菱官网

读写 PLC 常用方法。

4. 主要代码示例

int iReturnCode;

//Return code

//Displayed output data is cleared.

ClearDisplay();

//

//Processing of Open method

//

try

{

//获取端口号

var item =

lpcom_ReferencesProgType.ActUnitType = 0x0f; //设置为 FX1N(C) lpcom_ReferencesProgType.ActCpuType = 0x207; //set PROTOCOL_SERIAL lpcom_ReferencesProgType.ActProtocolType = 0x04; // Specify the baud rate for serial communication. lpcom_ReferencesProgType.ActBaudRate = 9600; //设置端口号 Specify the connection port number of personal computer. lpcom_ReferencesProgType.ActPortNumber = COMPort;

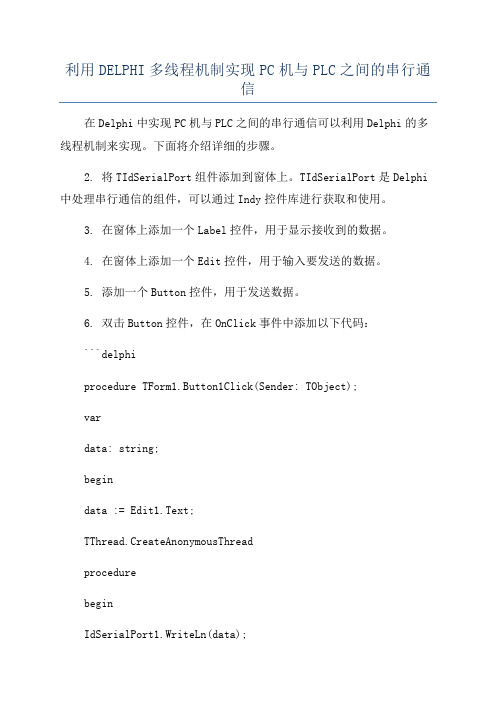

利用DELPHI多线程机制实现PC机与PLC之间的串行通信

利用DELPHI多线程机制实现PC机与PLC之间的串行通信在Delphi中实现PC机与PLC之间的串行通信可以利用Delphi的多线程机制来实现。

下面将介绍详细的步骤。

2. 将TIdSerialPort组件添加到窗体上。

TIdSerialPort是Delphi 中处理串行通信的组件,可以通过Indy控件库进行获取和使用。

3. 在窗体上添加一个Label控件,用于显示接收到的数据。

4. 在窗体上添加一个Edit控件,用于输入要发送的数据。

5. 添加一个Button控件,用于发送数据。

6. 双击Button控件,在OnClick事件中添加以下代码:```delphiprocedure TForm1.Button1Click(Sender: TObject);vardata: string;begindata := Edit1.Text;TThread.CreateAnonymousThreadprocedurebeginIdSerialPort1.WriteLn(data);.Startend;```上述代码创建了一个匿名线程,在线程中使用IdSerialPort1.WriteLn方法向串口发送数据。

7. 双击TIdSerialPort1的OnRxChar事件,在事件处理程序中添加以下代码:```delphiprocedure TForm1.IdSerialPort1RxChar(Sender: TObject; Count: Integer);vardata: string;begindata := IdSerialPort1.ReadLn;TThread.Queue(nil,procedurebeginLabel1.Caption := data;end```上述代码在串口接收到数据时,使用IdSerialPort1.ReadLn方法将接收到的数据读取到data变量中,并使用TThread.Queue方法将显示更新的代码放到主线程中执行,以避免主线程阻塞。

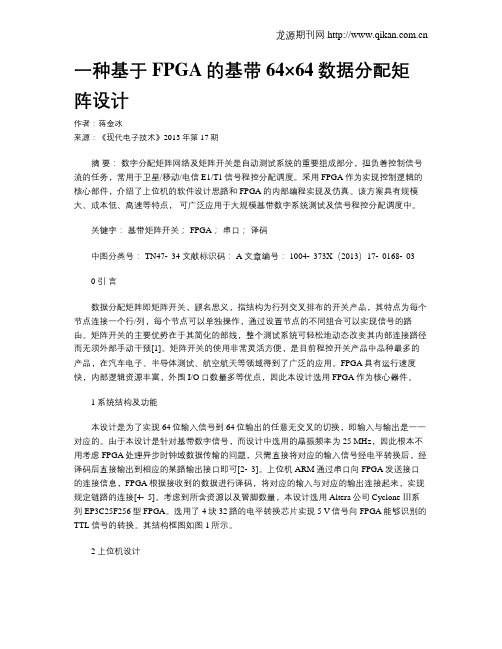

一种基于FPGA的基带64×64数据分配矩阵设计

一种基于FPGA的基带64×64数据分配矩阵设计作者:蒋金冰来源:《现代电子技术》2013年第17期摘要:数字分配矩阵网络及矩阵开关是自动测试系统的重要组成部分,担负着控制信号流的任务,常用于卫星/移动/电信E1/T1信号程控分配调度。

采用FPGA作为实现控制逻辑的核心部件,介绍了上位机的软件设计思路和FPGA的内部编程实现及仿真。

该方案具有规模大、成本低、高速等特点,可广泛应用于大规模基带数字系统测试及信号程控分配调度中。

关键字:基带矩阵开关; FPGA;串口;译码中图分类号: TN47⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)17⁃0168⁃030 引言数据分配矩阵即矩阵开关,顾名思义,指结构为行列交叉排布的开关产品,其特点为每个节点连接一个行/列,每个节点可以单独操作,通过设置节点的不同组合可以实现信号的路由。

矩阵开关的主要优势在于其简化的部线,整个测试系统可轻松地动态改变其内部连接路径而无须外部手动干预[1]。

矩阵开关的使用非常灵活方便,是目前程控开关产品中品种最多的产品,在汽车电子、半导体测试、航空航天等领域得到了广泛的应用。

FPGA具有运行速度快,内部逻辑资源丰富,外围I/O口数量多等优点,因此本设计选用FPGA作为核心器件。

1 系统结构及功能本设计是为了实现64位输入信号到64位输出的任意无交叉的切换,即输入与输出是一一对应的。

由于本设计是针对基带数字信号,而设计中选用的晶振频率为25 MHz,因此根本不用考虑FPGA处理异步时钟域数据传输的问题,只需直接将对应的输入信号经电平转换后,经译码后直接输出到相应的某路输出接口即可[2⁃3]。

上位机ARM通过串口向FPGA发送接口的连接信息,FPGA根据接收到的数据进行译码,将对应的输入与对应的输出连接起来,实现规定链路的连接[4⁃5]。

考虑到所含资源以及管脚数量,本设计选用Altera公司Cyclone Ⅲ系列EP3C25F256型FPGA。

基于FPGA的EPON系统中新型OLT的设计

图 4 OLT 处理控制帧模块软件实现流程图

高。 另外,光脉宽控制也是 OLT 的系统模块中的关键 技术,后续可做重点研究。 实验结果表明,本 OLT 的系 统模块工作在速率下, 符合目前通过的协议的规范。 电路在宽温度范围内能稳定工作,并能很好地控制发 射光功率。

参考文献:

[1] 原荣.宽带光接入网[M].北京:电子工业出版社,2003. [2] 陈 强.EPON 系 统 的 研 究 与 实 现[D].硕 士 论 文.浙 江 :浙 江 工 业 大 学 , 2004 [3] 陈伟,杨申,黄秋元.EPON 系 统 OLT 光 接 收 模 块 设 计 及 关 键 技 术[J]. 武 汉 理 工 大 学 学 报 ,2005 ,27(3):1-4. [4] H AN S, M AN- SEOP L. Burst- mode Pena lty o f AC-Coupled Optical Receivers Optimized for 8B /10B Line Code [ J]. IEEE Pho ton ics Techno logy Le tters, 2004,16( 7):1724- 1726. [5] H AN S, LEE M S. AC - coupled Burst-mode Optical Receiver Employing 8B /10B Coding [ J]. E lec tron ics Lette rs, 2003, 39 ( 21): 523- 524. [6] Media Access Control Parameters, Physical Layers and Management Parameters for Subscriber Access Networks[S].IEEE Draft P802. /D1. 9, 2003 ( 6):509.

FPGA的UART完整设计

FPGA的UART完整设计FPGA(现场可编程门阵列)是一种可编程逻辑设备,可以用于实现各种数字系统。

其中一个常见的应用是实现串行通信接口,如UART(通用异步收发器)。

UART是一种用于串行数据传输的通信协议,常用于连接计算机和外部设备(如传感器、显示器等)。

UART通信有两个关键部分:发送和接收。

在FPGA中,我们可以使用电平转换器、计数器和状态机等模块来设计和实现UART。

首先,我们需要设计发送模块。

发送模块的任务是将数据从FPGA发送到外部设备。

以下是发送模块的设计步骤:1.配置串行通信参数:确定波特率、校验位和停止位等参数。

2.设计数据缓冲区:创建一个FIFO(先进先出)缓冲区,用于存储要发送的数据。

3.生成波特率时钟:使用计数器和时钟分频器来生成适当速率的时钟信号。

4.串行化数据:将数据从缓冲区读取,并将其转换为串行比特流。

5.加入校验位和停止位:根据配置的参数,在数据的末尾添加校验位和停止位。

6.发送数据:将串行的比特流发送到外部设备。

接下来,我们需要设计接收模块。

接收模块的任务是从外部设备接收数据并传输到FPGA。

以下是接收模块的设计步骤:1.配置串行通信参数:确定波特率、校验位和停止位等参数,与发送模块保持一致。

2.生成波特率时钟:使用计数器和时钟分频器来生成适当速率的时钟信号。

3.接收数据:从外部设备接收串行比特流。

4.分析校验位和停止位:验证接收到的数据的校验位和停止位是否正确。

5.并行化数据:将串行比特流转换为并行数据,并存储到接收缓冲区中。

6.处理接收到的数据:根据串行通信协议,处理接收到的数据。

在设计中,需要考虑以下事项:1.时钟同步:确保发送端和接收端使用相同的时钟源,并进行合适的时序调整,以保持数据的稳定性和正确性。

2.缓冲区管理:使用FIFO缓冲区来处理发送和接收的数据,以防止数据丢失和冲突。

3.错误处理:根据串行通信协议,实现适当的错误检测和纠正机制,以确保数据的完整性和正确性。

基于fpga的can总线设计与实现

一、概述CAN(Controller Area Network)总线是一种广泛应用于汽车、工业控制和其他领域的串行通信协议,具有高可靠性、抗干扰能力强等特点。

在现代汽车电子控制系统中,CAN总线承担着重要的通信任务,因此CAN总线的设计与实现显得尤为重要。

二、FPGA技术与CAN总线1. FPGA(Field Programmable Gate Array)是一种集成了大量可编程逻辑和存储单元的集成电路芯片,具有灵活、可编程的特点,能够实现各种数字逻辑功能。

2. 利用FPGA技术可以实现CAN总线的设计与实现,通过FPGA的可编程性,能够灵活地实现CAN总线控制器、接口电路等功能。

三、基于FPGA的CAN总线设计1. CAN总线协议分析a. CAN总线采用了差分信号传输,具有抗干扰能力强的特点。

b. CAN总线具有消息优先级和通信速率可变等特性,需要实现相关的控制逻辑。

c. CAN总线的数据帧格式、错误处理、时序要求等方面需要仔细设计。

2. CAN总线控制器设计a. CAN总线控制器需要实现消息的发送和接收逻辑,包括数据帧封装、发送/接收处理等功能。

b. 利用FPGA的可编程逻辑可以实现CAN总线控制器的灵活控制逻辑。

3. CAN总线接口电路设计a. CAN总线需要与外部设备进行通信,因此需要设计CAN总线接口电路,包括收发芯片、电平转换电路等。

四、基于FPGA的CAN总线实现1. CAN总线控制器的编程实现a. 基于Verilog或VHDL等硬件描述语言实现CAN总线控制器的硬件逻辑。

b. 实现消息的发送、接收逻辑,以及错误处理、时序控制等功能。

2. CAN总线接口电路的设计与调试a. 设计CAN总线接口电路,与外部设备连接,包括选择合适的收发芯片、电平转换电路。

b. 进行接口电路的调试,保证CAN总线与外部设备能够正常通信。

五、基于FPGA的CAN总线应用与展望1. CAN总线在汽车电子控制系统中的应用a. CAN总线在汽车电子控制系统中承担着重要的通信任务,包括发动机控制、仪表控制、车身控制等。

基于FPGA的BLVDS高速通信总线设计

B V S总 线上数 据的接 收 、 送 , LD 发 以及数 据 的缓存 。 实验 结 果表 明 , 总线通信 速度 快 、 定 、 该 稳 可靠 。

b o usc mmu c to S h g s e d. tb e a d r l b e niai n i ih—p e sa l n e i l . a

Ke v wor : VDS FPGA; CB 1y u ;L ds BL ; P a o t VDS

测试总线是传输信号或者信息的公共路径 , 是连 接各 硬件 模块 的基 础 。它保证 各种 命令 和测试 数据 在 互 连设备 问准确 无 误地 传 输 。 随着 科 学技 术 的发 展 ,

关 键词 : L D ; P A;C B V S F G P B布线 ;V S L D

中 图分类 号 : P 3 T 36

文 献标识 码 : A

文章编 号 :0 0—8 2 ( 0 2 0 0 7 0 10 8 9 2 1 ) 7— 0 6— 6

De i n o sg fBLVDS H i h- e d Co m u c to sBa e o g Sp e m nia in Bu s d n FPGA

基于 F G P A的 B V S L D 高速通信 总线设计

黄 誉 ,王新 民 , 从 潮 姚

70 2 ) 119 ( 西北工业大学 自动化学 院, 陕西 西 安

摘 要 : 试 总线是测 试 系统 中 的一 个 重要 环 节 , 准 确 传输 信 号 的 关键 。详 细介 绍 了 L D 测 是 V S与 B V S L D 技 术 , 此基础 上论 述 了 B V S总线布置设 计 、C 在 LD P B布 线设 计 、 据格 式 设计 及 通信 背板 设计 , 数 并提 出

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA与PC串口自收发通信 实现的功能如题,就是FPGA里实现从PC接收数据,然后把接收到的数据发回去。 使用的是串口UART协议进行收发数据。上位机用的是通用的串口调试助手。 发送数据的波特率可选9600bps,19200bps,38400bps,57600bps,115200bps等, 是可调的。发送格式为:1bit起始位,8bit数据,1bit停止位,无校验位。 以下的代码有比较详细的注释,经过下载验证,存在误码率(<5%),仅供学习! 代码如下: (顶层模块): module my_uart_top(clk,rst_n,rs232_rx,rs232_tx); input clk; // 50MHz主时钟 input rst_n; //低电平复位信号 input rs232_rx; // RS232接收数据信号 output rs232_tx; // RS232发送数据信号

wire bps_start; //接收到数据后,波特率时钟启动信号置位 wire clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点 wire[7:0] rx_data; //接收数据寄存器,保存直至下一个数据来到 wire rx_int; //接收数据中断信号,接收到数据期间始终为高电平 //---------------------------------------------------- speed_select speed_select( .clk(clk), //波特率选择模块,接收和发送模块复用,不支持全双工通信

.rst_n(rst_n), .bps_start(bps_start), .clk_bps(clk_bps) ); my_uart_rx my_uart_rx( .clk(clk), //接收数据模块

.rst_n(rst_n), .rs232_rx(rs232_rx), .clk_bps(clk_bps), .bps_start(bps_start), .rx_data(rx_data), .rx_int(rx_int) ); my_uart_tx my_uart_tx( .clk(clk), //发送数据模块

.rst_n(rst_n), .clk_bps(clk_bps), .rx_data(rx_data), .rx_int(rx_int), .rs232_tx(rs232_tx), .bps_start(bps_start) ); endmodule

module speed_select(clk,rst_n,bps_start,clk_bps); input clk; // 50MHz主时钟 input rst_n; //低电平复位信号 input bps_start; //接收到数据后,波特率时钟启动信号置位 output clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点

parameter bps9600 = 5207, //波特率为9600bps

bps19200 = 2603, //波特率为19200bps

bps38400 = 1301, //波特率为38400bps

bps57600 = 867, //波特率为57600bps

bps115200 = 433; //波特率为115200bps

parameter bps9600_2 = 2603, bps19200_2 = 1301,

bps38400_2 = 650,

bps57600_2 = 433,

bps115200_2 = 216;

reg[12:0] bps_para; //分频计数最大值 reg[12:0] bps_para_2; //分频计数的一半 reg[12:0] cnt; //分频计数 reg clk_bps_r; //波特率时钟寄存器

//---------------------------------------------------------- reg[2:0] uart_ctrl; // uart波特率选择寄存器 //----------------------------------------------------------

always @ (posedge clk or negedge rst_n) begin if(!rst_n) begin uart_ctrl <= 3'd0; //默认波特率为9600bps

end else begin case (uart_ctrl) //波特率设置

3'd0: begin

bps_para <= bps9600; bps_para_2 <= bps9600_2; end 3'd1: begin

bps_para <= bps19200; bps_para_2 <= bps19200_2; end 3'd2: begin bps_para <= bps38400; bps_para_2 <= bps38400_2; end 3'd3: begin

bps_para <= bps57600; bps_para_2 <= bps57600_2; end 3'd4: begin

bps_para <= bps115200; bps_para_2 <= bps115200_2; end default: ; endcase end end

always @ (posedge clk or negedge rst_n) if(!rst_n) cnt <= 13'd0; else if(cnt//波特率时钟计数启动

else cnt <= 13'd0; always @ (posedge clk or negedge rst_n) if(!rst_n) clk_bps_r <= 1'b0; else if(cnt==bps_para_2 && bps_start) clk_bps_r <= 1'b1; // clk_bps_r高电平为接收或者发送数据位的中间采样点

else clk_bps_r <= 1'b0; assign clk_bps = clk_bps_r; endmodule

module my_uart_rx(clk,rst_n,rs232_rx,clk_bps,bps_start,rx_data,rx_int); input clk; // 50MHz主时钟 input rst_n; //低电平复位信号 input rs232_rx; // RS232接收数据信号 input clk_bps; // clk_bps的高电平为接收或者发送数据位的中间采样点 output bps_start; //接收到数据后,波特率时钟启动信号置位 output[7:0] rx_data; //接收数据寄存器,保存直至下一个数据来到 output rx_int; //接收数据中断信号,接收到数据期间始终为高电平

//---------------------------------------------------------------- reg rs232_rx0,rs232_rx1,rs232_rx2; //接收数据寄存器,滤波用 wire neg_rs232_rx; //表示数据线接收到下降沿

always @ (posedge clk or negedge rst_n) begin if(!rst_n) begin rs232_rx0 <= 1'b1; rs232_rx1 <= 1'b1; rs232_rx2 <= 1'b1; end else begin rs232_rx0 <= rs232_rx; rs232_rx1 <= rs232_rx0; rs232_rx2 <= rs232_rx1; end end

assign neg_rs232_rx = rs232_rx2 & ~rs232_rx1; //接收到下降沿后neg_rs232_rx置高一个时钟周期

//---------------------------------------------------------------- reg bps_start_r; reg[3:0] num; //移位次数 reg rx_int; //接收数据中断信号,接收到数据期间始终为高电平

always @ (posedge clk or negedge rst_n) begin if(!rst_n) begin bps_start_r <= 1'bz;