第3章 中低速数据采集系统设计

数据采集系统设计 (2)

Vn (1/ 2)(Vr / 2n ) Vi Vn (1/ 2)(Vr / 2n )

图3.16 理想ADC的传输特性和量化误差

A/D转换器常用以下几项技术指标来 评价其质量水平。

(1) 分辨率 ADC的分辨率定义为ADC所能分辨的输 入模拟量的最小变化量。 (2) 转换时间 A/D转换器完成一次转换所需的时间定 义为A/D转换时间。

第三章 智能仪 器的数据采集技术

智能仪器的数据采集系统简称DAS (Data Acquisition System),是指将 温度、压力、流量、位移等模拟量进行 采集、量化转换成数字量后,以便由计 算机进行存储、处理、显示或打印的装 置。

第一节 数据采集系统的组成结 构

传感器

模拟信号调理

数据采集电路

传感器 频率量 放大整形 输出

传感器 开关量 整形 输出

光电隔离 计算机 光电隔离 计算机

图3.6 频率量及开关量输出传感器的使 用

3. 集成传感器:集成传感器是将传感 器与信号调理电路做成一体。例如,将 应变片、应变电桥、线性化处理、电桥 放大等做成一体,构成集成压力传感器。 采用集成传感器可以减轻输人通道的信 号调理任务,简化通道结构。

图3.10 程控放大器原理框图

(三) 隔离放大器 隔离放大器主要用于要求共模抑制比

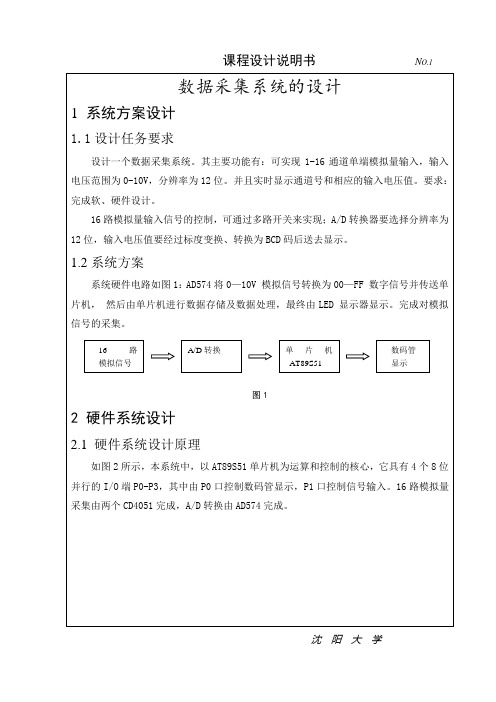

数据采集系统设计

数据采集系统的设计1 设计内容及要求设计一个数据采集系统。

要求:①采集系统的结构;②采集信号路数;③每路信号的主要特征;④计算机借口与控制逻辑;⑤ A/D等主要器件;⑥电源配置。

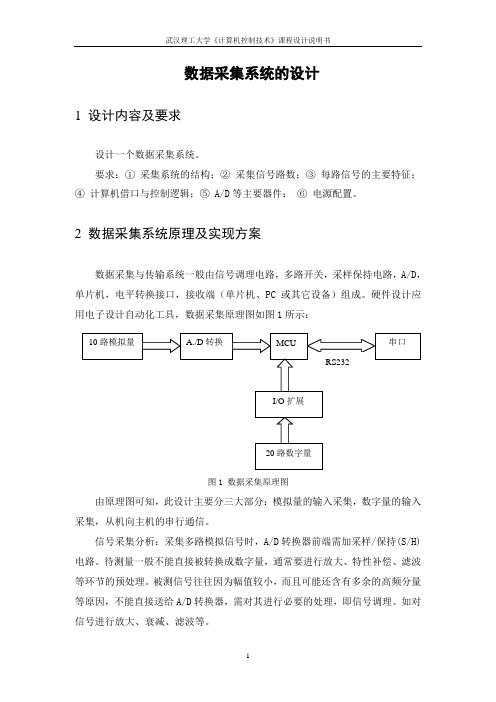

2 数据采集系统原理及实现方案数据采集与传输系统一般由信号调理电路,多路开关,采样保持电路,A/D,单片机,电平转换接口,接收端(单片机、PC或其它设备)组成。

硬件设计应用电子设计自动化工具,数据采集原理图如图1所示:图1 数据采集原理图由原理图可知,此设计主要分三大部分:模拟量的输入采集,数字量的输入采集,从机向主机的串行通信。

信号采集分析:采集多路模拟信号时,A/D转换器前端需加采样/保持(S/H)电路。

待测量一般不能直接被转换成数字量,通常要进行放大、特性补偿、滤波等环节的预处理。

被测信号往往因为幅值较小,而且可能还含有多余的高频分量等原因,不能直接送给A/D转换器,需对其进行必要的处理,即信号调理。

如对信号进行放大、衰减、滤波等。

模拟量的采集:A/D 转换器的选取应考虑:(1)转换时间的选择:转换速度是指完成一次A/D 转换所需时间的倒数,是一个很重要的指标。

A/D 转换器型号不同,转换速度差别很大。

由于本系统的控制时间无具体要求,故可不予考虑,但至少要小于题目要求的1ms ,这是可以达到的。

(2)AD 位数的选择:A/D 转换器的位数决定着信号采集的精度和分辨率。

要求精度为10位。

输入为0~5V 时,分辨率为0049.01251210=-=-N FV V设计要求10位精度的10路模拟量,通过查阅资料,TLC1543芯片满足要求。

TLC1543 是一种开关电容结构的逐次逼近式A/D 转换器, 片内提供转换时钟,12 位或 8 位串行数据输出。

可采集 11 路模拟输入电压,由片内多路开关选通,并采样保持。

数字量的采集:设计中要求是20路数字量,可利用单片机的I/O 口直接采集,但需要20个I/O 口与之对应,这样,就浪费了芯片的管脚资源,可采用并行采集、串行输出的办法,进行I/O 口扩展。

3章 数据采集技术解读

第三章 数据采集技术

测量放大器

模拟多路转换器

采样保持电路

A/D转换器(ADC)及其接口设计 数据采集系统设计及举例

数据采集技术

将温度、压力、流量、位移等模拟量进行采集、量化转换成 数字量后,再收集到微机进一步进行显示、处理、记录和传 输的过程。

智能仪器的数据采集系统

简称DAS(Data Acquisition System),是指将温度、压

力、流量、位移等模拟量进行采集、量化转换成数字量后, 以便由计算机进行存储、处理、显示或打印的系统或装置。

第一节 数据采集系统的组成结构

传感器

模拟信号调理

数据采集电路

微机系统

图3.1 数据采集系统的基本组成

一、数据采集系统的结构框图

输入信号有各自独立的 参考电压,或者信号长 传输引起严重共模干扰。 发挥共模抑制能力,通 道数一半

图3-12 模拟多路转换器的配置

伪差动式

3.3.3

常用的半导体多路转换器芯片

图 图3-13 3-13 AD7501(AD7503) AD7501(AD7503)和 和AD7502 AD7502的功能框图 的功能框图

00:02:48

图3-15 多路切换系统的等效电路 a)低频等效电路 b)高频等效电路

N-1通道被关断的信号在负载上产生的泄漏电压总和:

Ri+Ron<<RL<<(Ri+Roff)/(N-2) 2Ri+Ron<<Roff

1)减小Ri,为此前级应采用电压跟随器。 2)选用Ron极小、Roff极大的开关管。 3)减少输出端并联的开关数N。

对称结构使得具有很高的共模抑制能力 电路参数应对称以保证共模抑制能力 R1=R2,R3=R3, R5=R6

数据采集系统课件

图5图6:数字逻辑部分电源+5V。

:数据输出格式选择信号引脚。

当8/12 =1(+5V)时,双字节输出,即沈阳大学图7 图8AD574A有单极性和双极性两种模拟信号转换方式,这主要通过改变AD574A引脚8、、12的外接电路来实现。

图9左侧所示为单极性转换电路,可实现输入信号0~10V或0~20V的转换,其图9沈阳大学2.2.3单片机模块1、AT89S51单片机的简介AT89S51 是一个低功耗,高性能CMOS 8位单片机,片内含8k Bytes ISP(In-system programmable)的可反复擦写1000次的Flash只读程序存储器,器件采用ATMEL公司的高密度、非易失性存储技术制造,兼容标准MCS-51指令系统及80C51引脚结构,芯片内集成了通用8位中央处理器和ISP Flash存储单元,功能强大的微型计算机的AT89S51可为许多嵌入式控制应用系统供给高性价比的解决方案。

AT89S51具有如下特点:40个引脚,8k Bytes Flash片内程序存储器,128 bytes 的随机存取数据存储器(RAM),32个外部双向输入/输出(I/O)口,5个中断优先级2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

此外,AT89S52设计和配置了振荡频率可为0Hz并可通过软件设置省电模式。

空闲模式下,CPU暂停工作,而RAM定时计数器,串行口,外中断系统可继续工作,掉电模式冻结振荡器而保存RAM的数据,停止芯片其它功能直至外中断激活或硬件复位。

同时该芯片还具有PDIP、TQFP和PLCC等三种封装形式,以适应不一样产品的需求。

AT89S51与AT89C51相比,外型管脚完全相同,AT89C51的HEX程序无须任何转换可直接在AT89S51运行,结果一样。

AT89S比AT89C51新增了一些功能,支持在线编程和看们狗是其中主要特点。

数据采集的设计报告

目录摘要 (3)引言 (5)第一章数据采集系统的概述 (6)1.1 数据采集系统基本概述 (6)1.1.1 数据采集 (6)1.1.2 数据采集系统的分类 (6)1.1.3 数据采集系统的基本功能 (7)1.1.4 数据采集系统的结构形式 (7)第二章数据采集系统整体设计 (8)2.1 硬件设计原则 (8)2.2 软件设计原则 (8)第三章数据采集系统的硬件设计 (9)3.1 系统工作原理 (9)3.2 硬件工作原理 (9)3.2.1 CPU处理核心模块(STC89C52) (9)3.2.2 DS18B20温度传感器模块 (11)3.3 电路设计 (14)3.3.1 CPU处理模块 (14)3.3.2 显示电路 (15)3.3.3 通信电路 (15)3.3.4 复位电路 (15)3.3.5 温度采集电路 (16)3.3.6 晶振电路 (16)3.3.7 警报电路 (17)第四章数据采集系统的软件设计 (18)4.1 汇编语言和Keil C51 (18)4.2 主程序 (19)4.3 各程序 (19)4.3.1 显示子程序 (19)4.3.2 温度子程序 (20)第五章总结 (21)参考文献 (22)附录:程序 (23)摘要本次设计主要基于单片机STC89C52单片机的多点数据采集,该系统由硬件部分和软件部分组成。

硬件部分是由信号接收、信号采集、AD转换和信号发送四部分组成。

系统以单片机为核心,将被测信号转换为能够被单片机所识别的信号输入单片机实现数据采集。

被测信号一般为模拟数据和数字数据两大类。

主机发送的模拟信号经过AD0809的转换,模拟信号经量化后得到离散的值,即数字信号。

在方案的选择中,主机可以用单片机、ARM、电脑等,采用单片机做主机部分,通信距离会比较短,所以使用上拉电阻通过上拉的作用给信号线提供一个驱动电压,使之传输更稳定,传输距离更远,用来抵消线路中内阻对信号的损耗。

关键词:STC89C52;信号接收;信号采集;A/D转换AbstractThis design is mainly based on single-chip microcontroller STC89C52 multi-point data acquisition, this system is consists of hardware and software components. Hardware part is consists of four parts as signal receiving, signal acquisition, AD transform and signal sending. This System is based on single-chip microcontroller, which is being measured signals converted to what can be single-chip microcontroller identification of the signal input data acquisition.Measured signal is divided into two types of commonly simulation data and digital data.The analog signal sending by the mainframe is changed over through AD0809, then the analog signals via discrete values quantified, namely the digital signal.In the choice of case, mainframe can be MCU, ARM, computers and so on, using the monolithic as the mainframe will make a short communication distance, as the result, we use pull-up resistors to pull through the role of signal lines provide a driving voltage, make transmission more stable, the transmission distance is farther, and offset circuit impedance to signal loss.Key words:STC89C52, signal receiving, signal acquisition, A/D transform引言温度是一种最基本的环境参数,人们的生活与环境的温度息息相关,工业和农业生产中得许多场合对温度有严格的要求,如温室养殖场和冷冻室等,随着科学技术的进步,单片机及相关电子技术飞速发展,应用领域不断拓展,利用单片机和传感器实现对温度的精确测量,提高了生产的自动化程度,成本低廉,应用十分广泛,因此研究温度的测量方法和装置具有重要的意义。

数据采集系统的设计与选型PPT课件

和应用软件等。

被测电信 号与非电 信号

传感器或 变换器

信号 调理

数据采集 与控制

驱动 程序

分析与显 示软件

图1. 一个完整的DAQ系统

第2页/共12页

数据采集系统的构成

• 典型的基于PC的数据采集(DAQ)系统

第3页/共12页

PC Based信号采集系统

数据采集 与控制

第4页/共12页

数据采集系统的构成

第9页/共12页

数据采集系统的构成

4. PC与软件 软件使PC与数据采集硬件形成了一个完整的数据采

集、分析和显示系统。 软件分为驱动程序和上层应用程序。

1)驱动程序隐藏了复杂的硬件底层编程细节,为用户提 供容易理解的接口。将采集来的原始数据用可以理解的 形式显示,与用户进行数据交互。一般来说,硬件厂商 在卖出硬件的同时也会提供驱动程序。

•

1. 传感器和变换器

• 传感器感应物理信息并生成可测量的电信号。

• 例如热电偶、电阻式测温计(RTD)、热敏电阻器和IC传感器可以把 温度转变为ADC可测量的模拟信号。

第5页/共12页

变送器/传感器

物理现象 温度

光 声音 力和压力 位置(位移)

流量

PH

传感器 热电偶、电阻温度探测器(RTD)、 IC 传感器、热敏电阻 真空管光电传感器、光导器件

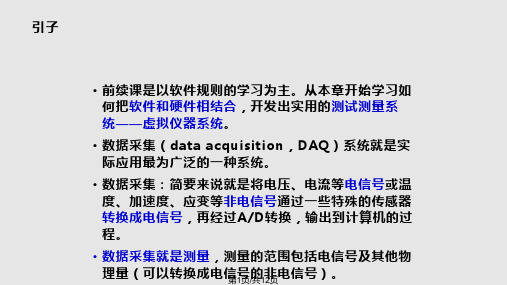

引子

• 前续课是以软件规则的学习为主。从本章开始学习如 何把软件和硬件相结合,开发出实用的测试测量系 统——虚拟仪器系统。

• 数据采集(data acquisition,DAQ)系统就是实 际应用最为广泛的一种系统。

• 数据采集:简要来说就是将电压、电流等电信号或温 度、加速度、应变等非电信号通过一些特殊的传感器 转换成电信号,再经过A/D转换,输出到计算机的过 程。

基于TMS320F2812及Labview的数据采集系统设计与实现

加速度

}

●

TM S3 2 oP2 81 2

。 。 。 。 。 。 ‘ ● ’ _ H 。 一

电 流 陌 i

电 压 陌

西

f D s P )

—

l

——]r一 _

j | 一

上位机

AD7 8 6 4

1 硬 件 结构 设 计

1 . 1 T M¥ 3 2 0 F 2 8 1 2及 A D7 8 6 4介 绍

D S P芯 片之 一 口 。

A D 7 8 6 4 是一种 高速 1 2位的 A / D转换器 .具有 4 个 可同时采样 输入通道 . 单 个通道转换 时间为 1 . 6 5 u s : 可 以通 过软件或者硬 件 的方 法选取用于采样的通道 . 每通道功耗 9 0 mW+ 四个通道 同时工作 时 。 最

0 引言

阐隙

数据采集在计算机广泛应用的今天显得越来越重要 , 它将计算机 与外部物理世界连接起来 随着集成电路和数字信号处理技术 的不断 发展. D S P技术应 用越来越 广泛 .将 D S P 技 术应用于 高速数据 的采 集. 可以将 采集的数据进行 实时处理 , 并 高速可靠地传递 至计算机或 上位机作进一步 的分析处理及其保存 。 本文的实时数据采集 系统主要 应 用于中低速磁悬浮控制系统 . 采用 1 1 公 司的 T M S 3 2 0 F 2 8 1 2 作为系 统 的核心 . 主要采集悬浮系统 的电流 、 电压 、 加速度 、 间隙等数据信号 。 模数转换 部分 采用 A D 7 8 6 4 芯 片. 上位机 数据显示部分采用图形化编 程软件 L a b v i e w实 现

D S P中的软件程序主要完成 间隙 、 加速度 、 电流 、 电压 的采集 , 并将 这些数据上传给上位机软件。在进入主程序后 . 首先初始化 系统 、 初始 化P I E控制寄存器及 P I E矢量表 、初始化 E V寄存器 、 C A N寄存 器 , 并 使能各个中断 。 然后进入循环等待定时器 T l 、 , r 2 中断 定时器 T 1 中断 中驱动 A D 7 8 6 4 完成电流 、 电压信号采集 , 并从 I / O口读取 间隙、 加速度 信号 。定时器 T 2中断则主要将数据通过 C A N总线上传给上位机。 2 . 2 A D7 8 6 4软件具体实现 按 照 AD 7 8 6 4的工作 时序图 . D S P驱 动 A D 7 8 6 4转换 并读取数 据 的过程如下: 首先 由软件选通 4 个数据 采集 通道 . G P I O B 1 5 产 生转换 起 始信号 C O N V E S T .当 C O N V E S T为上升沿 时 , 4 个采样保 持器进 入 保持状态 , 开始对选择的通道采样。同时 , B U S Y输出信号被触发为高 电平 . 并在转换过程 中一直保持为高电平 当 G P I O B 1 3 检测到低电平 时表 明 4 个通道转换结束 . 转换后 的数据保存在 A D 7 8 6 4内部相应 的 锁存器 中。当片选信号和读 信号同时低有效 时 , D S P 则按照转换顺序 从数据总线 X D上并行将数据读走。具体的程序实现如下 :

数据采集与系统设计基础详解演示文稿

峰值 双峰值

xn =max(xi ),i=1,2,...,N

第6页,共70页。

1.1 数据采集系统概述

四、现代数据采集系统的特点:

一般由计算机控制:简化设计、完善功能;

软件的作用越来越大;

数据采集与处理一体化;

数据采集的实时性;

集成度越来越高; 总线技术广泛应用。

第7页,共70页。

1.2数据采集与处理技术

数据采集系统中涉及到的相关技术大体如下:

传感器技术、模拟信号处理技术、A/D转换和D/A转换、

已知样本x(t)

则概率密度为:

p(x)= Nx N Δx

Δx 是中心值为x的小区间, Δx= b-a

k

Nx

是 x n 落在

x-

Δx 2

,x+

Δx 2

区间内的点数之和,[a,b]为x的取值范围,k为[a,b]

区间的等分数。第i 点的取值范围为[di-1,di], di a i Δx

第34页,共70页。

第10页,共70页。

1.3 数据采集系统的结构形式

一、 微型计算机数据采集系统

微型计算机数据采集系统的特点:

系统结构简单,容易实现、对环境的要求不高、成本低、微 型计算机数据采集系统是集散型数据采集系统的一个基本组成部

分、微型计算机的各种I/O模块及软件都比较齐全,很容易构 成系统,便于使用和维护。

1.4 数据采集信号处理基础

第3章 中低速数据采集系统设计

图 3.7

TLV1571 的实际运行时序

3.2.2

TLC7528 的软硬件设计和调试

TLC7528 是双通道、8bit、并行数模转换芯片,具有独立的片内数据锁存器。数据通过 8bit 输入口传送至两个 DA 数据锁存器中的任何一个。控制输入端 DACA 和 DACB 决定数

《DSP 嵌入式系统开发典型案例》

华清远见——嵌入式培训专家

TLV1571 具有两个基准电压输入引脚:REFP 和 REFM。REFP 引脚的电压,是输入模拟 信号的最大值;REFM 引脚的电压,是输入模拟信号的最小值;REFP、REFM 以及模拟输入 一般不超出正电源电压或低于 GND,它们符合 TLV1571 规定的极限参数。当输入信号等于 或高于 REFP 时,数字输出为最大值;当输入信号等于或小于 REFM 时,数字输出为零。外 部基准电压值如表 3.3 所示。

《DSP 嵌入式系统开发典型案例》

《DSP 嵌入式系统开发典型案例》—第 3 章、中低速数据采集系统设计

控制寄存器。

图 3.5

TLV1571 与 DSP5409 的连接

(3)DSP 接收 TLV1571 的中断信号,进入中断服务程序。 (4)DSP 在中断服务程序中,读取 TLV1571 的采样数据,并保存。 (5)重复步骤(3)和(4) ,读取下一个采样数据,并保存。 TLV1517 各种信号的时序如图 3.6 所示。

图 3.4

TLV1571 地线连接

TLV1571 与 TMS320C5409 的连接如图 3.5 所示。使用 DSP 的地址总线的 A0 引脚控制 TLV1571 的片选信号;使用 DSP 的 XF 引脚控制 TLV1571 的读信号;DSP 和 TLV1571 的数 据总线和中断信号直接相连。 TLV1571 的调试,主要步骤如下。 (1) DSP 选通 TLV1571, 根据图 3.5 的连接, 将 DSP 的 A0 引脚置低, 从而选通 TLV1571。 ___ (2)DSP 初始化 TLV1571 的两个控制寄存器,通过 DSP 的 R/ W 信号和数据总线初始化

通用低速数据采集系统的软件设计

四、 串行通信 协议及 单片 机发送程 序设计 ( 一 )通信 的协议 由 于是 和 P c 机通信 ,要 想保证双 方通信 的 成功 ,必 须使通 信 双方有 一系列 约定 。这种 约定叫做通信协议或规程,它必须在编程之前 确定 下来 。 在 串行 通信 中 , 一个重要 的指 标是波 特率 , 波特率即数据传送速率,表示每秒钟传送二进 制 的位数 。单 位是 b p s 。波特率对 C P U与外界 的 通信是 很 重要 的。 它反 映了串行 通信 的速 率 , 也 反映 了对 于传 输通 道的要 求 。波特率 越高 , 要求传输通道的频带越宽。一般异步通信的波 特 率在 5 0 b p s 一9 6 0 0 b p s 之 间[ 2 ] 。

ቤተ መጻሕፍቲ ባይዱ

由于异步通信双方各 自 都有 自己的时钟

源 ,要 保证 捕捉 到 的信号正 确 ,双方在 发送前 必 须约 定两 件事 。一 是字符 格式 ;二是 采用 的 波 特率 是多 少 。在编 写程序 的 时候 ,要 设置 波 特 率和 计数 器 的初值 ,另外 还要设 置定 时器 的 工 作方 式和 串行通 信 的模 式【 1 】 。 ( 二 )串行通 信 寄存 器 的介绍 在 单片 机 的特 殊寄存 器 中有 T MO D, S C O N, P C O N等可 以在 串行 通信 的时候用 的上 。 它 们 的位地 址分别 如下 : 1 . 工作方式控制寄存器( T M O D )

一

、

软件设计 概要

M0 V P CON . # 0 0 H

单 片 机 应 用 系 统 的 软 件 主 要 包 括 两 大 部 分 :用 于管 理数 据采 集系 统工作 的监 控 程序 、 系统主程序和各项功能子程序。 根 据 系统软 件 的总体构 思 ,按 照先 粗后 精 的方法 , 把整个 系统 软件划 分成 多个 功能独 立 、 大小适 当的模块。应明确规定各模块的功能 , 尽量使每个模块功能单一 ,各模块间的接口信 息简单 、完备,接口关系统一,尽可能使各模 块 间 的联 系减少 到最低 限度 。最后再 将 各个 模 块 连接 成一 个完整 的程序 进行 总 的调试 。 二 、程 序设计 流程及 思路 软 件设 计 的第一 步 ,必须 根据 总体 设计 所 明确 的功 能 、任 务 ,硬件 系统所 提供 的 资源 和 工作环 境 等作详 细 的调查研 究 ,甚 至还 要进行 必 要 的系 统试验 。收 集有关 的设 计数 据 和所 需 的技术 指标 及必 要条 件 ,然后 对必需 处 理 的问 题和应 完成 的功 能 、任务 予 以明确定 义 。从 整 体考虑 ,全面 的对 系 统的 功能 、特性 、任务 要 求 、输入 , 输 出、时 间限制 、处理要 求 、技术 指 标 、存 储器 容量 、地 址分配 、I / O接 口,出错 处 理等做出明确合理的规定和定义。 整 个 软件 系统可 以分 为两 个大 的部 分 :单 片机 的软 件设计 和计 算机 上数 据接 收和 处理 的 软件设计。 从上一章系统硬件设计 中可以看到, 整个硬 件 系统可 以分 为电源 电路 、放 大 滤波 电 路 、模 数转 换 电路 、串 口通 讯 电路 四个 部分 , 后 两个 部分 的 电路都 需要单 片 机的 正确 控制 才 能够 正常 工作 ,因此 ,单 片机 的软件 设 计是 整 个系 统的 重要组 成部 分之 一 。而数 据采 集系 统 采 集到 的大量 数据 必须传 送到 P C 机上 才能 够 进行保存、显示、处理等一系列的后续部分。 在 本次 设计 中 , 软 件部 分只能 完成 单片 机对模 , 数 转换 的控 制及 串行 通信 的控制 ,上 位 机部 分 没有体 现 。 单 片机 的程序用 汇编 语言 , 在K e i l C 的集成 开发环 境 ( I D E) 中编 写和编 译 ,然后通 过 编程 器把 编译好 的程 序直 接烧 录到 单 片机 的 R O M 中 。单 片机 上 电后 就可 以运 行 。 三 、A / D转 换程序 设计 本 次设计 中 , 由于所 采用 的 A D C 0 8 0 9的转 换 时 间为 1 2 8 u s ,速 度 比较快 ,并且 C P U 的工 作 比较单一 ,所以可以采用查询的方法对转换

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 3.4

TLV1571 地线连接

TLV1571 与 TMS320C5409 的连接如图 3.5 所示。使用 DSP 的地址总线的 A0 引脚控制 TLV1571 的片选信号;使用 DSP 的 XF 引脚控制 TLV1571 的读信号;DSP 和 TLV1571 的数 据总线和中断信号直接相连。 TLV1571 的调试,主要步骤如下。 (1) DSP 选通 TLV1571, 根据图 3.5 的连接, 将 DSP 的 A0 引脚置低, 从而选通 TLV1571。 ___ (2)DSP 初始化 TLV1571 的两个控制寄存器,通过 DSP 的 R/ W 信号和数据总线初始化

____

华清远见——嵌入式培训专家

_____

(2)等待 TLV1571 产生中断信号( INT 信号产生下降沿) ,一般在初始化之后的 6 个时 钟周期后才会有第一次中断信号产生。 ( 3 )DSP 响应 TLV1571 的中断 ,读入数据 到其 内部存储 器,数据读 完后 DSP 通 知 ____ TLV1571,TLV1571 得到读入完成信号( RD 引脚电平为低)后,开始下一次采样。 ____ 在响应中断过程中, TLV1571 留出 6 个指令周期等待 DSP 读数据, 直到 DSP 收到 RD 为 低信号,TLV1571 才开始下一次采样。 ____ 在对 TLV1571 读或写的同时,必须保证 TLV1571 的 CS 为低,同时还必须保证其他外 部 I/O 空间的片选信号为高(如果系统还有其他外部 I/O 空间) ,从而避免将数据写到其他外 部设备中。 ____ 图 3.7 是实际中对 TLV1571 操作产生的信号波形 。 WR 信号开始有两个下降沿,其目的 ____ 是为了设 置 TLV1571 的两个控制 寄存 器。之 后, WR 信号不 再 有下 降沿, 除非再 次改 变 _____ 此时 TLV1571 TLV1571 的设置。 紧接着 TLV1571 的中断信号产生, 即 图中的 INT 的下降沿。 _____ 已经完成第一次 AD 转换,数据 已经送到数据线上 , INT 的下降沿通知 DSP 可以读入数据。 ____ ____ DSP 读入数据后,置 RD 为低,TLV1571 收到 RD 为低后开始下一次采样。

华清远见——嵌入式培训专家

“黑色经典”系列之《DSP 嵌入式系统开发典型案例》

第 3 章 中低速数据采集系统设计

《DSP 嵌入式系统开发典型案例》

《DSP 嵌入式系统开发典型案例》—第 3 章、中低速数据采集系统设计

3.1 案例要求和应用对象

案例要求:实现对信号频率在 1MHz 以下的模拟信号的采样,并分析信号,对信号进行 数字滤波后,滤波后信号从数模转换器输出。 本案例属于中速数据采集, 使用 TI 公司的 TMS320C5409 型号 DSP 作为核心处理器, 实 现读取 AD 转换器的数据,对数字信号处理后,从 DA 转换器输出信号。由于是中速采样, DSP 可以直接对 AD、DA 控制,不需要增加中间单元。

表 3.1 方式 启动方式 · CSTART 下降沿启动采样 硬件启动 CR0.D7=0 单通道输入 CR0.D3=0 CR1.D7=0 软件启动 CR0.D7=1 · CSTART 上升沿启动转换 ·INT 方式时,每次转换后产生一个 INT 脉冲 ·EOC 方式时,转换开始时 EOC 将由高电平变至低电平,转换结束时返 回高电平 ·最初由 WR 的上升沿启动采样。在 RD 的上升沿发生采样 ·采样开始后的 6 个时钟后开始转换,INT 方式时,每次转换后产生一个 INT 脉冲 ·EOC 方式时,转换开始时 EOC 由高电平变至低电平,转换结束时返回 高电平 TLV1571 转换启动方式 说 明

图 3.7

TLV1571 的实际运行时序

3.2.2

TLC7528 的软硬件设计和调试

TLC7528 是双通道、8bit、并行数模转换芯片,具有独立的片内数据锁存器。数据通过 8bit 输入口传送至两个 DA 数据锁存器中的任何一个。控制输入端 DACA 和 DACB 决定数

《DSP 嵌入式系统开发典型案例》

表 3.2 CR1(D1、D0) D1=0;D0=0 D1=0;D0=1 D1=1;D0=0 D1=1;D0=1 正常工作方式 将 VREFM 作为基准电压加到 AD 将(VREFP-VREFM)/2 作为基准电压加到 AD 将 VIN=VREFP 作为基准电压加到 AD 《DSP 嵌入式系统开发典型案例》 TLV1571 自测方式 自测试电压 N/A 000h 200h 3FFh 数字输出

《DSP 嵌入式系统开发典型案例》

《DSP 嵌入式系统开发典型案例》—第 3 章、中低速数据采集系统设计

控制寄存器。

图 3.5

TLV1571 与 DSP5409 的连接

(3)DSP 接收 TLV1571 的中断信号,进入中断服务程序。 (4)DSP 在中断服务程序中,读取 TLV1571 的采样数据,并保存。 (5)重复步骤(3)和(4) ,读取下一个采样数据,并保存。 TLV1517 各种信号的时序如图 3.6 所示。

华清远见——嵌入式培训专家

TLV1571 具有两个基准电压输入引脚:REFP 和 REFM。REFP 引脚的电压,是输入模拟 信号的最大值;REFM 引脚的电压,是输入模拟信号的最小值;REFP、REFM 以及模拟输入 一般不超出正电源电压或低于 GND,它们符合 TLV1571 规定的极限参数。当输入信号等于 或高于 REFP 时,数字输出为最大值;当输入信号等于或小于 REFM 时,数字输出为零。外 部基准电压值如表 3.3 所示。

3.2.1

TLV1571 的软硬件设计和调试

TLV1571 的内部结构如图 3.2 所示。 TLV1571 的时钟源有内部时钟和外部时钟两种方式。 TLV1571 的时钟信号可以由 CLK 从外部引入,也可以由 TLV1571 的内部时钟产生。和一般 AD 转换器不同,TLV1571 外部时钟信号必须经过 TLV1571 内部 MUX 时钟电路来提供给各 个通道。由于 TLV1571 内部本身也带有时钟,因此 TLV1571 对各种时钟信号都兼容,这些 时钟信号包括正弦波或者方波、TTL 电平或者 CMOS 电平。

对于 TLV1571,单通道输入设置 CR0.D3=0,CR1.D7=0;采用软件启动设置 CR0.D7=1; 采用内部时钟源方式设置 CR0.D5=0;时钟为 20MHz 设置 CR1.D6=1;采用二进制输出方式 设置 CR1.D3=0。最终控制寄存器的设置为 CR0=0080H,CR1=0140H,将这两个数据写到控 制寄存器,TLV1571 将按照以上设置开始工作。 TLV1571 提供 3 种自测试方式,并通过写 CR1 寄存器的 D1 和 D0 位来控制这 3 种测试 方式。这些方式可用于不必提供外部信号就可检查 TLV1571 本身工作是否正常。具体方法如 表 3.2 所示。

图 3.6

TLV1571 的读写时序

图 3.6 是 TLV1571 的读写时序图。从图中可以看出,对于 TLV1571 的具体操作如下。

____

, 同时写入两个寄存器的值到 TLV1571 (置 WR (1) DSP 选通 TLV1571 (置信号 CS 为低) 为低) 。

《DSP 嵌入式系统开发典型案例》

《DSP 嵌入式系统开发典型案例》—第 3 章、中低速数据采集系统设计

据装载到哪一个 DA。 器件的装载周期与随机存取存储器的写周期类似, 因此可灵活地与通 用微处理器数据总线相连接。TLC7528 是宽电压供电,供电电压在 5~15V 之间,功耗小 于 15mW(典型值) ,2 或 4 象限乘法功能使得 TLC7528 十分适合应用于微处理器控制的增 益设置和信号控制领域。如果 TLC7528 工作在电压方式下,其输出幅度是基于电压而不是 基于 电流。 TLC7528 包括两个相同的 8bit 乘法 DA 转换器 DACA 和 DACB。每一个转换器由反相 R-2R 梯形电阻网络、模拟开关以及数据锁存器组成。当 TLC7528 转换器工作时,二进制加 权电流在转换器的输出端与 AGND 之间切换,以确保每一个梯形电阻网络分支电流恒定,且 与开关状态无关。TLC7528 转换器的实际运用较为简单,仅需要在其外部加上外部运算放大 器和电压基准就可正常工作。TLC7528 的 DAC 工作原理如图 3.8 所示。 从图 3.8 可以看出,TLC7528 通过数据总线、 CS 、 WR 以及 DACA 与 DACB 等控制信 号与微处理器接口。当 CS 和 WR 均为低电平时,TLC7528 模拟输出将对 DB0~DB7 数据总 线输入端的变化做出响应。在此方式下,TLC7528 的输入锁存器是透明的,从 DB0~DB7 数据总线输入的数据将直接影响 TLC7528 模拟输出。 当 CS 或 WR 信号变为高电平时, DB0~ DB7 数据总线输入端上的数据被锁存,直至 CS 和 WR 信号再次变低为止。必须注意的是, 当 CS 为高电平时,不管 WR 信号的状态如何,DB0~DB7 数据总线将为高阻状态,禁止输 入数据。

《DSP 嵌入式系统开发典型案例》

华清远见——嵌入式培训专家

图 3.2

TLV1571 的内部结构原理框图

外部模拟信号从 TLV1571 的 AIN 引脚输入,信号到达 TLV1571 的中心单元(10bit 触发 式 AD) ,将模拟信号转换为数字信号,同时 TLV1571 内部的输入寄存器和逻辑控制单元控 制信号转 变 的 方 式,数字信号 经过逻辑校验 单 元到达 三态 数据输出 寄存 器输出。 此外 , TLV1571 提供外部数据输出中断信号 INT 引脚,该引脚信号连接到 DSP 的中断信号,DSP 收到中断信号就可以读取数据总线,获得采样信号。 用于选通芯片;RD 是读信号, TLV1571 的引脚分布如图 3.3 所示。 其中 CS 是片选信号, 即 DSP 每读取一个数据通过该引脚通知 TLV1571,TLV1571 从而开始下一次采样; WR 是 写信号,对 TLV1571 初始化寄存器,通过该引脚通知 TLV1571,TLV1571 从而将数据总线 的数据写入到其内部寄存器;REFP 是高电平参考电压,一般直接连接到 VCC;REFM 是低 电平参考电压,一般直接连接到地。