jtag 20pin引脚定义

jtag接口是什么

jtag 接口是什么

JTAG(JointTestAcTIonGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG 技术是一种

嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP (TestAccessPort,测试访问口),通过专用的JTAG 测试工具对内部节点进行测试。

如今大多数比较复杂的器件都支持JTAG 协议,如ARM、DSP、FPGA 器件等。

标准的JTAG 接口是4 线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

如今JTAG 接口的连接有两种标准,即14 针接口和20 针接口,其定义分别如下所示。

14 针JTAG 接口

1、13VCC 接电源。

jtag工作原理详解

jtag工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它是一种通用的、标准化的接口,可以用于连接芯片或电路板上的各种测试和调试设备。

JTAG接口通常由一个标准的20针或14针连接器组成,用于连接测试和调试设备。

本文将详细介绍JTAG的工作原理。

一、JTAG接口的基本原理1.1 JTAG接口的引脚定义:JTAG接口通常由TCK(Test Clock)、TMS(Test Mode Select)、TDI(Test Data Input)、TDO(Test Data Output)四个引脚组成,用于控制和传输测试数据。

1.2 JTAG接口的工作模式:JTAG接口工作时,通过TCK引脚提供时钟信号,通过TMS引脚控制状态机状态转换,通过TDI引脚输入测试数据,通过TDO引脚输出测试结果。

1.3 JTAG接口的链路结构:JTAG接口可以连接多个芯片或电路板,形成一个链路结构,通过JTAG链路可以同时测试和调试多个设备。

二、JTAG接口的工作流程2.1 进入测试模式:在正常工作模式下,JTAG接口处于绕回状态,当需要进行测试时,通过TMS引脚切换到测试模式。

2.2 通过TCK引脚提供时钟信号:一旦进入测试模式,通过TCK引脚提供时钟信号,控制测试数据的传输和状态机的状态转换。

2.3 通过TDI和TDO引脚传输数据:在测试模式下,通过TDI引脚输入测试数据,通过TDO引脚输出测试结果,通过这种方式完成测试和调试过程。

三、JTAG接口的应用领域3.1 芯片生产测试:在芯片生产过程中,可以通过JTAG接口进行芯片的测试和调试,确保芯片的质量和性能。

3.2 电路板调试:在电路板设计和制造过程中,可以通过JTAG接口对电路板进行测试和调试,发现和修复故障。

3.3 嵌入式系统开发:在嵌入式系统开发过程中,可以通过JTAG接口对系统进行测试和调试,确保系统的稳定性和可靠性。

jtag的pin电压

jtag的pin电压摘要:1.JTAG 的概述2.JTAG 的PIN 电压概述3.JTAG 的PIN 电压标准4.JTAG 的PIN 电压测试方法5.JTAG 的PIN 电压应用实例正文:【1.JTAG 的概述】JTAG(Joint Test Action Group)是一种国际标准测试协议,主要用于集成电路的测试、调试和编程。

JTAG 标准由摩托罗拉公司于1980 年代开发,现在广泛应用于各种电子设备和系统中。

JTAG 技术的一个显著特点是,它允许多个器件通过单一接口进行测试和编程,大大简化了电路设计和生产流程。

【2.JTAG 的PIN 电压概述】在JTAG 技术中,PIN 电压是指JTAG 接口上的电压信号。

JTAG 接口通常包括多个PIN,每个PIN 具有特定的电压信号。

这些电压信号在JTAG 测试、调试和编程过程中起到关键作用。

【3.JTAG 的PIN 电压标准】JTAG 的PIN 电压标准是由JTAG 组织制定的。

根据JTAG 标准,常见的JTAG PIN 电压包括:- VCC:供电电压,通常为3.3V 或5V;- GND:地电压,通常为0V;- TDI:测试数据输入,通常为3.3V 或5V;- TDO:测试数据输出,通常为3.3V 或5V;- SDA:串行数据线,通常为3.3V 或5V;- SCL:串行时钟线,通常为3.3V 或5V。

【4.JTAG 的PIN 电压测试方法】测试JTAG 的PIN 电压通常需要使用万用表或其他测试仪器。

具体测试方法如下:1.将万用表设置为直流电压档;2.将万用表的正极接触到JTAG 接口的PIN 上;3.将万用表的负极接触到地(GND)上;4.读取万用表上的数值,即为该JTAG PIN 的电压值。

【5.JTAG 的PIN 电压应用实例】JTAG 的PIN 电压在实际应用中具有重要意义。

例如,在JTAG 测试过程中,需要通过调整PIN 电压来实现对器件的测试和诊断。

08.Mini J-link SWD 2线模式搭建

J-Link SWD 2线模式注意事项传统20脚JTAG 底座个头大,占用PCB 面积多,连接线复杂。

所以很多开发板仅仅预留2线SWD 接口;J-link 通过这种方式与目标板通讯,可实现程序下载,单步调试等,除了不能给目标板供电、速度有所降低之外,与完整版的功能是一样的。

标准的20 Pin J-LINK for SWD 接口接口定义定义定义如下如下如下::SWD 2线模式下,仅需要SWDIO,SWCLK 两根线进行通讯;然而除这两根线之外,GND 必不可少的;VTef 是目标板提供给Jlink 的工作电源,是J-link 必不可少的电源,同时用于侦测目标板电压; 所以,用Mini J-link 搭建SWD 2线模式,实际实际需要在开发板与需要在开发板与Mini J-link 之间之间,,连接4根线根线:SWDIO --- 数据线,目标板的SWDIO 与Mini J-link 接口的第7Pin 相连;SWCLK --- 时钟线,目标板的SWCLK 与Mini J-link 接口的第9Pin 相连;GND --- Mini J-link 与开发板需要共地,目标板的GND 与Mini J-link 接口的任意GND Pin 相连; VTref --- 将开发板CPU 的电源接入Mini J-link 的第1Pin ;连接好这四根线之后,即可以通过SWD 方式连接开发板,进行工程开发了;注意事项注意事项::1. 这四根一定要都连接上,缺一不可;2. 由于数据传输率还是较高的,所以这四根线一定要尽量做成绞线,缠在一起走,(尤其是SWDIO/SWCLK/GND 一定要绞在一起,尽量等长)避免飞线过远导致数据错误,无法正常使用;3. 连接好了后,使用SWD 方式,并非JTAG 方式;。

ARM与JTAG

CUSIICARM与JTAGJTAG(Joint Test Action Group ,联合测试行动小组) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP (Test Access Port ,测试访问口),通过专用的JTAG 测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持JTAG 协议,如ARM 、DSP 、FPGA 器件等。

标准的JTAG 接口是4 线:TMS 、TCK 、TDI 、TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG 测试允许多个器件通过JTAG 接口串联在一起,形成一个JTAG 链,能实现对各个器件分别测试。

JTAG 接口还常用于实现ISP (In-System Programmable 在系统编程)功能,如对FLASH器件进行编程等。

通过JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

目前JTAG 接口的连接有两种标准,即14 针接口和20 针接口,其定义分别如下所示。

14 针JTAG 接口定义引脚名称描述1 、13 VCC 接电源2 、4 、6 、8 、10 、14 GND 接地3 nTRST 测试系统复位信号5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11TDO 测试数据串行输出12NC 未连接20 针JTAG 接口定义引脚名称描述1VTref 目标板参考电压,接电源2 VCC 接电源3 nTRST 测试系统复位信号4、6、8、10、12、14、16、18、20 GND 接地5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 RTCK 测试时钟返回信号13 TDO 测试数据串行输出15 nRESET 目标系统复位信号17 、19 NC 未连接下面以S3C4510B开发板为例说明JTAG接口:在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG 接口调试S3C4510B,在系统上电前,首先应检测JTAG 接口的TMS 、TCK 、TDI 、TDO 信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B 的nEWAIT 引脚(Pin71 )是否已上拉,ExtMREQ 引脚(Pin108 )是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B 不能正常工作或无法与JTAG 接口通信,均与没有正确处理这两只引脚有关。

笔记本液晶屏各种屏线接口引脚定义

笔记本液晶屏各种屏线接口引脚定义2010-09-21 10:2720PIN单6定义:3.3V3.3V1:电源2:电源3:地4:地5:R0-6:R0+ 7:地8:R1-9:R1+10:地11:R2-12:R2+13:地14:CLK-15:CLK+ 16空 17空 18空 19 空 20空每组信号线之间电阻为(数字表100欧左右)指针表20 -100欧左右(4组相同阻值)20PIN双6定义:1:电源2:电源3:地4:地5:R0-6:R0+7:R1-8:R1+9:R2-10:R2+11:CLK-12:CLK+13:RO1-14:RO1+15:RO2-16:RO2+17:RO3-18:RO3+19:CLK1-20:CLK1+每组信号线之间电阻为(数字表100欧左右)指针表20 -100欧左右(8组相同阻值)20PIN单8定义:1:电源2:电源3:地4:地5:R0-6:R0+ 7:地8:R1-9:R1+10:地11:R2-12:R2+13:地14:CLK-15:CLK+16:R3-17:R3+每组信号线之间电阻为(数字表100欧左右)指针表20 -100欧左右(5组相同阻值)本资料由淮安笔记本维修网源科技提供30PIN单6定义:1:空2:电源3:电源4:空5:空6:空 7:空8:R0-9:R0+10:地11:R1-12:R1+13:地14:R2-15:R2+16:地17:CLK-18:CLK+19:地20:空-21:空22:空23:空24:空25:空26:空27:空28空29空 30空每组信号线之间电阻为(数字表100欧左右)指针表20 -100欧左右(4组相同阻值)30PIN单8定义:1:空2:电源3:电源4:空5:空6:空 7:空8:R0-9:R0+10:地11:R1-12:R1+13:地14:R2-15:R2+16:地17:CLK-18:CLK+19:地20:R3-21:R3+22:地23:空24:空25:空26:空27:空28空29空 30空每组信号线之间电阻为(数字表100欧左右)指针表20 -100欧左右(5组相同阻值。

ATX电源针、针和精编针引脚定义详解

20pin&24pinATX电源针脚定义无主板启动电源——ATX电源接口各线的定义(注意:电源端,主板端口需镜像)AT电源只要能把电源打开就行了,可现在的ATX电源都是电位控制开关而非机械开关,这就需要从电源的那一排查线孔中找出可以激活电源的那个针(Pin)。

ATX电源排针(Pin)的标准定义为???无主板启动电源——ATX电源接口各线的定义(20针和24针的都有)AT电源只要能把电源打开就行了,可现在的ATX电源都是电位控制开关而非机械开关,这就需要从电源的那一排查线孔中找出可以激活电源的那个针(Pin)。

ATX电源排针(Pin)的标准定义为:14号针(Pin14PS-ON)就是控制电源开启关闭的。

单个针没有回路怎么控制开关,其实所有的地线(GND)都可以与其他任意针组成回路,所谓“低电位”开启,“高电位”关闭,就是当Pin14针与GND针短接后,Pin14针本身的电位就低了,电源也就开启了,反之亦然。

现在很清楚了——要想无主板开启ATX电源,只需要将Pin14针(绿色线,图中也标绿了)与任意一个GND针(黑色线,图中标灰了)短接就可以。

红Red=+5V橙Orange=+3.3V黄Yellow=+12V兰Blue=-12V绿Green=PS_ON紫Purple=+5VSB灰Gray=PWR_OK白White=—5V黑Black=COM=GND=接地24pin我们使用的ATX开关电源,输出的电压有+12V、-12V、+5V、-5V、+3.3V等几种不同的电压。

在正常情况下,上述几种电压的输出变化范围允许误差一般在5%之内,如下表所示,不能有太大范围的波动,否则容易出现死机的数据丢失的情况。

i915/925使用新的电源架构ATX12V-24针,它的标准接口从原来的两个提升至三个。

这种分离式的设计,与过往在服务器上的EPS电源很相似,EPS使用+12V两路独立供电的,两个+12V电压输出分别对CPU和其它I/O设备进行供电,这样可以减少由如硬盘光驱等设备对CPU工作时的影响,大大提高系统的稳定性。

ARM系统的JTAG接口

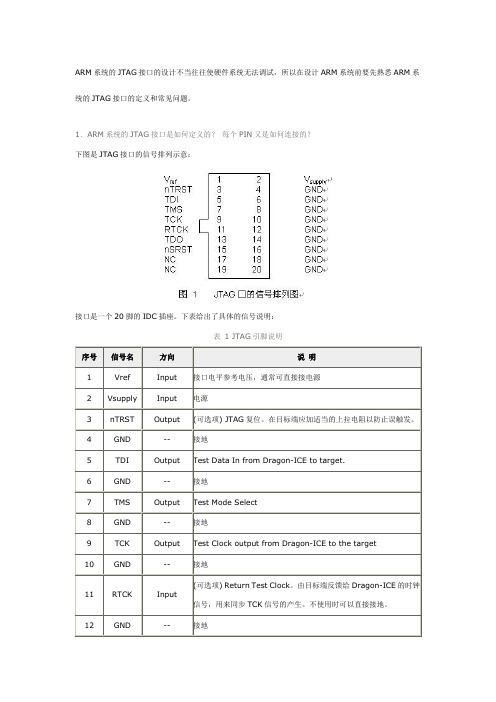

ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表1 JTAG引脚说明2.目标系统如何设计?目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。

RTCK和nTRST这两个信号根据目标ASIC有否提供对应的引脚来选用。

nSRST则根据目标系统的设计考虑来选择使用。

下面是一个典型的连接关系图:复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。

如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。

后面给出了一种电路方案的效果图。

图3 一个复位电路结构的例子在目标系统的PCB设计中,最好把JTAG接口放置得离目标ASIC近一些,如果这两者之间的连线过长,会影响JTAG口的通信速率。

另外电源的连线也需要加以额外考虑,因为Dragon-ICE要从目标板上吸取超过100mA的大电流。

最好能有专门的敷铜层来供电,假如只能使用连线供电的话,最小线宽不应小于10mil (0.254mm)。

3. 14脚JTAG如何与20JTAG连接?Dragon-ICE使用工业标准的20脚JTAG插头,但是有些老的系统采用一种14脚的插座。

这两类接口的信号排列如下:这两类接口之间的信号电气特性都是一样的,因此可以把对应的信号直接连起来进行转接。

Dragon-ICE配备这种转接卡,随机配备。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

jtag 20pin引脚定义

JTAG(Joint Test Action Group)是一种调试界面标准,可以用于测试和调试电路板上的电子设备。

JTAG接口通常由一个20针的连接器组成,这些引脚有不同的功能和定义。

本文将为您介绍JTAG 20针引脚的定义,并提供相关参考内容。

1. VREF:引脚6,JTAG的参考电压引脚。

在大多数情况下,该引脚连接到目标设备的供电电源,以提供JTAG接口的正确工作电平。

2. TDI:引脚7,表示测试数据输入。

此引脚用于将测试数据加载到目标设备中。

3. TDO:引脚8,表示测试数据输出。

此引脚用于从目标设备中读取测试结果。

4. TCK:引脚9,表示测试时钟。

此引脚用于控制测试数据的传输速率。

5. TMS:引脚13,表示测试模式选择。

此引脚用于选择目标设备的测试模式。

6. SRST:引脚15,表示复位信号。

此引脚用于对目标设备执行硬件复位。

7. JTAGEN:引脚19,表示JTAG使能信号。

此引脚用于启用或禁用JTAG接口。

除了引脚定义之外,下面是一些相关的参考内容,可以帮助您更好地了解JTAG 20针引脚的定义和应用:

1. JTAG标准文档:IEEE标准1149.1是JTAG标准的正式文档,可以从IEEE官方网站上免费获取。

该标准详细定义了JTAG接口和相关引脚的功能和特性。

2. 嵌入式系统设计参考书籍:关于嵌入式系统和JTAG调试的书籍是深入了解JTAG接口和相关引脚的很好资源。

《嵌入式系统原理与实践》、《嵌入式系统设计导论》等都是值得参考的书籍。

3. JTAG调试器和开发工具:像J-Link、Xilinx Parallel Cable

IV等JTAG调试器和开发工具都有相关的使用手册,其中包

含了关于JTAG接口和引脚定义的详细说明。

4. 开源硬件项目文档:一些开源硬件项目,如Arduino、Raspberry Pi等,提供了关于JTAG接口的文档和相关资源。

您可以参考这些文档了解JTAG接口和引脚定义在这些项目中

的应用。

总之,JTAG 20针引脚的定义包括VREF、TDI、TDO、TCK、TMS、SRST和JTAGEN等。

通过阅读JTAG标准文档、嵌入

式系统设计参考书籍、JTAG调试器和开发工具的手册,以及

开源硬件项目的文档,您可以更好地了解和应用JTAG接口和相关引脚。