第4章 Verilog HDL行为级建模

EDA技术与Verilog_HDL

1.7 EDA技术的优势

(1)大大降低设计成本,缩短设计周期。 (2)有各类库的支持。 (3)极大地简化了设计文档的管理。 (4)日益强大的逻辑设计仿真测试技术。 (5)设计者拥有完全的自主权,再无受制于人之虞。 (6)软件平台支持任何标准化的设计语言;良好的可移植与可测试性, 为系统开发提供了可靠的保证。 (7)能将所有设计环节纳入统一的自顶向下的设计方案中。 (8)在系统板设计结束后仍可利用计算机对硬件系统进行完整的测试。

Altera 的 SignalTap II Xilinx 的 ChipScope

3.6 FPGA/CPLD产品概述

3.6.1 Lattice公司的CPLD器件系列 1. ispLSI系列器件 2. MACHXO系列 3. MACH4000系列 4. LatticeSC FPGA系列 5. LatticeECP3 FPGA系列

第3章 FPGA/CPLD结构与应用

3.1 概 述

3.1 概 述

3.1.1 可编程逻辑器件的发展历程

(1)20世纪70年代,熔丝编程的PROM和PLA器件是最早的可编程逻辑 器件。 (2)20世纪70年代末,对PLA进行了改进,AMD公司推出PAL器件。 (3)20世纪80年代初,Lattice发明电可擦写的,比PAL使用更灵活的 GAL器件。 (4)20世纪80年代中期,Xilinx公司提出现场可编程概念,生产出了世 界上第一片FPGA器件。同期,A1tera公司推出EPLD器件,较GAL器件 有更高的集成度,可以用紫外线或电擦除。 (5)20世纪80年代末,Lattice公司又提出在系统可编程技术,并且推出 了一系列具备在系统可编程能力的CPLD器件,将可编程逻辑器件的性能 和应用技术推向了一个全新的高度。 (6)进入20世纪90年代后,可编程逻辑集成电路技术进入飞速发展时期。 器件的可用逻辑门数超过了百万门,并出现了内嵌复杂功能模块(如加法 器、乘法器、RAM、CPU核、DSP核、PLL等)的SOPC。

第2讲 Verilog HDL层次建模

2.1.6 自顶向下的设计实例

例2.3 脉动进位计数器顶层模块

例2.4 触发器T_FF 例ຫໍສະໝຸດ .5 带异步复位的D触发器 D_FF

例2.6 激励模块

激励信号和波形输出

2.1.7 小结

用于数字电路设计的两种方法:自顶向下方法和自底向上

方法。在当今的数字电路设计中,这两种方法经常组合使 用。随着设计复杂性的增加,使用这些结构化的方法来进 行设计管理变得越来越重要。 模块是Verilog中的基本功能单元。模块通过调用(实例引 用)来使用,模块的每个实例都被惟一标识,以区别于同 一模块的其他实例。每个实例都拥有其模板模块的不同副 本。读者需要将模块和模块实例区别开来。 仿真有两个不同的组成部分:设计块和激励块,激励块用 于测试设计块。激励块通常是顶层模块。对设计块施加激 励有两种不同的模式。 以脉动进位计数器为例,一步步地解释了为各个部分创建 仿真的过程。

说明为向量,则默认线网的位宽为1。线网的默认值为 z(trireg类型的线网例外,其默认值为x)。线网的值 由其驱动源确定,如果没有驱动源,则线网的值为z。

2.2.2.3 寄存器(reg,integer,real,time)

寄存器用来表示存储元件,它保持原有的数值,直到被

改写。寄存器数据类型一般通过使用关键字reg来声明, 默认值为x。例3.1给出了如何使用寄存器的例子。 例3.1 寄存器的声明和使用

一个模块的示例

Verilog HDL的四种描述方式

行为或算法级:Verilog所支持的最高抽象层次。设计者只

注重其实现的算法,而不关心其具体的硬件实现细节。在 这个层次上进行的设计与C语言编程非常类似。 数据流级:通过说明数据的流程对模块进行描述。设计者 关心的是数据如何在各个寄存器之间流动,以及如何处理 这些数据。 门级:从组成电路的逻辑门及其相互之间的互连关系的角 度来设计模块。这个层次的设计类似于使用门级逻辑简图 来完成设计。 开关级:Verilog所支持的最低抽象层次。通过使用开关、 存储节点及其互连关系来设计模块。在这个层次进行设计 需要了解开关级的实现细节。

Verilog HDL优点

Verilog HDL优点1.能够在多个层次上对所设计的系统加以描述,从开关级、门级、寄存器传输级(RTL)到行为级等;语言不对设计的规模施加任何限制。

2.可采用行为描述、数据流描述和结构化描述三种不同方式或混合方式对设计建模。

3.具有两种数据类型;线网数据类型和寄存器数据类型。

Verilog HDL描述风格结构描述;描述设计单元的硬件结构。

数据流描述;类似寄存器传输级的方式描述数据的传输变换。

行为描述只、混合描述SOPC优势1.合理的性能组合2.提升系统的性能3.降低系统的成本4.更好满足产品生命周期的要求。

步骤1.创建一个Quartus 2工程;2.创建Nios系统模块;启动SOPC Builder;添加CPU及外围器件;指定基地址;系统设置;生成系统模块。

3.将图标添加到BDF文件中。

4.编辑Quartus 2的工程设计文件。

5.配置FPGA;启动Nios 2 IDE;建立新的软件工程;编译工程;运行工程;调试工程;将程序下载到FLASH中。

EDA仿真步骤1.分析系统设计要求和设计思想2.了解各种输出信号及2.要求3.估计各种输出的期望值4.进行实际仿真及结果3.分析5.仿真改进与完善Synplify Pro步骤1.新建工程或打开工程2.新建源工程并添加到工程3.选择工程实现设置4.选择所需研究的工程并进行逻辑综合5.查看有关逻辑综合结果ModelSim SE 6.0步骤1.新建或打开工程2.新建源程序并添加到工程3.编译源程序4.加载设计单元5.建立仿真波形6.运行仿真并观察结果。

10进制计数器posedge上升negedge下降module cnt10(clk,clr,ena,cq,co);input clk,clr,ena;output [3:0] cq;output co;reg [3:0] cnt;reg co;always @(posedge clk or posedge clr) beginif (clr)cnt<=4’b0;elseif (ena)if (cnt==4’h9)cnt<=4’h0elsecnt<=cnt+1;endassign cq=cnt;//控制进位输出并去毛刺always @(posedge clk)beginif (cnt==4’h9)co=4’h1;elseco=4’h0;endendmoduie 测试module cnt10_tb();reg clk,clr,ena;wire [3:0]cq;wire co;cnt10 ut1(clk,clr,ena,cq,co); initial$monitor($time,”clk=%b,clr=%b, cq=%b,co=%b”, clk,clr,ena,cq,co); initialbeginclk=0;clr=1;ena=0;#20 clr=0;经过20后变0#30 ena=1;经过20+30后变1 endinitialbeginforever#10 clk=~clk;endinitial #2000 $finish; endmodule4位阻塞module reg4_bpa(qout,clk,reset,din); output [3:0] qout;input clk,reset;input din;reg [3:0] qout;always @(posedge clk or posedge reset)if (reset)qout=4’b0000;elsebeginqout[0]=din;qout[1]=qout[0];qout[2]=qout[1];qout[3]=qout[2];endendmodule 四选一信号module mu14_1a(y,s,x);output y;input [1:0]s;input[3:0]x;reg y;always @(s or x)begincase (s)2’b00: y=x[0];2’b01: y=x[1];2’b10: y=x[2];2’b11: y=x[3];default: y=1’b0;endcaseend8位加法器module adder4b(a4,b4,c4,s4,co4); input [3:0] a4,b4;input c4;output [3:0] s4;output co4;assign {co4,s4}=a4+b4+c4; endmodulemoduie adder8b(a8,b8,c8,s8,co8); input [7:0] a8,b8;input c8;output [7:0] s8;output co8;wire sc;adder4b u1(.a4(a8[3:0]),.b4(b8[3:0]), .c4(c8),.s4(s8[3:0]),.co4(sc));adder4b u2(.a4(a8[7:4]),.b4(b8[7:4]),.c4(sc),.s4(s8[7:4]),.co4(co8)); endmodule32位锁存器module reg32b(load,dim,dout);input load;input[31:0]din;output[31:0];wire load;wire[31:0] din;reg [3:0] dout;always @(posedge load)begindout=din;endendmodule20分频器module jydiv(clk_in,reset,clk_out);input clk_in,reset;output clk_out;reg [4:0] cnt;reg clk_out;parameter divide_period+20;always @(posedge clk_in or posedge reset) beginif (reset)begincnt<=0;clk_out<=1’b0;endelse If(cnt<(divide_period/2))beginclk_out<=1’b0;cnt<=cnt+1;endelse if (cnt,(divide_period_1))beginclk_out<=1’b0;cnt<=cnt+1;endelsecnt<=1’b0;endendmodule 测频控制信号发生器module testctl(clk,tsten,clr_cnt,load);input clk;output tsten,clr_cnt,load;reg div2clk,clr_cnt;always @(posedge clk)begindiv2clk<=~div2clk;endassign load=~div2clk;assign tsten=div2clk;always @(clk or div2clk)beginif(~div2clk)if(~clk) clr_cnt<=1;else clr_cnt<=0;elseclr_cnt<=0;endendmodule。

VerilogHDL语言基础学习教案课件

o双目运算符(binaryoperator):带两个操作数。 三目运算符(ternaryoperator):带三个操作数。

第27页/共69页

27

第28页/共69页

28

第29页/共69页

格式: assign 连线型变量名=赋值表达式; 持续赋值语句是并发执行的,每条持续赋值语句对应着独 立的逻辑电路,它们的执行顺序与其在描述中的顺序无关。

第51页/共69页

51

第52页/共69页

52

第53页/共69页

53

第54页/共69页

54

4.3.模块的行为描述方式

第20页/共69页

20

wire型数据

用 来 表 示用 assign 语 句 赋 值 的 组 合 逻辑 信 号 。 Verilog HDL模块输入输出端口信号类型说明缺省时,自动定义为wire 型。

wire型变量可以用作任何表达时的输入,也可用作assign 语句、元件调用语句和模块调用语句的输出。

4.1 什么是Verilog HDL?

Verilog HDL 是 目 前 应 用 最 为 广 泛 的 硬 件 描 述 语 言 。 Verilog HDL可以用来进行各种层次的逻辑设计,也可以进行 数字系统的逻辑综合,仿真验证和时序分析等。

Verilog HDL适合算法级,寄存器级,逻辑级,开关级、 系统级和版图级等各个层次的设计和描述。

通过一个例子认识Verilog HDL的3种建模方式,图中电路 实现的功能是,当sel=0时,out=a;当sel=1时,out=b。

第40页/共69页

Verilog教程-夏宇闻(共178张)

第13页,共178页。

3.2 Verilog HDL基本(jīběn)结构

二、Verilog HDL模块的结构

▪ Verilog的基本设计单元是“模块 (block) ” 。 ▪ Verilog 模块的结构由在module和endmodule关键词

之间的4个主要部分组成:

1 端口定义 2 I/O说明

(3)用 “always” 块语句 结构说明语句

always @(posedge clk) // 每当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; // 同步预置数据 else

out = data + 1 + cin; // 加1计数

end

❖注1:“always” 块语句常用于描述时序逻辑,也可 描述组合逻辑。

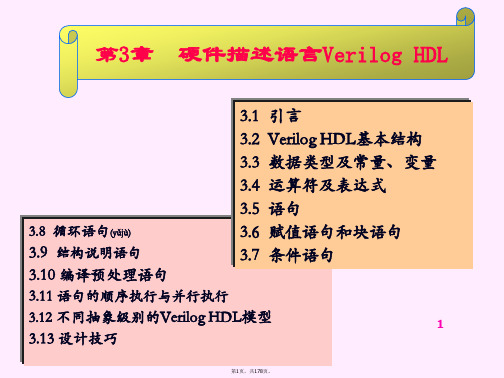

3.12 不同抽象级别的Verilog HDL模型

1

3.13 设计技巧

第1页,共178页。

引言 3.1

(yǐnyán)

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

第2页,共178页。

3.1 引言(yǐnyán)

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

//(1)使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> = 表达式 ;

Verilog语言详解

第三章 Cadence仿真器

学习内容

逻辑仿真算法 如何启动Verilog-XL和NC Verilog仿真器 如何显示波形

仿真算法

主要有三种仿真算法

基于时间的(SPICE仿真器) 基于事件的(Verilog-XL和NC Verilog仿真器) 基于周期的(cycle)

仿真算法

基于时间的算法用于处理连续的时间及变量

课程内容(三)

• 逻辑综合的介绍

– – – – – 简介 设计对象 静态时序分析 (STA) design analyzer环境 可综合的HDL编码风格

• 可综合的Verilog HDL

– Verilog HDL中的一些窍门 – Designware库 – 综合划分

•

实验 (1)

课程内容(四)

• 设计约束( Constraint)

Verilog HDL是在1983年由GDA(GateWay Design Automation)公司的Phil Moorby所创。Phi Moorby 后来成为Verilog-XL的主要设计者和Cadence公司的第一个合伙人。

在1984~1985年间,Moorby设计出了第一个Verilog-XL的仿真器。

Verilog还有一定的晶体管级描述能力及算法级描述能力

行为级和RTL级

MUX的行为可以描述为:只要信号a或b或sel发生变化,如果sel为0则选择a输出;否则选择 b输出。

module muxtwo (out, a, b, sel); input a, b, sel; output out; reg out; always @( sel or a or b) if (! sel) out = a; else out = b; endmodule

北航夏宇闻复杂数字逻辑系统的VerilogHDL设计方法简介

信号处理的工作是可以事后进行。

• 实时系统:

信号处理的工作必须在规定的很短的时间内完 成。

数字信号处理系统的实现

• 非实时系统: 通用的计算机和利用通用计算机改装的设备,

主要工作量是编写 “C” 程序。

• 实时系统: 信号处理专用的微处理器为核心的设备,主 要工作量是编写汇编程序。

行步骤是否正确。 逻辑综合:把RTL级模块转换成门级 。 后仿真:用门级模型做验证,检查门的互连逻辑

其功能是否正确。 布局布线: 在门级模型的基础上加上了布线延时 布局布线后仿真:与真实的电路最接近的验证。

行为级和RTL级

module muxtwo (out, a, b, sl);

input a,b,sl;

end endmodule

Verilog HDL模块的测试

`include myadder.v module t; wire [8:0] sumout; reg [7:0] ain, bin; reg clk; myadder(.clock(clk), .reset(rst), .a(ain), .b(bin), .sum(sumout));

• 行为级:有关行为和技术指标模块,容易理 解

• RTL级:有关逻辑执行步骤的模块,较难理 解

• 门级 :有关逻辑部件互相连接的模块,很 难理解

• 开关级:有关物理形状和布局参数的模块, 非常难理解

抽象级别和综合与仿真的关系

行为仿真:行为的验证和验证模块分割的合理性 前仿真 :即 RTL级仿真,检查有关模块逻辑执

International)

有哪几种硬件描述语言? 各有什么特点?

• VHDL - 比VerilogHDL早几年成为I EEE标准; - 语法/结构比较严格,因而编写出的 模块风格比较清晰; - 比较适合由较多的设计人员合作完成 的特大型项目(一百万门以上)。

第-五讲--行为建模PPT课件

西安邮电学院通信工程系

格式: begin: 块名 … end 或 fork:块名 … join

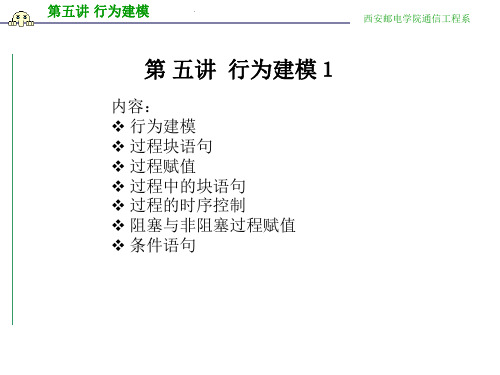

第五讲 行为建模

过程的时序控制

西安邮电学院通信工程系

在过程块中可以说明过程时序。过程时序控制有三类: ❖ 延时执行:#delay, 延迟指定时间步后执行语句 ❖ 边沿敏感事件的时序控制:@(<signal>)

第五讲 行为建模

有名块

有名块的块名作用: ❖ 便于实现对块语句的有效控制 用disable语句终止或提前结束有名块的执行过

程 ❖ 允许在块内引入局部变量 只在块内起作用的变量 变量名可以和块外的其他变量名相同 一定是寄存器类 例: begin: SEQ_BLK

reg[3:0] sat sat = mask & data; ff = ^sat; end

❖ Verilog的行为建模是用一系列以高级编程语言编写的并行的、动态的过

程块来描述系统的工作。

D触发器行为

在每一个时钟上升沿,

若Clr不是低电平,

ห้องสมุดไป่ตู้

置Q为D值,

置Qb为D值的反

无论何时Clr变低 置Q为0, 置Qb为1

第五讲 行为建模

西安邮电学院通信工程系

过程块(procedural)

❖ 过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种:

第五讲 行为建模

西安邮电学院通信工程系

行为建模(描述)

❖ 行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系 统的功能而不是实现。

❖ Verilog有高级编程语言结构用于行为描述,包括:initial, always,@, wait, for, while, if else, case 和 forever 等。