基于FPGA的图像采集系统设计毕业论文

基于FPGA的图像采集卡的设计

基于FPGA的图像采集卡的设计1 引言现代化生产和科学研究对视频图像采集系统的要求日益提高。

传统的图像采集卡速度慢、处理功能简单、采用分立元件、电路非常复杂;而且可靠性差、不易调试、不能很好地满足特殊要求。

FPGA(现场可编程门阵列)是专用集成电路中集成度最高的一种,用户可对FPGA 内部的逻辑模块和I/O模块重新配置,以实现用户所需逻辑功能。

用户对FPGA的编程数据放入芯片,通过上电加载到FPGA中,对其进行初始化;也可在线对其编程,实现系统在线重构。

基于FPGA技术的图像采集主要是通过集成的FPGA开发板,使用软件编程把图像的采集控制程序写入FPGA开发板的芯片上,通过仿真技术来进行图像的采集处理分析。

通过这种方式,便于及时地发现设计中的错误,从而有效地缩短研发时间。

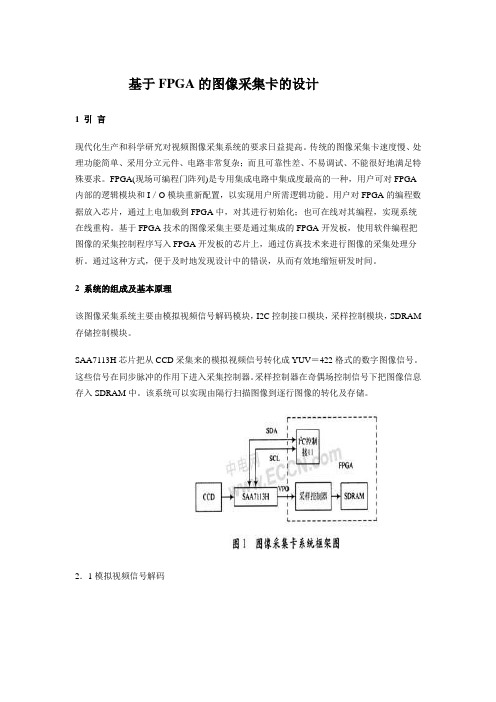

2 系统的组成及基本原理该图像采集系统主要由模拟视频信号解码模块,I2C控制接口模块,采样控制模块,SDRAM 存储控制模块。

SAA7113H芯片把从CCD采集来的模拟视频信号转化成YUV=422格式的数字图像信号。

这些信号在同步脉冲的作用下进入采集控制器。

采样控制器在奇偶场控制信号下把图像信息存入SDRAM中。

该系统可以实现由隔行扫描图像到逐行图像的转化及存储。

2.1模拟视频信号解码由于SAA7113H芯片具有I2C接口,该模块则通过I2C总线来配置SAA7113H初始化的信息。

工作涉及SAA7113H的初始化字的配置、工作方式的配置;行同步开始和结束标志位、确定亮度、色度、饱和度的大小以及输出图像数据信号的格式。

2.2 I2C控制接口模块I2C模块作为SAA7113H寄存器初始配置的整体控制模块。

具体可以分成I2C_cmd和数据传输2个模块I2C_cmd模块为纯组合逻辑电路,完成信号的发送控制任务,配合rom_data[7.0]和rom_addr[7.0]信号完成数据的寻址与存入等工作;而数据传输模块主要和I2C_cmd模块一起组合成I2C的数据控制写入模块,他主要负责对I2C_cmd模块的输出信号进行缓存,并在其输出端输出I2C总线的串行数据SDA以及I2C总线的串行时钟信号SCL。

基于FPGA的一体化实时图像采集系统设计

快 速采 样 、存 储及 图像 数据 处 理 就 显 得 尤 为必 要。 传统 的使 用单 片机作 为控 制器 对数 据进 行 间

B a s e d o n C MO S i m a g e s e n s o r ,o n e F i e l d P r o g r a m ma b l e G a t e A r r a y ( F P G A )i s c h o s e n a s t h e

7 2 6 0 0 0 )

Ab s t r a c t : I n o r d e r t o o b t a i n r e a l - t i me a n d p r e c i s i o n i ma g e f r o m CMOS i ma g e s e n s o r ,a n i mp r o v e d r e a l - t i me d a t a a c q u i s i t i o n s y s t e m i s d e s i g n e d b a s e d o n t h e c o mb i n a t i 刘 萌

( 商洛学 院 物理与电子信息工程系, 陕西商洛 7 2 6 0 0 0 )

摘 要: 为 了通过 C MO S图像探测器实时准确 的获取 图像 。 设计 了一套基 于 F P G A结合 S D R A M

的 实时图像 采 集 系统。根据 C MO S图像探 测 器输 出图像 格式 的特 点 ,选 用 了一 片 X i l i n x公 司

Ke y wor ds : CMOS i ma g e s e n s o r ;F PGA;p i n g — po ng o p e r a t i o n;SDRAM

基于FPGA的多路图像采集系统的软件设计

ue o r AA7 1 H vd od c d r n woF GA oahe e tea q iio ssfu S 1 3 ie e o esa d t P t c iv h c ust n,soa e n ipa ft h n e ma e i trg ,a d dsly o woc a n li g ,

fl sre .I fr e e l e h ac d o f u ain o wo F GA,a d te F mnb s c n g rt n, te I U6 6 ul cen t ut rrai s te c sa e c n g rt ft P — h z i o n h C o iu o f u ai i o h T 5

( 安 工 业 大 学 计 算机 科 学 与 工程 学 院 , 西 西 安 7 0 3 ) 西 陕 10 2

摘 要 :分 析 了 现 有 的 视 频 采 集 方 案 的 研 究现 状 。 对如 何 采 用 C D 摄 像 头采 集 多通 道 、 C 高分 辨 率 、 高质 量 的 图像 以及

基 于 F G 的 嵌 入 式 图 像 采 集 系统 的 实 现 方 法做 了研 究 。 与传 统 图像 采 集 系统 相 比 . 系统 主要 利 用 四 片视 频 解码 PA 该

关键 词 : A 7 l H;F G I U 6 ;图像 采 集 S A l3 P A; T 5 5

,

文 章 编 号 :17 — 2 6 2 1 )3 14 0 6 4 6 3 (0 号 :I 99 , 1 ’ P

文献标识码 : A

The s fwa e de i n o u t- ha ne m a e a q sto s s e b s d o FPGA o t r sg fm lic n li g c uiii n y t m a e n

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的高速图像采集系统设计.

基于FPGA的高速图像采集系统设计引言在低速的数据采集系统中,往往采用单片机或者DSP进行控制;而对于图像采集这种高速数据采集的场合,这种方案就不能满足需要。

因此这种方案极大浪费了单片机或DSP的端口资源且灵活性差;若改用串口方式收集数据,则一方面降低了数据采集的速度,另一方面极大地耗费CPU的资源。

本系统采用FPGA作为数据采集的主控单元,全部控制逻辑由硬件完成,速度快、成本低、灵活性强。

为了增加缓冲功能,系统在FPGA外扩展了256Mb的RAM,不仅增大了缓冲区容量,而且极大地降低了读写频率,有效地减轻了上位机CPU的负担。

在图像数据接口中,比较常见的是VGA、PCI—Express,而这些接口扩展性差、成本高。

本系统采用高速的USB接口作为与上位机通信的端口,速度快、易安装、灵活性强。

1 系统框图系统框图如图1所示。

FPGA控制单元采用A1tera公司Cyclone II系列的EP2C5F256C6,主要由4个部分组成——主控模块、CMOS传感器接口、RAM 控制器以及EZ—USB接口控制器。

传感器接口负责完成SCCB时序控制,RAM控制器用于实现RAM读写与刷新操作的时序,USB接口模块完成主控模块与EZ—USB之间的数据读写;而主控模块负责对从EZ—USB部分接收过来的上位机命令进行解析,解析完命令后产生相应的信号控制各个对应模块,如CMOS传感器传输的图像格式、RAM的读写方式、突发长度等。

2 OV7620模块设计图像传感器采用OV7620,接口图如图2所示。

该传感器功能强大,提供多种数据格式的输出,自动消除白噪声,白平衡、色彩饱和度、色调控制、窗口大小等均可通过内部的SCCB控制线进行设置。

OV7620属于CMOS彩色图像传感器。

它支持连续和隔行两种扫描方式,VGA与QVGA两种图像格式;最高像素为664×492,帧速率为30fps;数据格式包括YUV、YCrCb、RGB三种。

基于FPGA的ADC采集系统的设计_毕业设计论文

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

基于FPGA的数字图像处理系统设计与实现

基于FPGA的数字图像处理系统设计与实现现代社会中,数字图像处理(Digital Image Processing, DIP)已经成为了一个不可或缺的技术。

它可以处理和分析图像,使其更清晰、更美观或者更容易被识别。

而要实现这个技术,我们就需要借助FPGA技术,设计并实现一个基于FPGA的数字图像处理系统。

一、FPGA技术的优势首先,我们来看看为什么要使用FPGA技术。

相对于传统的数字电路设计,FPGA具有以下优势:1. 灵活性高:FPGA可以进行可编程设计,因此可以根据不同需求进行灵活的设计和修改。

这种灵活性可以在数字图像处理的过程中,根据图像的不同特点来修改处理方式,提高图像处理的效率和质量。

2. 时序可控性强:FPGA在设计时可以很好地控制时序,避免一些不必要的时序问题。

对于数字图像处理来说,时序问题可能会导致图像刷新失真等问题。

3. 可重构性强:由于FPGA可以进行可编程的设计,因此被定义为“可重构硬件”。

使用FPGA进行数字图像处理系统设计时,可以实现对系统的快速修改和优化。

4. 运算性能强:FPGA具有并行处理的优势,处理图像时可以同时进行多个数据的计算,大幅提高计算速度。

这样可以使得数字图像处理系统的运算性能更优秀。

基于FPGA的数字图像处理系统,可以充分发挥FPGA的优势,提高图像处理的效率和质量。

二、数字图像处理系统的设计与实现接下来,我们来看看基于FPGA的数字图像处理系统的设计与实现。

对于数字图像处理系统的设计,我们需要从以下几个方面来考虑:1. 系统架构设计:包括数字信号处理(DSP)模块,图像采集器和显像器等,这些模块常常与FPGA相连,构建一个完整的数字图像处理系统。

2. 系统功能设计:本系统可实现图像增强、滤波、边缘检测、图像分割等多种功能,每种功能对应不同的算法和处理方式。

3. 系统软件设计:FPGA硬件设计不同于传统的软件开发,需要针对硬件的特殊性进行开发。

因此需采用专业的硬件设计语言,如Verilog和VHDL等语言,并进行仿真与硬件验证。

基于FPGA的图像采集处理系统

基于FPGA的图像采集处理系统在现代科技领域,特别是计算机视觉和机器学习领域,图像采集和处理已经成为一项至关重要的任务。

在许多应用中,需要快速、准确地对图像进行处理,这推动了图像采集和处理系统的研究和发展。

现场可编程门阵列(FPGA)作为一种可编程逻辑器件,具有并行处理能力强、功耗低、可重构等优点,使其成为构建高性能图像采集处理系统的理想选择。

FPGA是一种可通过编程来配置其硬件资源的集成电路,它由大量的可配置逻辑块、内存块和输入/输出块组成。

这些逻辑块和内存块可以在FPGA上被重新配置,以实现不同的逻辑功能和算法。

输入/输出块可以用于与外部设备进行通信。

基于FPGA的图像采集处理系统通常包括图像采集、预处理、传输、主处理和输出等几个主要环节。

这个阶段主要通过相机等设备获取图像数据。

相机与FPGA之间的接口可以是并行的,也可以是串行的。

并行接口通常传输速度更快,但需要更多的线缆;串行接口则使用更少的线缆,但传输速度可能较慢。

这个阶段主要是对采集到的原始图像数据进行初步处理,如去噪、灰度化、彩色化等。

这些处理任务可以在FPGA上并行进行,以提高处理速度。

经过预处理的图像数据需要通过接口或总线传输到主处理单元(通常是CPU或GPU)进行处理。

在传输过程中,可以使用DMA(直接内存访问)技术,以减少CPU的负载。

在这个阶段,主处理单元(通常是CPU或GPU)会对传输过来的图像数据进行复杂处理,如特征提取、目标检测、图像识别等。

这些处理任务需要大量的计算资源和算法支持。

处理后的图像数据可以通过接口或总线传输到显示设备或用于进一步的处理。

基于FPGA的图像采集处理系统具有处理速度快、可重构性强、功耗低等优点,使其在许多领域都有广泛的应用前景。

特别是在需要实时图像处理的场景中,如无人驾驶、机器视觉等,基于FPGA的图像采集处理系统将具有更高的性能和效率。

随着FPGA技术和相关算法的发展,我们可以预见,基于FPGA的图像采集处理系统将在未来得到更广泛的应用和推广。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的图像采集系统设计前言随着科技社会的发展,图像采集系统在日常生活、工业生产、国家安全等众多领域得到广泛的应用,具有广阔的应用前景和研究价值。

采用FPGA进行设计的图像采集系统有良好的扩展性能和相对稳定的硬件结构。

主要工作如下: 1)分析图像采集和图像处理的原理和特点,设计硬件电路的原理图,完成系统PCB板图的设计。

2)针对FPGA进行内部功能模块的划分,使用Verilog HDL硬件描述语言进行设计。

3)利用SOPC Builder 完成NIOS处理器软核及其外设的创建和配置。

4)根据FPGA内部硬件电路的特点,选择适合FPGA的算法,并对算法进行优化。

5)在NIOS II IDE环境下用Verilog HDL语言编写图像传感器控制、图像采集、SRAM读写控制、图像显示等程序,实现完整的图像采集系统功能。

1课题分析1.1 选题背景(含国内外相关研究综述及评价)与意义EDA技术的发展和应用普及性越来越高,已经涉及到现代电子产品设计的各个系统、各个领域中。

之所以有这样的广泛应用,主要得益于可编程逻辑器件的长足发展和日益成熟,可编程逻辑器件(Programmable Logic Device, PLD)是一种半定制集成电路,在其内部集成了大量的门和触发器等基本逻辑单元电路,通过用户编程来改变PLD内部电路的逻辑关系或连线,从而得到所需要的电路设计功能。

这种新型逻辑器件,不仅速度快、集成度高,能够完成用户定义的逻辑功能,还可以加密和重新定义编程,其允许编程次数可以达到上万次。

可编程逻辑器件的出现,大大改变了传统数字系统设计方法,简化了硬件系统、降低成本、提高系统的可靠性、灵活性。

因此,自20世纪70年代问世以后,PLD受到广大工程师的青睐,被广泛应用于工业控制、通信设备、仪器仪表和医疗电子仪器等众多领域,为EDA技术开创了广阔的发展空间。

VGA作为一种标准的显示接口,在视频和计算机领域得到了广泛的应用。

VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。

对VGA而言,其主要应用在工业控制领域,通过VGA接口实现将信息、图像、文字等内容显示各种VGA显示器上,为客户提供一种完美的显示界面,也是目前重要的显示终端。

本次实验设计主要是基于FPGA芯片为处理器,利用硬件描述语言完成VGA的时序控制,并利用相应的实验平台,进行设计验证,基本实现了VGA 的彩条信号和图像显示效果,达到了整个设计目标和要求。

1.2 选题研究的方法与主要内容1.2.1研究方法通过查阅资料,学习VGA工作原理和控制方法,掌握EDA技术应用基本技巧,运用FPGA为设计实现的处理器,完成VHDL对各个模块的功能描述,在实验平台上完成整个系统设计实现。

1.2.2主要内容◆根据设计任务,制定实现方案◆应用VHDL完成对系统中各个功能模块的描述◆完成顶层设计文件,并调试仿真系统◆下载程序代码到FPGA,在实验平台上验证VGA是否正常显示撰写设计报告书1.3 研究条件和可能存在的问题1.3.1研究条件会使用EDA开发工具软件Quartus II ,能熟练使用VHDL语言编写时序电路,需要有相应的实验开发平台。

1.3.2可能存在的问题:◆VGA时序控制不正确,无法正常显示相应的图形◆VGA硬件接口电路PCB设计不能实现其功能◆FPGA内部ROM存储空间太小,不能存储大容量的图片数据1.4 拟解决的主要问题和预期的结果1.4.1拟解决的主要问题◆VGA时序控制问题◆PROTEL绘制VGA电阻分压网络电路设计问题◆调试VHDL程序代码常见错误1.4.2预期的结果通过完成整个系统的电路设计,实现各个功能模块和顶层设计电路,能在显示器上正确看到横竖彩条、棋盘格图形和图片显示等效果。

2 图像采集系统介绍2.1 图像采集系统功能分析这部分阐述了图像采集系统的各种动作功能和控制要求,给出了完整的图像采集系统操作规程,并介绍了图像采集运行系统中所包括的人工操作步骤。

2.1.1 图像采集系统的基本功能在进行上、下位机程序编写之前,首先要做的工作是确定图像采集系统本身所具备的功能及在进行某种操作后所具有的状态。

在实际生活中,我们见到的图像采集系统可以采集一些简单的图像,如书本、人物和植物等。

图像采例集系统的基本功能就是对图像进行采集,并进行简单的处理。

举一个简单的例子来说明:采集一本书的图像,系统会根据书的颜色大小自动调整,使采集的图像清晰,尽量减小失真。

当图像达到最佳状态时,系统等待外部命令,如继续采集,则同上,如果此时不再采集而按下退出按钮,系统则要进行退出操作,并提示你是否保存所采集的图像,完成此次操作。

由此看来,系统一次采集要涉及摄像头、VGA以及FPGA等,这是它的内部功能。

基于FPGA实现的图像采集系统的整体结构框图如图1.1.1-1所示:系统主要分为:图像采集模块、PLL锁相环时钟管理模块、I2C总线模块、FIFO图像数据处理模块、Nios II 显示控制模块。

系统中PLL负责为Nios II嵌入式内核、外部SDRAM和OV7670摄像头提供时钟,系统通电后,FPGA首先从EPCS中读取配置数据,完成自身程序加载,随后对系统时钟分频为摄像头提供系统时钟,然后通过I2C总线完成对OV7670摄像头的配置。

配置完成后,OV7670将采集到的图像数据输出格式转换为标准的图像数据及图像时钟送入FPGA进行处理,并将处理后的图像数据通过FIFO模块暂时存储在SDRAM中进行缓冲,同时Nios II模块读取存放在SDRAM中的图像数据,按照TFT液晶显示的时序、数据要求将图像数据送到TFT彩色液晶显示屏上显示。

图1.1.1-1 图像采集系统结构3 系统硬件设计3.1 FPGA选型FPGA是该系统的核心,由于系统目前只是完成简单的图像处理,故FPGA选用Altera 公司的低成本FPGA Cyclone II系列器件简介如表所示。

Cyclone II器件采用90nm工艺制造,它延续Cyclone的低成本定位,在逻辑容量、PLL、乘法器和I/O数量上都比Cyclone有了较大提高,应用Cyclone II进行图像处理开发有如下优点:(1)低成本高性能,适应图像处理要求较高的需要。

(2)丰富的内嵌存储器资源,适应大量图像数据存取的需要。

(3)丰富的硬件乘法器,适应图像处理算法的需要。

系统的FPGA选用开发板自带的EP2CS5Q208C8芯片。

Cyclone II系列FPGA参数对比器件EP2C5 EP2C8 EP2C15 EP2C20 EP2C35 EP2C50 EP2C70逻辑单元4608 8256 14448 18752 33216 50528 68416M4K RAM块26 36 52 52 105 129 250总比特数119808 165888 239616 239616 483840 594432 1152000嵌入式乘法器13 18 26 26 35 86 150PLL个数 2 2 4 4 4 4 4最多用户I/O管脚158 182 315 315 475 450 6223.2 图像采集模块选择图像采集采用OV7670图像传感器,OV7670图像传感器体积小、工作电压低。

OV7670摄影头的VGA图像最高达到30帧/秒。

通过SCCB总线控制内部寄存器,可以是OV7670输出整帧、子采样、取窗口等方式的各种分辨率的图像数据。

用户还可以完全控制图像质量、数据格式和传输方式。

OV7670与FPGA硬件连接如图所示。

3.3 图像显示模块图像显示通过在FPGA中构建的Nios II嵌入式内核实现,Nios II系统可以在设计阶段根据实际的需求来增减外设的数量和种类。

可以使用Altera提供的开发工具SOPC Builder,在FPGA器件上创建软硬件开发的基础平台,即用SOPC Builder创建嵌入式内核CPU和参数化的接口总线Avalon。

在此基础上,可以快速地将硬件系统与常规软件集成在单一可编程芯片中。

而且SOPC Builder还提供标准的接口方式,以便用户将外围电路做成Nios II嵌入式内核可以添加的外设模块。

这种设计方式,方便了各类系统的调试。

3.4 PLC的选型与工作原理当某一个控制任务决定由PLC来完成后,选择PLC就成为最重要的事情。

一方面要选择多大容量的PLC ,另一方面是选择什么公司的PLC及外设。

对第一个问题,首先要对控制任务进行详细的分析,把所有的I/O点找出来,包括开关量I/O和模拟量I/O以及输出是用继电器还是晶体管或是可控硅型。

3.4.1 PLC的硬件结构图:图2.4.1-1 PLC硬件结构图3.4.2 PLC各部分的作用与工作原理3.4.2.1 中央处理器CPU是由控制器和运算器组成的。

运算器也称为算术逻辑单元,它的功能就是进行算术运算和逻辑运算。

控制器的作用是控制整个计算机的各个部件有条不紊地工作,其基本功能是从内存中取指令和执行指令。

他的重要功能如下:★诊断PLC电源、内部电路的工作状态及编制程序中的语法错误。

★采集由现场输入装置送来的状态或数据,并送入PLC的寄存器中。

★按用户程序存储器中存放的先后顺序逐条读取指令,进行编译解释后,按指令规定的任务完成各种运算和操作。

★将存于寄存器中的处理结果送至输出端。

★应各种外部设备的工作请求。

3.4.2.2 存储器PLC的存储器分为两大部分:一大部分是系统存储器,用来存放系统管理程序、监控程序及其系统内部数据;二大部分是用户存储器,包括用户程序存储区及工作数据存储区。

3.4.2.3 PLC的基本工作原理PLC采用的是循环扫描工作方式。

对每个程序,CPU从第一条指令开始执行,按指令步序号做周期性的程序循环扫描,如果无跳转指令,则从则从第一条指令开始逐条顺序执行用户程序,直至遇到结束符后又返回第一条指令,如此周而复始不断循环,每一个循环称为一个扫描周期。

PLC的扫描全过程如图2.4.2.3-1所示。

图3.4.2.3-1 PLC的扫描全过程3.4.2.3.1 输入刷新阶段在输入刷新阶段,CPU扫描全部输入端口,读取其状态并写入输入状态寄存器。

完成后关闭输入端口,转入程序执行阶段。

3.4.2.3.2 程序执行阶段在程序执行阶段,根据用户输入的控制程序,从第一条开始逐条执行,并将相应的逻辑运算结果存入对应的内部辅助寄存器和输出状态寄存器。

3.4.2.3.3 输出刷新阶段当所有指令执行完毕后,将输出状态寄存器中的内容,依次送到输出锁存电路,并通过一定输出方式输出,驱动外部相应执行元件工作,这才形成PLC的实际输出。

显然扫描周期的长短主要取决与程序的长短。

扫描周期越长,响应速度越慢。