(完整版)电子科技大学微电子器件习题

电子科技大学《微电子器件》课件PPT微电子器件(3-10)

CTE↓

① ②

AE↓ ( NB↓(

l↓, s↓ ) 但会使

rbb’↑,VA↓)

要使 b↓,应: (1) WB↓( 但会使 rbb’↑,VA↓,且受工艺限制)

(2) η↑ ( 采用平面工艺 )

要使 d↓,应:xdc↓ →NC↑( 但会使 BVCBO↓, CTC↑)

要使 c↓,应:

(1) rcs↓

① ② ③

fT

rbb fT Le

2

CTC

3.10.3 高频晶体管的结构

由

M

fT

8 rbbCTC

可知,要提高 M ,应提高 fT ,降低 rbb’

和 CTC,因此应该采用由平面工艺制成的硅 NPN 管,并采用细

线条的多基极条和多发射极条结构。

l B E B E B ….…

S

提高 M 的各项具体措施及其副作用

除以上主要矛盾外,还存在一些相对次要的其它矛盾,在 进行高频晶体管的设计时需权衡利弊后做折衷考虑。

3.11 双极晶体管的开关特性

(自学)

3.12 SPICE 中的双极晶体管模型

(自学)

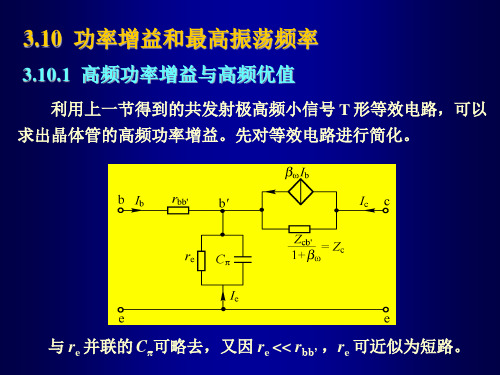

3.10 功率增益和最高振荡频率

3.10.1 高频功率增益与高频优值

利用上一节得到的共发射极高频小信号 T 形等效电路,可以 求出晶体管的高频功率增益。先对等效电路进行简化。

与 re 并联的 Cπ可略去,又因 re << rbb’ ,re 可近似为短路。

再来简化

Zc

Zcb

1 ω

,

1 Zcb

1 rμ

(3) 对 NC 的要求

减小 d 及 rcs 与减小 CTC及提高 BVCBO 对 NC 有矛盾的要求。

这可通过在重掺杂 N+ 衬底上生长一层轻掺杂 N- 外延层来缓解。 外延层厚度与衬底厚度的典型值分别为 10 m 与 200 m 。

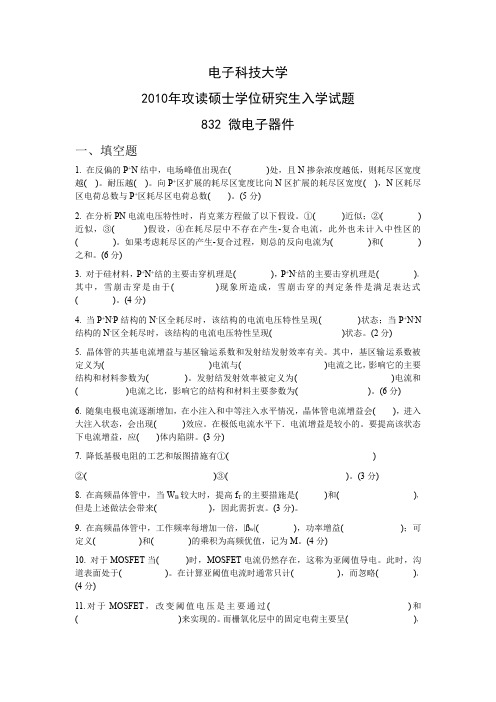

2010年电子科大微电子器件考研试题

电子科技大学2010年攻读硕士学位研究生入学试题832微电子器件一、填空题1.在反偏的P+N结中,电场峰值出现在()处,且N掺杂浓度越低,则耗尽区宽度越()。

耐压越()。

向P+区扩展的耗尽区宽度比向N区扩展的耗尽区宽度(),N区耗尽区电荷总数与P+区耗尽区电荷总数()。

(5分)2.在分析PN电流电压特性时,肖克莱方程做了以下假设。

①()近似;②()近似,③()假设,④在耗尽层中不存在产生-复合电流,此外也未计入中性区的()。

如果考虑耗尽区的产生-复合过程,则总的反向电流为()和()之和。

(6分)3.对于硅材料,P+N+结的主要击穿机理是(),P+N-结的主要击穿机理是()。

其中,雪崩击穿是由于()现象所造成,雪崩击穿的判定条件是满足表达式()。

(4分)4.当P+N-P结构的N-区全耗尽时,该结构的电流电压特性呈现()状态;当P+N-N 结构的N-区全耗尽时,该结构的电流电压特性呈现()状态。

(2分)5.晶体管的共基电流增益与基区输运系数和发射结发射效率有关。

其中,基区输运系数被定义为()电流与()电流之比,影响它的主要结构和材料参数为()。

发射结发射效率被定义为()电流和()电流之比,影响它的结构和材料主要参数为()。

(6分)6.随集电极电流逐渐增加,在小注入和中等注入水平情况,晶体管电流增益会(),进入大注入状态,会出现()效应。

在极低电流水平下.电流增益是较小的。

要提高该状态下电流增益,应()体内陷阱。

(3分)7.降低基极电阻的工艺和版图措施有①()②()③()。

(3分)8.在高频晶体管中,当W B较大时,提高f T的主要措施是()和(),但是上述做法会带来(),因此需折衷。

(3分)。

9.在高频晶体管中,工作频率每增加一倍,|ßw|(),功率增益();可定义()和()的乘积为高频优值,记为M。

(4分)10.对于MOSFET当()时,MOSFET电流仍然存在,这称为亚阈值导电。

此时,沟道表面处于()。

电子科技大学832微电子器件17年考研真题

考试科目:832 微电子器件一、填空题(共45分,每空1.5分)1、根据输运方程,载流子的(扩散)电流主要与载流子浓度梯度相关,而(漂移)电流主要与载流子浓度相关。

2、俄歇复合的逆过程是(碰撞电离)。

3、当PN结反偏时候,反向电流由(少子)扩散电流和势垒区(产生)电流构成。

4、在二极管的反向恢复过程中,中性区存储的非少子浓度降低有两个原因,一是(载流子复合),二是(反向电流抽取)。

5、薄基区二极管是指P区和N区中至少有一个区的长度远小于该区的(少子扩散长度)。

在其它条件相同的情况下,薄基区二极管的中性区宽度越(小),扩散电流越大。

6、(热击穿)又称为二次击穿,这种击穿通常是破坏性的。

7、双极型晶体管的基区少子渡越时间是指少子在基区内从发射结渡越到集电结的平均时间,等于(基区非平衡少子电荷)除以基区少子电流。

8、半导体薄层材料的方块电阻与材料的面积无关,而与(掺杂浓度)和(厚度)相关。

(备注:填电阻率和厚度也可以)。

9、双极型晶体管的电流放大系数具有(正)温度系数,双极型晶体管的反向截止电流具有(正)温度系数。

(填”正”,”负”或”零”)10、双极型晶体管用于数字电路时,其工作点设置在(截至)区和(饱和)区;MOSFET用于模拟电路时,其直流工作点设置在(饱和)区。

11、由于短沟道器件的沟道长度非常短,起源于漏区的电力线将有一部分贯穿沟道区终止于源区,造成源漏之间的(势垒高度)降低,从而造成漏极电流的(变大)。

(第二个空填”变大”,”变小”或”不变”)12、高频小信号电压是指信号电压是指信号电压的振幅小于(KT/q);高频小信号通常是叠加在(直流偏置)上的。

13、MOSFET漏源击穿的机理有两种,一种是(漏极PN结击穿),一种是(沟道穿通)。

14、漏源交流短路的情况下,MOSFET的(沟道载流子)电荷随(栅极)电压的变化,定义为MOSFET的本征栅极电容。

15、长沟道MOSFET的跨导与沟道长度(成反比),与栅源电压(成正比),而发生速度饱和的短沟道MOSFET的跨导与沟道长度(无关)。

微电子技术基础 全册习题解答

微电子技术基础全册习题解答第1章习题解答1.微电子学主要以半导体材料的研究为基础,以实现电路和系统的集成为目的,构建各类复杂的微小化的芯片,其涵盖范围非常广泛,包括各类集成电路(Integrated Circuit,IC)、微型传感器、光电器件及特殊的分离器件等。

2.数字集成电路、模拟集成电路、数模混合集成电路。

3.设计、制造、封装、测试。

4.微机电系统是指集微型传感器、微型执行器、信号处理和控制电路、接口电路、通信系统及电源于一体的系统。

典型应用包括微加速度计、微磁力计、微陀螺仪等。

第2章习题解答1.(100)平面:4.83Å,(110)平面:6.83Å2.略。

3.略。

4.硅的原子密度约为5×1022/cm3,硅外层有四个价电子,故价电子密度为2×1023/cm3 5.N型掺杂杂质:P、As、Sb,P型掺杂杂质:B、Al、Ga、In6.As有5个价电子,为施主杂质,形成N型半导体7.当半导体中同时存在施主和受主杂质时,会发生杂杂质补偿作用,在实际工艺中杂质补偿作用使用的非常广泛,例如在P阱结构中制备NMOS管8.理想半导体假设晶格原子严格按周期性排列并静止在格点位置上,实际半导体中原子不是静止的,而是在其平衡位置附近振动。

理想半导体是纯净不含杂质的,实际半导体含有若干杂质。

理想半导体的晶格结构是完整的,实际半导体中存在点缺陷,线缺陷和面缺陷等。

9.费米能级用于衡量一定温度下,电子在各个量子态上的统计分布。

数值上费米能级是温度为绝对零度时固体能带中充满电子的最高能级。

10.状态密度函数表示能带中能量E附近每单位能量间隔内的量子态数。

11.费米-狄拉克概率函数表示热平衡状态下电子(服从泡利不相容原理的费米子)在不同能量的量子态上统计分布概率。

12.1.5k0T:费米函数0.182,玻尔兹曼函数0.2334k0T:费米函数0.018,玻尔兹曼函数0.018310k0T:费米函数4.54×10-5,玻尔兹曼函数4.54×10-513.所以假设硅的本征费米能级位于禁带中央是合理的14.假设杂质全部由强电离区的E FN D=1019/cm3;E F=E c-0.027eV15.未电离杂质占的百分比为得出:T=37.1K16.本征载流子浓度:1013/cm 3,多子浓度: 1.62×1013/cm 3,少子浓度:6.17×1012/cm 3,E F -E i =0.017eV17.*pC V 0i F *n 3ln 24m E E k T E E m +==+,当温度较小时,第二项整体数值较小,本征费米能级可近似认为处于禁带中央。

电子科大微机原理(新教材)1-4章习题答案

“微处理器系统原理与嵌入式系统设计”第一章习题解答1.1 什么是程序存储式计算机?程序存储式计算机指采用存储程序原理工作的计算机。

存储程序原理又称“冯·诺依曼原理”,其核心思想包括:●程序由指令组成,并和数据一起存放在存储器中;●计算机启动后,能自动地按照程序指令的逻辑顺序逐条把指令从存储器中读出来,自动完成由程序所描述的处理工作。

1.2 通用计算机的几个主要部件是什么?●主机(CPU、主板、内存);●外设(硬盘/光驱、显示器/显卡、键盘/鼠标、声卡/音箱);1.3 以集成电路级别而言,计算机系统的三个主要组成部分是什么?中央处理器、存储器芯片、总线接口芯片1.4 阐述摩尔定律。

每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。

1.5 讨论:摩尔定律有什么限制,可以使用哪些方式克服这些限制?摩尔定律还会持续多久?在摩尔定律之后电路将如何演化?摩尔定律不能逾越的四个鸿沟:基本大小的限制、散热、电流泄露、热噪。

具体问题如:晶体管体积继续缩小的物理极限,高主频导致的高温……解决办法:采用纳米材料、变相材料等取代硅、光学互联、3D、加速器技术、多内核……(为了降低功耗与制造成本,深度集成仍是目前半导体行业努力的方向,但这不可能永无止,因为工艺再先进也不可能将半导体做的比原子更小。

用作绝缘材料的二氧化硅,已逼近极限,如继续缩小将导致漏电、散热等物理瓶颈,数量集成趋势终有终结的一天。

一旦芯片上线条宽度达到纳米数量级时,相当于只有几个分子的大小,这种情况下材料的物理、化学性能将发生质的变化,致使采用现行工艺的半导体器件不能正常工作,摩尔定律也就要走到它的尽头了。

业界专家预计,芯片性能的增长速度将在今后几年趋缓,一般认为摩尔定律能再适用10年左右,其制约的因素一是技术,二是经济。

)1.6 试以实例说明计算机系统结构、计算机组成与计算机实现之间的相互关系与相互影响。

计算机系统结构主要是指程序员关心的计算机概念结构与功能特性,而计算机组成原理则偏重从硬件角度关注物理机器的组织,更底层的器件技术和微组装技术则称为计算机实现。

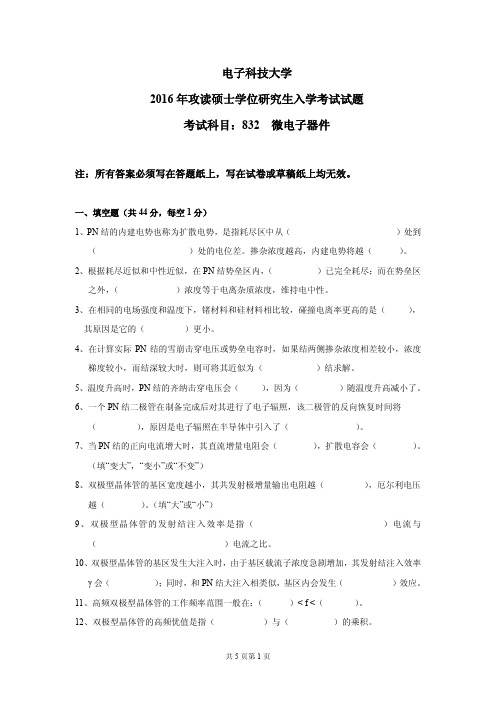

2016年电子科技大学832微电子器件真题

电子科技大学2016年攻读硕士学位研究生入学考试试题考试科目:832 微电子器件注:所有答案必须写在答题纸上,写在试卷或草稿纸上均无效。

一、填空题(共44分,每空1分)1、PN结的内建电势也称为扩散电势,是指耗尽区中从()处到()处的电位差。

掺杂浓度越高,内建电势将越()。

2、根据耗尽近似和中性近似,在PN结势垒区内,()已完全耗尽;而在势垒区之外,()浓度等于电离杂质浓度,维持电中性。

3、在相同的电场强度和温度下,锗材料和硅材料相比较,碰撞电离率更高的是(),其原因是它的()更小。

4、在计算实际PN结的雪崩击穿电压或势垒电容时,如果结两侧掺杂浓度相差较小,浓度梯度较小,而结深较大时,则可将其近似为()结求解。

5、温度升高时,PN结的齐纳击穿电压会(),因为()随温度升高减小了。

6、一个PN结二极管在制备完成后对其进行了电子辐照,该二极管的反向恢复时间将(),原因是电子辐照在半导体中引入了()。

7、当PN结的正向电流增大时,其直流增量电阻会(),扩散电容会()。

(填“变大”,“变小”或“不变”)8、双极型晶体管的基区宽度越小,其共发射极增量输出电阻越(),厄尔利电压越()。

(填“大”或“小”)9、双极型晶体管的发射结注入效率是指()电流与()电流之比。

10、双极型晶体管的基区发生大注入时,由于基区载流子浓度急剧增加,其发射结注入效率γ会();同时,和PN结大注入相类似,基区内会发生()效应。

11、高频双极型晶体管的工作频率范围一般在:()< f <()。

12、双极型晶体管的高频优值是指()与()的乘积。

13、小电流时,双极型晶体管的电流放大系数会下降,这是由于()在()中所占的比例增加所引起的。

14、MOS结构中,半导体的表面势是指从()到()的电势差。

一般来说,实际MOS结构的表面势是()零的,这主要是由于()以及()所引起。

(第三个空填“>”、“<”或“=”)15、为了降低栅氧化层电荷的影响,MOSFET通常会采用()晶面来制作。

微电子作业答案完美版

半导体物理与器件1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分).集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

小规模时代(SSI),元件数2-50;中规模时代(MSI),元件数30-5000;大规模时代(ISI), 元件数5000-10万;超大规模时代(visi),10万-100万;甚大规模,大于100万。

2. 写出IC 制造的5个步骤?(15分)(1)硅片制备(Wafer preparation):晶体生长,滚圆、切片、抛光。

(2)硅片制造(Wafer fabrication):清洗、成膜、光刻、刻蚀、掺杂。

(3)硅片测试/拣选(Wafer test/sort):测试、拣选每个芯片。

(4)装配与封装(Assembly and packaging):沿着划片槽切割成芯片、压焊和包封。

(5)终测(Final test):电学和环境测试。

3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:①提高芯片性能②提高芯片可靠性③降低成本摩尔定律:硅集成电路按照4年为一代,每代的芯片集成度要翻两番、工艺线宽约缩小30%, IC 工作速度提高1.5倍等发展规律发展。

4. 什么是特征尺寸CD?(10分).硅片上的最小特征尺寸称为 CD,CD 常用于衡量工艺难易的标志。

5. 什么是More moore定律和More than Moore定律?(10分) “More Moore”:是指继续遵循Moore定律,芯片特征尺寸不断缩小(Scaling down),以满足处理器和内存对增加性能/容量和降低价格的要求。

它包括了两方面:从几何学角度指的是为了提高密度、性能和可靠性在晶圆水平和垂直方向上的特征尺寸的继续缩小,以及与此关联的3D结构改善等非几何学工艺技术和新材料的运用来影响晶圆的电性能。

“More Than Moore”:指的是用各种方法给最终用户提供附加价值,不一定要缩小特征尺寸,如从系统组件级向3D 集成或精确的封装级(SiP)或芯片级(SoC)转移。

电子科技大学2015年硕士研究生微电子器件考研真题_电子科技大学专业课真题

电子科技大学2015年攻读硕士学位研究生入学考试试题考试科目:832 微电子器件注:所有答案必须写在答题纸上,写在试卷或草稿纸上均无效。

一、填空题(共45分,每空1分)1、泊松方程的积分形式即是()定理,它的物理意义是:流出一个闭合曲面的电通量等于该闭合曲面围成的体积内的()。

2、PN结的扩散电容和势垒电容有很多不同之处。

例如:()只存在于正向偏压之下;()的正负电荷在空间上是分离的;()能用作变容二极管。

3、锗二极管和相同掺杂浓度、相同尺寸的硅二极管相比,其反向饱和电流更(),正向导通压降更()。

4、碰撞电离率是指每个载流子在()内由于碰撞电离产生的()的数目。

电场越(),材料的禁带宽度越(),碰撞电离率将越大。

5、温度升高时,PN结的雪崩击穿电压将(),这是因为温度升高将导致晶格振动加强,因而载流子的平均自由程()。

6、MOSFET用于数字电路时,其工作点设置在()区和()区;双极型晶体管用于模拟电路时,其直流偏置点设置在()区。

7、双极型晶体管的t b既是基区渡越时间,又是()电阻与()电容的乘积。

8、双极型晶体管的跨导代表其()电流受()电压变化的影响。

双极型晶体管的直流偏置点电流I E越大,跨导越();工作温度越高,跨导越()。

(第三、四个空填“大”或“小”)9、一般来说,双极型晶体管的几个反向电流之间的大小关系为:I ES()I CS;I CBO()I CEO;BV CBO()BV CEO;BV EBO()BV CBO(填“>”、“<”或“=”)10、当双极型晶体管集电极反偏,发射极开路时,发射极电流()零,发射结上的偏压()零。

(填“>”、“<”或“=”)11、增加双极型晶体管的基区宽度将()厄尔利电压,()基极电阻,()基区输运系数。

12、NMOS的衬底相对于源端应该接()电位。

当|V BS|增加时,其阈值电压将()。

(第二个空填“增大”、“减小”或“不变”)13、MOSFET的沟道载流子和位于半导体内的载流子相比,除受到()散射及电离杂质散射作用外,还会受到()散射,因此,通常沟道载流子的迁移率()体内载流子迁移率。

电子科技大学大二微电子专业模拟集成电路试卷及答案 (2)

………密………封………线………以………内………答………题………无………效……电子科技大学二零XX 至二零XX 学年第X 学期期终考试模拟集成电路原理课程考试题 A 卷(120分钟)考试形式:开卷考试日期20XX 年月日课程成绩构成:平时10 分,期中0 分,实验10 分,期末80 分一二三四五六七八九十合计一.选择题(共20题,每题2分,共40分)1.对于MOS管, 当W/L保持不变时, MOS管的跨导随漏电流的变化是( B )A. 单调增加B. 单调减小C. 开口向上的抛物线D.开口向下的抛物线.2. 对与MOS器件,器件如果进入饱和区, 跨导相比线性区将( A )A增加 B.减少 C不变 D 可能增加也可能减小3. 在W/L相同时, 采用”折叠”几何结构的MOS管较普通结构的MOS管, 它的栅电阻( C )A 增大B 不变C 减小D 可能增大也可能减小4. 关于衬底PNP,下列说法正确的是( A )A.所有衬底PNP集电极电压必须相同.B.所有衬底PNP发射极电压必须相同.C.所有衬底PNP基极电压必须相同.D.所有衬底PNP各个电极电压可以任意设定5. 对于扩散电阻, 其宽度越大, 则电阻值越易做得( A )A 精确, B误差大, C 误差可大可小, D电阻间的相对误差大.6. 室温下, 扩散电阻阻值的温度系数为( A )A 正, B零, C负, 可正可负7.在集成电路中决定互联线宽度的因素有( A )A.大电流密度限制.B.Si-Al互熔问题.C.互联线的温度系数………密………封………线………以………内………答………题………无………效……D.是否形成欧姆接触.8. 套筒式共源共栅运放和折叠式共源共栅运放相比, 它的( B )较大些A. 最大电压输出摆幅B. 差模增益C. 极点频率D.功耗9.在版图设计上, 采用比例电阻和比例电容的设计可以( C )A. 提高电阻或电容自身的绝对精度,B. 提高电阻或电容自身的相对精度,C. 减小电阻或电容间的比例误差D. 无影响10.差分对中, 不影响其共模抑制比的因素为( C )A.差分管的对称性B.电流源的交流阻抗C.输入电压幅度D.电阻R C1和R C2的对称性11. Cascode电流镜的最小输出电压V MIN(out)的值为( C )A.V ON+V TN B.2(V ON+V TN) C. 2V ON+V TN D. V ON+2V TN12.对于ED NMOS基准电压源电路, 其中的两个NMOS的工作状态为( A )A, 都是饱和区B. 一个是饱和区, 一个是线性区C 都是线性区D都是亚阈值区13正偏二级管正向压降具有( B )温度特性.A . 零 B. 负 C. 正 D. 可正可负14. MOS共栅放大器的特点是( D )A.放大器输入输出反相, 输入阻抗高B.放大器输入输出同相, 输入阻抗高………密………封………线………以………内………答………题………无………效……C.放大器输入输出反相, 输入阻抗低D.放大器输入输出同相, 输入阻抗低15. 电路的主极点是( D )A离原点最远的极点, 它对应电路的-3dB带宽B 离原点最远的极点, 它对应电路的单位增益带宽C离原点最近的极点, 它对应电路的单位增益带宽D.离原点最近的极点, 它对应电路的-3dB带宽16.在CMOS差分输入级中, 下面的做法哪个对减小输入失调电压有利( C )A.增大有源负载管的宽长比.B.提高静态工作电流..C.增大差分对管的沟道长度和宽度D.提高器件的开启(阈值)电压17.在差分电路中, 可采用恒流源替换”长尾”电阻. 这时要求替换”长尾”的恒流源的输出电阻( A )A.越高越好, B.越低越好 C. 没有要求D. 可高可低18. 和共源极放大器相比较, 共源共栅放大器的密勒效应要( A )A.小得多B相当, C 大得多. D不确定19.在版图设计上, 采用比例电阻和比例电容的设计可以( C )A. 提高电阻或电容自身的绝对精度,B. 提高电阻或电容自身的相对精度,C. 减小电阻或电容间的比例误差D. 无影响20.对于差分对的版图设计下列( D )图最优.………密………封………线………以………内………答………题………无………效……二. 简答题(共5题,每题4分, 共20分)1. 画出共源共栅放大器基本结构, 简述其工作原理及特点.答:基本原理:M1为输入器件,M2为共源共栅器件,共源级M1将输入电压信号Vin 转换为电流信号g m Vin ,该电流信号流入M2漏端,从其源端输入到负载。

《微电子器件原理》复习题课件

《微电⼦器件原理》复习题课件考试时间: (第⼗周周⼆6-8节)考试地点:待定《微电⼦器件原理》复习题及部分答案⼀、填空1、PN结电容可分为扩散电容和过渡区电容两种,它们之间的主要区别在于扩散电容产⽣于过渡区外的⼀个扩散长度范围内,其机理为少⼦的充放电,⽽过渡区电容产⽣于空间电荷区,其机理为多⼦的注⼊和耗尽。

2、当MOSFET器件尺⼨缩⼩时会对其阈值电压V T产⽣影响,具体地,对于短沟道器件对V T的影响为下降,对于窄沟道器件对V T的影响为上升。

3、在NPN型BJT中其集电极电流I C受V BE电压控制,其基极电流I B受V BE电压控制。

4、硅-绝缘体SOI器件可⽤标准的MOS⼯艺制备,该类器件显著的优点是寄⽣参数⼩,响应速度快等。

5、PN结击穿的机制主要有雪崩击穿、齐纳击穿、热击穿等等⼏种,其中发⽣雪崩击穿的条件为V B>6E g/q。

6、当MOSFET进⼊饱和区之后,漏电流发⽣不饱和现象,其中主要的原因有沟道长度调制效应,漏沟静电反馈效应和空间电荷限制效应。

⼆、简述1、Early电压V A;答案:2、截⽌频率f T;答案:截⽌频率即电流增益下降到1时所对应的频率值。

3、耗尽层宽度W。

答案:P型材料和N型材料接触后形成PN结,由于存在浓度差,就会产⽣空间电荷区,⽽空间电荷区的宽度就称为耗尽层宽度W。

4、雪崩击穿答案:反偏PN中,载流⼦从电场中获得能量;获得能量的载流⼦运动与晶格相碰,使满带电⼦激出到导带,通过碰撞电离由电离产⽣的载流⼦(电⼦空⽳对)及原来的载流⼦⼜能通过再碰撞电离,造成载流⼦倍增效应,当倍增效应⾜够强的时候,将发⽣“雪崩”——从⽽出现⼤电流,造成PN结击穿,此称为“雪崩击穿”。

5、简述正偏PN结的电流中少⼦与多⼦的转换过程。

答案:N型区中的电⼦,在外加电压的作⽤下,向边界Xn漂移,越过空间电荷区,在边界Xp形成⾮平衡少⼦分布,注⼊到P区的少⼦,然后向体内扩散形成电⼦扩散电流,在扩散过程中电⼦与对⾯漂移过来的空⽳不断复合,结果电⼦扩散电流不断转为空⽳漂移电流.空⽳从P区向N区运动也类同.6、太阳电池和光电⼆极管的主要异同点有哪些?答案:相同点:都是应⽤光⽣伏打效应⼯作的器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章 PN 结填空题1、若某突变 PN 结的 P 型区的掺杂浓度为 N A =1.5 ×1016cm -3 ,则室温下该区的平衡多子 浓度 p p0与平衡少子浓度 n p0分别为( )和( )。

2、在 PN 结的空间电荷区中, P 区一侧带( )电荷, N 区一侧带( )电荷。

内建 电场的方向是从( )区指向( )区。

3、当采用耗尽近似时, N 型耗尽区中的泊松方程为 ( )。

由此方程可以看出, 掺杂浓度越高,则内建电场的斜率越( )。

4、 PN 结的掺杂浓度越高,则势垒区的长度就越( ),内建电场的最大值就越( ), 内建电势 V bi 就越( ),反向饱和电流 I 0就越( ),势垒电容 C T 就越( ),雪崩击穿电 压就越( )。

5、硅突变结内建电势 V bi 可表为(),在室温下的典型值为( )伏特。

6、当对 PN 结外加正向电压时, 其势垒区宽度会 ( ),势垒区的势垒高度会 ()。

7、当对 PN 结外加反向电压时, 其势垒区宽度会 ( ),势垒区的势垒高度会 ( )。

8、在 P 型中性区与耗尽区的边界上,少子浓度 n p 与外加电压 V 之间的关系可表示为( )。

若 P 型区的掺杂浓度 N A =1.5 ×1017cm -3,外加电压 V= 0.52V ,则 P 型区与耗尽区边界上的少子浓度 n p 为( )。

9、当对 PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子 浓度( );当对 PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡 少子浓度( )。

10、 PN 结的正向电流由( 电流三部分所组成。

11、 PN 结的正向电流很大,是因为正向电流的电荷来源是(); PN 结的反向电流很小,是因为反向电流的电荷来源是( )。

12、当对 PN 结外加正向电压时,由 N 区注入 P 区的非平衡电子一边向前扩散,一边 ( )。

每经过一个扩散长度的距离,非平衡电子浓度降到原来的( )。

13、PN 结扩散电流的表达式为 ( )。

这个表达式在正向电压下可简 化为( ),在反向电压下可简化为( )。

14、在 PN 结的正向电流中,当电压较低时,以( )电流为主。

15、薄基区二极管是指 PN 结的某一个或两个中性区的长度小于( )。

在向电流越大,则扩散电容就越( );少子寿命越长,则扩散电容就越( )。

)电流、( )电流和( ))电流为主;当电压较高时,以薄基区二极管中,少子浓度的分布近似为( 16、小注入条件是指注入某区边界附近的 浓度,因此该区总的多子浓度中的( 17、大注入条件是指注入某区边界附近的 浓度,因此该区总的多子浓度中的( 18、势垒电容反映的是 PN 结的(结的掺杂浓度越高,则势垒电容就越( ); )。

( )浓度远小于该区的 () )多子浓度可以忽略。

( )浓度远大于该区的 ( ))多子浓度可以忽略。

)电荷随外加电压的变化率。

PN 外加反向电压越高,则势垒电容就越( )。

19、扩散电容反映的是 PN 结的()电荷随外加电压的变化率。

正20、在PN 结开关管中,在外加电压从正向变为反向后的一段时间内,会出现一个较大的反向电流。

引起这个电流的原因是存储在( )区中的( 的消失途径有两条,即( )和( )。

21、从器件本身的角度,提高开关管的开关速度的主要措施是( )。

22、 PN 结的击穿有三种机理,它们分别是(23、PN 结的掺杂浓度越高, 雪崩击穿电压就越( 24、雪崩击穿和齐纳击穿的条件分别是( 问答与计算题1、简要叙述 PN 结空间电荷区的形成过程。

2、什么叫耗尽近似?什么叫中性近似?3、什么叫突变结?什么叫单边突变结?什么叫线性缓变结?分别画出上述各种PN 结的杂质浓度分布图、内建电场分布图和外加正向电压及反向电压时的少子浓度分布图。

4、 PN 结势垒区的宽度与哪些因素有关?5、写出 PN 结反向饱和电流 I 0的表达式,并对影响 I 0的各种因素进行讨论。

6、PN 结的正向电流由正向扩散电流和势垒区复合电流组成。

试分别说明这两种电流随 外加正向电压的增加而变化的规律。

当正向电压较小时以什么电流为主?当正向电压较大时 以什么电流为主?7、什么是小注入条件?什么是大注入条件?写出小注入条件和大注入条件下的结定律, 并讨论两种情况下中性区边界上载流子浓度随外加电压的变化规律。

8、在工程实际中,一般采用什么方法来计算 PN 结的雪崩击穿电压?9、简要叙述 PN 结势垒电容和扩散电容的形成机理及特点。

10、当把 PN 结作为开关使用时,在直流特性和瞬态特性这两方面, PN 结与理想开关 相比有哪些差距?引起 PN 结反向恢复过程的主要原因是什么?11、某突变 PN 结的 N D =1.5 ×1015cm -3, N A =1.5 ×1018cm -3,试求 n n0, p n0, p p0和 n p0的值,并 求当外加 0.5V 正向电压和( -0.5V )反向电压时的 n p (-x p )和 p n (x n )的值。

12、某突变 PN 结的 N D =1.5 ×1015cm -3, N A =1.5 ×1018cm -3,计算该 PN 结的内建电势 V bi 之 值。

13、有一个 P 沟道 MOSFET 的衬底掺杂浓度为 N D =1.5 ×1015cm -3,另一个 N 沟道MOSFET 的衬底掺杂浓度为 N A =1.5 ×1018cm -3。

试分别求这两个 MOSFET 的衬底费米势,并将这两个 衬底费米势之和与上题的 V bi 相比较。

14、某突变 PN 结的 N D =1.5 ×1015cm -3, N A =1.5 ×1018cm -3,试问 J dp 是 J dn 的多少倍? 15、已知某 PN 结的反向饱和电流为 I o =10 -12A ,试分别求当外加 0.5V 正向电压和(-0.5V ) 反向电压时的 PN 结扩散电流。

16、已知某 PN 结的反向饱和电流为 I o =10 -11A ,若以当正向电流达到 10 -2A 作为正向 导通的开始,试求正向导通电压 V F 之值。

若此 PN 结存在寄生串联电阻 R cs = 4 Ω,则在同样的测试条件下 V F 将变为多少? 17、某硅单边突变结的雪崩击穿临界电场 E C =3.5 ×105Vcm -1,开始发生雪崩击穿时的耗 尽区宽度 x dB = 8.57 μ,m 求该 PN 结的雪崩击穿电压 V B 。

若对该 PN 结外加 |V|=0.25V B 的反向 电压,则其耗尽区宽度为多少?18、如果设单边突变结的雪崩击穿临界电场 e C 与杂质浓度无关,则为了使雪崩击穿电 压 V B 提高 1 倍,发生雪崩击穿时的耗尽区宽度 x dB 应为原来的多少倍?低掺杂区的杂质浓度 应为原来的多少倍?)电荷。

这个电荷)和 )、( )和( )。

);结深越浅, 雪崩击穿电压就越 ( )。

19、某突变PN 结的V bi = 0.7V ,当外加-4.3V 的反向电压时测得其势垒电容为8pF,则当外加-19.3V 的反向电压时其势垒电容应为多少?20、某突变结的内建电势V bi = 0.7V ,当外加电压V= 0.3V 时的势垒电容与扩散电容分别是2pF 和2×10-4pF,试求当外加电压V= 0.6V 时的势垒电容与扩散电容分别是多少?21、某硅突变结的n A= 1 × 1016cm-3,n D= 5 ×1016cm-3,试计算平衡状态下的(1)内建电势V bi ;(2)P区耗尽区宽度x p、N 区耗尽区宽度x n 及总的耗尽区宽度x D;(3)最大电场强度εmax。

22、某单边突变结在平衡状态时的势垒区宽度为x D0,试求外加反向电压应为内建电势V bi 的多少倍时,才能使势垒区宽度分别达到2x d0和3x d0。

23、一块同一导电类型的半导体,当掺杂浓度不均匀时,也会存在内建电场和内建电势。

设一块N 型硅的两个相邻区域的施主杂质浓度分别为n D1 和n D2 ,试推导出这两个区域之间的内建电势公式。

如果n D1= 1 × 1020cm-3,n D2= 1 ×1016cm-3,则室温下内建电势为多少?24、试推导出杂质浓度为指数分布N= N0exp(-x/l)的中性区的内建电场表达式。

若某具有这种杂质浓度分布的硅的表面杂质浓度为1018cm-3,λ= 0.4 μm,试求其内建电场的大小。

再将此电场与某突变PN 结的耗尽区中最大电场作比较,该突变PN 结的n A= 1018cm-3,n D=1015cm-3。

25、图P2-1所示为硅PIN 结的杂质浓度分布图,符号I 代表本征区。

(1)试推导出该PIN 结的内建电场表达式和各耗尽区长度的表达式,并画出内建电场分布图。

(2)将此PIN 结的最大电场与不包含I 区的PN 结的最大电场进行比较。

设后者的P 区与N 区的掺杂浓度分别与前者的P 区与N 区的相同。

图P2-1图P2-226、某硅中的杂质浓度分布如图P2-2所示,施主杂质和受主杂质的浓度分别为N D(x)=10 16exp(-x/ 2 1×0 -4)cm-3和N A (x)= N A(0)exp(-x/10 -4)cm -3(1)如果要使结深x J= 1 μm,则受主杂质的表面浓度n A (0)应为多少?(2)试计算结深处的杂质浓度梯度A 的值。

(3)若将此PN结近似为线性缓变结,设V bi= 0.7V ,试计算平衡时的耗尽区最大电场εmax,并画出内建电场分布图。

27、试证明在一个P 区电导率σp 远大于N 区电导率σn 的PN 结中,当外加正向电压时空穴电流远大于电子电流。

28、已知n I2= N C N V exp(-e G/kT) = CkT3exp(-e G0/kT),式中n C、n V 分别代表导带底、价带顶的有效状态密度,e G0代表绝对零度下的禁带宽度。

低温时反向饱和电流以势垒区产生电流为主。

试求反向饱和电流I0与温度的关系,并求I0随温度的相对变化率(dI0/dT)/I0,同时画出电压一定时的I0~ T 曲线。

29、某P+N -N +结的雪崩击穿临界电场εc为32V/ μm,当N-区的长度足够长时,击穿电压V B 为144V 。

试求当N-区的长度缩短为3μm时的击穿电压为多少?30、已知某硅单边突变结的内建电势为0.6V ,当外加反向电压为3.0V 时测得势垒电容为10pF ,试计算当外加0.2V 正向电压时的势垒电容。