基于Zynq-7000高速图像采集与实时处理系统

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于Zynq SoC的EtherCAT主站设计及实现

No. 7Jul ・ 2020第7期2020年7月组合机床与自动化加工技术Modular Machine Tool & Automatic Manufacturing Techinnue文章编号 #1001 -2265(2020)07 -0122 -05DOI : 10.13462/j. cnki. mmtamt. 2020. 07. 028基于Zynq SoC 的EtterCAT 主站设计及实现*收稿日期#2019 -08 -24*基金项目:广东省重点领域研发计划项目(2019B090918002);高档数控机床与基[制造装备(2018ZX04006001 - 010)作者简介:马平(1968-),男,湖南汨罗人,广东工业大学教授,博士,研究方向为高速数控机床关键技术、超精密驱动进给技术,(E-mail ) pingma@gdue edu. cn ;通讯作者:苏攀杰(1994—),男,广东湛江人,广东工业大学硕士研究生,研究方向为嵌人式系统、工业现场通信,(E- mail ) vickers_su@ 163. com#马 平1 #苏攀杰1,刘胜旺1,邓龙军2(1.广东工业大学机电工程学院,广州510006;2.广州数控设备有限公司,广州510535)摘要#为了在高端数控系统中实施高性能的Ether/AT 总线,提出了一种基于Zynq-7000 SoC 的Eth- rCAT 主站构建方案。

首先基于Zynq-7000硬件平台,运用系统模块化设计方法对Ether/AT 主站 进行总体方案规划,然后基于电子设计平台Vivado 设计主站的硬件工程,接着在CPU0上搭建Far eRTOS 操作系统,在此基础上移植了开源主站库! SOEM-1.3.3)并对网卡驱动进行优化,最后建立了 Ether/AT 主站测试系统。

实验结果表明,该主站的周期通信时间约为40&#通信抖动为纳秒级, 具有较高的实时性和稳定性。

【拆机】鼎阳SDS1102X示波器拆解

【拆机】鼎阳SDS1102X示波器拆解△图 1 SDS1000X-E中集成了Zynq-7000SDS1000X-E中采用的XC7Z020 SoC芯片,具有双核ARM Cortex-A9处理器(PS)+基于Artix-7架构的FPGA(PL),其中处理器部分支持的最高主频为866 MHz, FPGA部分则包含85k逻辑单元、4.9 Mb Block RAM和220个DSP Slice,并提供对常用外部存储器如DDR2/DDR3的支持,非常契合数字示波器中对数据进行采集、存储和数字信号处理的需求。

同时,Zynq-7000的PS(处理器系统)和PL(可编程逻辑)部分之间通过AXI高速总线互连,可以有效解决传统数字存储示波器中CPU与FPGA间数据传输的带宽瓶颈问题,有利于降低数字示波器的死区时间,提高波形捕获率。

用单片SoC芯片替代传统的CPU+FPGA的分立方案,也可以减少硬件布板面积,有利于将高性能处理系统向紧凑型的入门级示波器中集成。

数据采集与存储△图 2 用Zynq-7000构架的SPO引擎SDS1000X-E中采用的高速模-数转换(ADC)芯片,其数据接口为LVDS差分对形式,每对LVDS的速率为1 Gbps。

采用的Zynq-7000芯片,其可编程IO的LVDS最高速率可达1.25 Gbps,可以保证稳定可靠地接收ADC采样到的数据。

同时,FPGA接收到的高速ADC数据需要实时地写入到存储器中,以8-bit,1 GSa/s的ADC为例,其输出数据的吞吐率为1 GByte/s。

Zynq-7000支持常用的DDR2、DDR3等低成本存储器,最高DDR3接口速率可达1066 MT/s,因此,使用单片DDR3即可满足实时存储上述ADC输出数据的要求。

而且,Zynq-7000支持PL共享PS的存储器,只要给PS部分预留足够的存储器带宽,剩余带宽用于存储ADC 数据,无须在PL部分再外挂存储器,降低了成本。

Xilinx Vivado zynq7000 入门笔记

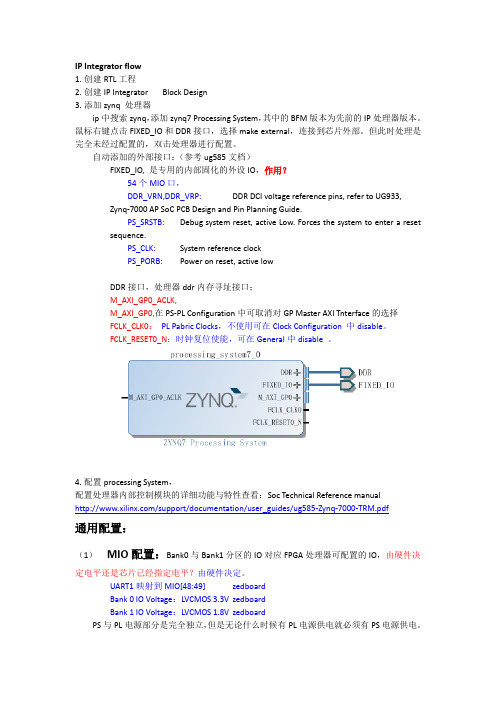

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

基于FPGA的红外图像实时采集系统设计与实现

基于FPGA的红外图像实时采集系统设计与实现摘要:随着红外图像在军事、航天、安防等领域的广泛应用,对红外图像的实时采集和处理需求越来越高。

本文基于FPGA设计并实现了一个红外图像实时采集系统,通过系统硬件框架、图像采集流程设计以及软硬件协同优化等方面的探究,实现了高效、稳定的红外图像实时采集和传输,为相关领域的探究和应用提供了重要支持。

一、引言红外图像技术是一种利用物体发射的红外辐射进行成像分析的技术,具有透过阴郁、烟雾等不利环境的能力。

它在军事、航天、安防等领域具有重要应用价值。

红外图像的实时采集和处理对于这些领域的探究和应用至关重要,然而传统的红外图像采集系统存在采集速度慢、波动大、传输距离限制等问题。

因此,设计并实现一种基于FPGA的红外图像实时采集系统具有重要意义。

二、系统框架设计基于FPGA的红外图像实时采集系统主要由硬件和软件两个部分组成。

硬件部分包括红外探测器、FPGA开发板、存储器、图像传输模块等;软件部分主要包括图像采集控制程序和数据处理程序。

硬件框架设计接受分层结构,分为红外图像采集层、控制层、存储层和传输层四个部分。

红外图像采集层包括红外探测器和模拟-数字转换电路,负责将红外辐射信号转换为数字信号。

控制层包括FPGA芯片和时钟控制电路,负责采集信号的控制和同步。

存储层包括高速存储器和图像缓存,负责暂存采集到的红外图像数据。

传输层包括数据传输电路和网络接口,负责将采集到的图像数据传输到外部设备。

三、图像采集流程设计图像采集流程是指将红外图像转换为数字信号并存储的过程。

在红外图像采集层,红外探测器将红外辐射信号转换为模拟信号,经过模拟-数字转换电路转换成数字信号。

在控制层,FPGA芯片控制采集信号的采样频率和位宽,通过时钟控制电路实现同步。

在存储层,高速存储器负责将采集到的图像数据暂存起来,图像缓存则将暂存的图像数据进行处理和压缩。

在传输层,数据传输电路将处理和压缩后的图像数据传输到外部设备。

基于VxWorks的实时图像采集及处理系统

基于VxWorks的实时图像采集及处理系统

蔡巍;刘世元;黄弢;史铁林

【期刊名称】《微计算机信息》

【年(卷),期】2007(023)014

【摘要】为了对给定的标记图像进行识别定位,该文讨论了一种基于嵌入式操作系统VxWorks的实时图像采集及处理系统,给出了该系统的主要架构和系统采用的图像处理算法,并对上位机和下位机之间采用的socket通信机制进行了介绍.

【总页数】3页(P54-55,53)

【作者】蔡巍;刘世元;黄弢;史铁林

【作者单位】430074,武汉,华中科技大学机械科学与工程学院;430074,武汉,武汉光电国家实验室光电材料与微纳制造研究部;430074,武汉,华中科技大学机械科学与工程学院;430074,武汉,武汉光电国家实验室光电材料与微纳制造研究部;430074,武汉,华中科技大学机械科学与工程学院;430074,武汉,华中科技大学机械科学与工程学院;430074,武汉,武汉光电国家实验室光电材料与微纳制造研究部

【正文语种】中文

【中图分类】TP316.2

【相关文献】

1.基于VxWorks的实时图像采集技术 [J], 谢诚;虢仲平

2.基于Meteor Ⅱ图像采集卡的图像实时处理系统开发 [J], 应浩;詹跃东;范九荣;胡浩

3.基于VxWorks的实时图像采集及处理系统 [J], 蔡巍;刘世元;黄弢;史铁林

4.基于Access数据库的图像采集与实时处理系统设计 [J], 杨天敏

5.基于FPGA和DSP的高速实时轨道巡检图像采集处理系统 [J], 程雨;杜馨瑜;顾子晨;戴鹏;李海浪;王昊

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PYNQ的传感器数据采集系统实验案例设计

实验技术与管理Experimental Technology and Management 第38卷第1期2021年1月Vol.38No.l Jan.2021ISSN1002-4956CN11-2034/TDOI:10.16791/ki.sjg.2O21.01.013基于PYNQ的传感器数据采集系统实验案例设计刘玉梅,棊俊炜,任立群,侯长波,于蕾(哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨150001)摘要:为了加强嵌入式系统设计实践教学的效果,提高学生解决复杂工程问题的能力,采用自顶向下的设计方法设计了传感器数据采集系统的实验案例该案例采用ZYNQ-7000系列为核心的PYNQ-Z2硬件平台,通过Arduino接口连接传感器.利用Xilinx公司的Vivado及SDK进行软、硬件设计与开发,通过该实验案例.使学生深入理解ZYNQ-7000软硬件协同设计原理和方法,以及通过Arduino的模拟、数字、Fc、UART总线通信接口釆集传送数据的方法.激发学生对“微处理器结构与嵌入式系统设计”课程的学习兴趣.提升实践教学效果。

关键词:嵌入式系统设计;PYNQ;ZYNQ-7000;Arduino;自顶向下设计中图分类号:TP368.1文献标识码:A文章编号:1002-4956(2021)01-0058-07Design of experimental case on sensor data acquisitionsystem based on PYNQLIU Yumei,QI Junwei,REN Liqun,HOU Changbo,YU Lei(College of Information and Communication,Harbin Engineering University,Harbin150001,China)Abstract:In order to strengthen the effect of embedded system design practice teaching and improve students'ability to solve complex engineering problems,an experimental case of the sensor data acquisition system isdesigned with a top-down design method.This case adopts the PYNQ-Z2hardware platform with ZYNQ-7000series as the core,connects sensors through Arduino interface,and uses Xilinx's Vivado and SDK for software andhardware design and development.Through the experimental case,students can obtain an in-depth understandingof the principles and methods of the co-design of ZYNQ-7000software and hardware,as well as the methods ofdata collection and transmission through the communication interface of Arduino's analog,digital,I2C and UARTbuses,which can stimulate students1interest in learning microprocessor structure and embedded system design,and improve the effect of practical teaching.Key words:embedded system design;PYNQ;ZYNQ-7000;Arduino;top-down design随着互联网时代的到来,基于物联网(IoT)技术革命的新经济世界正在形成,智能物联的泛在连接与泛在服务需求促使嵌入式微系统的设计及应用技术进入全新的发展阶段山2】。

弹性SoC方案为ADAS保驾护航

弹性SoC方案为ADAS保驾护航 先进驾驶辅助系统是汽车电子产业成长的主要动能之一,为自动驾驶奠定了深厚的基础。虽然全自动驾驶的实现还有待时日,但相关技术发展已为客户带来显著的好处,汽车OEM已开始推出高度复杂的ADAS系统以提高驾驶的安全性与舒适度,在目前的汽车产业中,先进驾驶辅助系统(ADAS)细分市场的成长得到到很多不同因素推动。

终端消费者也已经认知到ADAS可应用于不同交通状况的优势,尽管到买家愿意花一大笔钱购买汽车周边监控设备前还需要一些时间,但如今似乎已能了解停车辅助系统或自动紧急煞车系统不仅能保命,还能防止低速交通事故,进而减少经济损失。另一项推动因素是全自动驾驶技术的发展。全自动驾驶一开始只是汽车产业技术专家们讨论的一个技术性话题而已,而现在Google等公司已经进军这一领域, 并打造看似不切实际却即将广泛推广的Robocars无人驾驶汽车。虽然Google获得媒体的争相报导,也不断地推动ADAS技术的发展,但其技术如何 运用到OEM汽车生产设置上仍是个问题,而消费者在购买新车时势必考虑到成本和外观等因素。不过,Google等公司展示的所有技术对传统汽车企业造成影响是无庸置疑的,而且增加压力驱使传统汽车企业必须在短期内实现这些技术。 ADAS市场与趋势 ADAS对于汽车产业供应链又会产生什么影响?大多数OEM已经规划了全自动驾驶技术的发展蓝图。换言之,这些OEM已经定义了一系列的应用,打算从现在起到2025年之间陆续向终端消费者推出;并随之在这段期间内不断改进ADAS特性与功能。业界厂商已经看到ADAS技术在汽车上的一些发展演进,例如停车辅助技术一开始只是保险杆转角处内建在停车或倒车时可协助驾驶人预估车距的机械量油尺,接着很快地便出现声音和视觉回馈的超音波传感器,再来后视摄像头开始取代或加强后置超音波传感器,让倒车和停车时更安全。 虽然有些人曾认为超音波传感器技术将会过时,然而采用多达12个超音波传感器的自动停车辅助系统再次复苏,且能准确地测量停车空间,并让驾驶人仅需操控煞车踏板和油门

Zynq7000从零开始之一

Zynq7000从零开始之一使用myir的z-turn开发板,做一个从uart打印hello world的实验,只用PS,不用PL部分,程序从SD卡启动,跑在PS的内部RAM.zynq 7000的PS虽然也是CPU,但是开发方法不像普通的CPU 只需要一个SDK就可以了,它还需要vivado硬件设计软件.所以ZYNQ 7000的PS开发需要两个工具,一个是vivado-- 另一个是SDK-- .1. 打开vivado软件-->Create New Project,工程名和目录:2. next->选RTL Project->Add Sources,Add existing IP和Add constraints界面直接点next3. New Parts界面4. 添加IP,在Flow Navigator的IP Integrator下点Create Block DesignCreate Block Design如下,点OK在Diagram界面点击Add IP双击ZYNQ7 Processing System,添加CPU5. 设置CPU在Diagram界面点击Run Block Automation,不做修改,点Finish就可以。

在Diagram界面双击进入设置界面,我们把所有的接口去掉,只留下FIXED_IO.1> PS-PL Configuration->General->Enable Clock Resets->去掉FCLK_RESET0_N2> PS-PL Configuration->GP Master AXI Interface->去掉 MAXI GP0 interface3> Clock Configuration->PL Fabric Clocks->去掉FCLK_CLK04> DDR Congiguration->去掉Enable DDR5> 设置SD和UART引脚MIO Configuration->Bank1 IO Voltage选LVCMOS 1.8V.MIO Configuration->IO Peripherals->选上SD 0, SD 0的引脚配置:MIO Configuration->IO Peripherals->选上UART 1, UARRT 1的引脚配置:6. 点击OK返回Diagram界面, 把DDR接口删掉,配置之后的界面7. 生成设计文件右击system项->Generate Output Products->直接点Generate, 之后会提示文件生成成功.右击system项->Create HDL Wrapper选下面一项,点OK注意:如果重新修改了CPU配置,上面两个步骤一定要重新实行。

连接与链接

张鹏辉,等:基于ZYNQ-7000 FPGA和AD9361的软件无线电平台设计935系统测试搭建两套SDR平台(一套用于收,一套用于发),AD9361射频板插接到SYNQ数据处理板上,SYNQ 数据处理板通过网线和PC连接。

在PC端运行GNU Radio,执行4.2节描述的802.11a基带数据处理程序。

一台PC运行发送程序,将处理好的基带数据交由SYNQ处理板进行进一步的数据处理后交由AD9361射频发送;另一台PC运行接收程序,射频信号先经过AD9361射频板接收并处理至基带,然后交由FPGA 做初步的基带处理后传给PC,PC进行基带数据处理后完成最终的接收。

发送和接收的两套SDR平台需配置相同的射频频点及通信制式(该实验中使用QAM4)。

发射接收之间相隔5 m放置。

接收端的星座图如图22所示。

共统计了10 000帧数据,误码率为零,说明AD9361数据接口、基于千兆以太网的数据传输等所有数据通路中数据无遗漏、无传输错误,验证了该SDR平台的通信可靠性。

星座图不聚集,说明系统存在一定的噪声。

提高发射功率,提高接收增益会使星座图聚集。

图22 GNU Radio实时基带数据处理测试结果6结语设计了基于AD9361和ZYNQ-7000系列FPGA的软件无线电平台。

PC上使用GNU Radio实现了802.11a 标准的基带数据处理。

最后通过两套SDR设备的搭建,一套发送,一套接收,验证了整个系统的通信可靠性。

该SDR平台对于通信类学生的实践教学和科研工作有重要价值和意义。

参考文献(References)[1] 肖维民,许希斌,朱键,等.软件无线电综述[J].电子学报,1998, 26(2): 65-70.[2] 杨小牛.从软件无线电到认知无线电,走向终极无线电:无线通信发展展望[J].中国电子科学研究院学报,2008, 3(1): 1–7.[3] 杨小牛.软件无线电技术与应用[J].中国数据通信,2004(6):121–121.[4] 陶玉柱,胡建旺,崔佩璋.软件无线电技术综述[J].通信技术,2011,44(1):37–39.[5] 曹悦.软件无线电技术及其应用前景[J].计算机与网络,2006, 36(2): 58–60.[6] 杨宇红,袁焱,田砾,等.基于软件无线电平台的通信实验教学[J].实验室研究与探索,2015, 34(4): 186–188.[7] 李智群,王志功.零中频射频接收机技术[J].电子产品世界,2004(7A): 69–72.[8] Inc.AD.RF Transceiver Rapid prototyping Kit:AD9361 [J/OL].https:///articles/priat/23169-rf-transceiver- rapid-prototyping-kit-al9361.[9] CROCKETT L H.The Zynq book: embedded processing withthe ARM Cortex-A9 on the Xilinx Zynq-7000 all programmable SoC[M]. Strathclyde Academic Media, 2014.[10] 黄伟,罗新民.基于FPGA的高速数据采集系统接口设计[J].单片机与嵌入式系统应用,2006(4): 34–37.[11] BLOSSOM E.GNU Radio: tools for exploring the radiofrequency spectrum[J]. Linux Journal, 2004, 2004(122): 76–81.[12] 曹瀚文,王文博. GNU Radio:开放的软件无线电平台[J].电信快报:网络与通信,2007(4): 31–34.[13] IEEE. IEEE Std 802.11. part 11: Wireless LAN medium accesscontrol (MAC) and physical layer (PHY) specifications C1-1184[S].2007.[14] GAST M S.802.11无线网络权威指南[M].2版.南京:东南大学出版社,2007.·词义辨析·连接与链接连接(connection)是互相衔接之意,指一般在程序设计语言中允许模块之间交互作用;各种功能部件之间为了传递信息所建立的联系,如级联连接、多点连接。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

处理 应 用提 供 了一种 设 计 方案 。 关键词 Z y n q一 7 0 0 0;图像 采 集 ; 实 时 处 理 ;L i n u x

中 图分 类 号

T 码

A

文章编号

1 0 0 7— 7 8 2 0 ( 2 0 1 4) 0 7—1 5 1 — 0 4

( 1 .珠海广播 电视 大学 信息 工程 系 ,广东 珠 海

摘 要

5 1 9 0 0 0 ;2 .华中科技大学 电子与信息工程 系,湖北 武汉 4 3 0 0 7 4 )

4 3 0 0 7 4;

3 . 华 中科技 大学 光 学与电子信息学院 ,湖北 武汉

X i l i n x 公 司推 出的 Z y n q一 7 0 0 0 系列 全 可 编 程 S o C 采 用 了微 处理 器加 可 编 程 逻 辑 的 结 构 ,该 项 目在 Z y n q一

2 . S c h o o l o f El e c t r o n i c s a n d I n f o r ma t i o n E n g i n e e r i n g, Hu a z h o n g Un i v e r s i t y o f S c i e n c e a n d Te c h n o l o g y, W u h a n 4 3 0 0 7 4, C h i n a;

7 0 0 0的 可 编 程 逻 辑 部 分 搭 建 了 图像 采 集 系统 ,在 双 核 处理 器 C o d e x —A 9部 分搭 建 了用 于 处 理 图像 的 实 时 L i n u x 操作系 统 ,使 用 Wi F i 与 外界 进 行 交 互 。 同 时还 介 绍 了使 用 该 平 台进 行 高性 能 图像 处 理 的 方 法 , 为 小 型 机 器 人 的 高 性 能 图 像

s t r u c t u r e . An i ma g e a c q u i s i t i o n s y s t e m i s b u i l t u s i n g t h e p r o ra g mma b l e l o g i c u n i t ,a n d a L i n u x o p e r a t i n g s y s t e m i s b u i l t f o r r e a l — t i me i ma g e p r o c e s s i n g u s i n g t h e Co de x ・ A9 d u a l - c o r e p r o c e s s o r wi t h WI FI or f i n t e r a c t i o n. Th e me t h o d o f

3 . S c h o o l o f Op t i c a l a n d E l e c t r o n i c I n f o ma r t i o n,Hu a z h o n g U n i v e r s i t y o f S c i e n c e a n d T e c h n o l o g y,Wu h a n 4 3 0 0 7 4,C h i n a )

Ab s t r a c t Z y n q - 7 0 0 0 s e r i e s a l l p r o g r a mma b l e S o Cs b y Xi l i n x us e d u a l mi c r o p r o c e s s o r a n d p r o g r a mma b l e l o g i c

Hi g h- S pe e d I ma g e Ac q u i s i t i o n a nd Re a l ・ - t i me Pr o c e s s i ng Sy s t e m Ba s e d o n Zy nq- 7 0 0 0

YANG Xi a o a n .L U0 J i e .S U Hn o .B AO We n b o

( 1 . S c h o o l o f I n f o r ma t i o n E n g i n e e r i n g ,Z h u h a i R a d i o& T V Un i v e r s i t y ,Z h u h a i 5 1 9 0 0 0,C h i n a ;

a 叶技 2 0 1 4 年 第 2 7 卷 第 7 期

El e c t r o n i c S c i . & Te c h . / J u 1 . 1 5. 2 0 1 4

基于 Z y n q一7 0 0 0高 速 图像 采 集 与 实 时处 理 系统

杨晓安 ,罗 杰 ,苏 豪 ,包 文博