PLL的电源管理设计

摘要

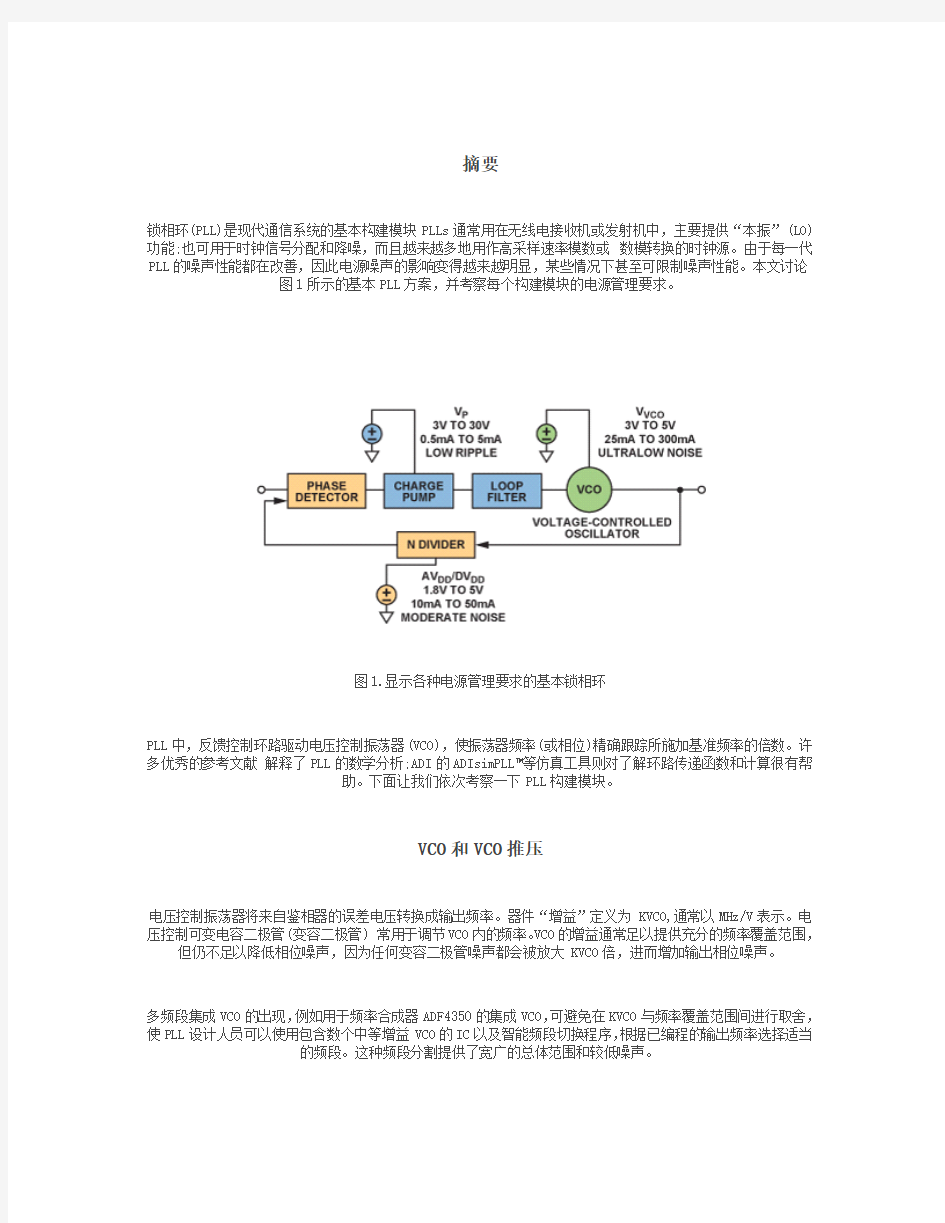

锁相环(PLL)是现代通信系统的基本构建模块PLLs通常用在无线电接收机或发射机中,主要提供“本振”(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。由于每一代PLL的噪声性能都在改善,因此电源噪声的影响变得越来越明显,某些情况下甚至可限制噪声性能。本文讨论图1所示的基本PLL方案,并考察每个构建模块的电源管理要求。

图1.显示各种电源管理要求的基本锁相环

PLL中,反馈控制环路驱动电压控制振荡器(VCO),使振荡器频率(或相位)精确跟踪所施加基准频率的倍数。许多优秀的参考文献解释了PLL的数学分析;ADI的ADIsimPLL?等仿真工具则对了解环路传递函数和计算很有帮

助。下面让我们依次考察一下PLL构建模块。

VCO和VCO推压

电压控制振荡器将来自鉴相器的误差电压转换成输出频率。器件“增益”定义为KVCO,通常以MHz/V表示。电压控制可变电容二极管(变容二极管) 常用于调节VCO内的频率。VCO的增益通常足以提供充分的频率覆盖范围,但仍不足以降低相位噪声,因为任何变容二极管噪声都会被放大KVCO倍,进而增加输出相位噪声。

多频段集成VCO的出现,例如用于频率合成器ADF4350的集成VCO,可避免在KVCO与频率覆盖范围间进行取舍,使PLL设计人员可以使用包含数个中等增益VCO的IC以及智能频段切换程序,根据已编程的输出频率选择适当的频段。这种频段分割提供了宽广的总体范围和较低噪声。

除了需要从输入电压变化转换至输出频率变化(KVCO)外,电源波动也会给输出频率变化带来干扰成分。VCO对电源波动的灵敏度定义为VCO 推压(Kpushing),通常是所需KVCO.的一小部分。例如,Kpushing通常是KVCO 的5%至20%。因此,对于高增益VCO,推压效应增大,VCO电源的噪声贡献就更加举足轻重。

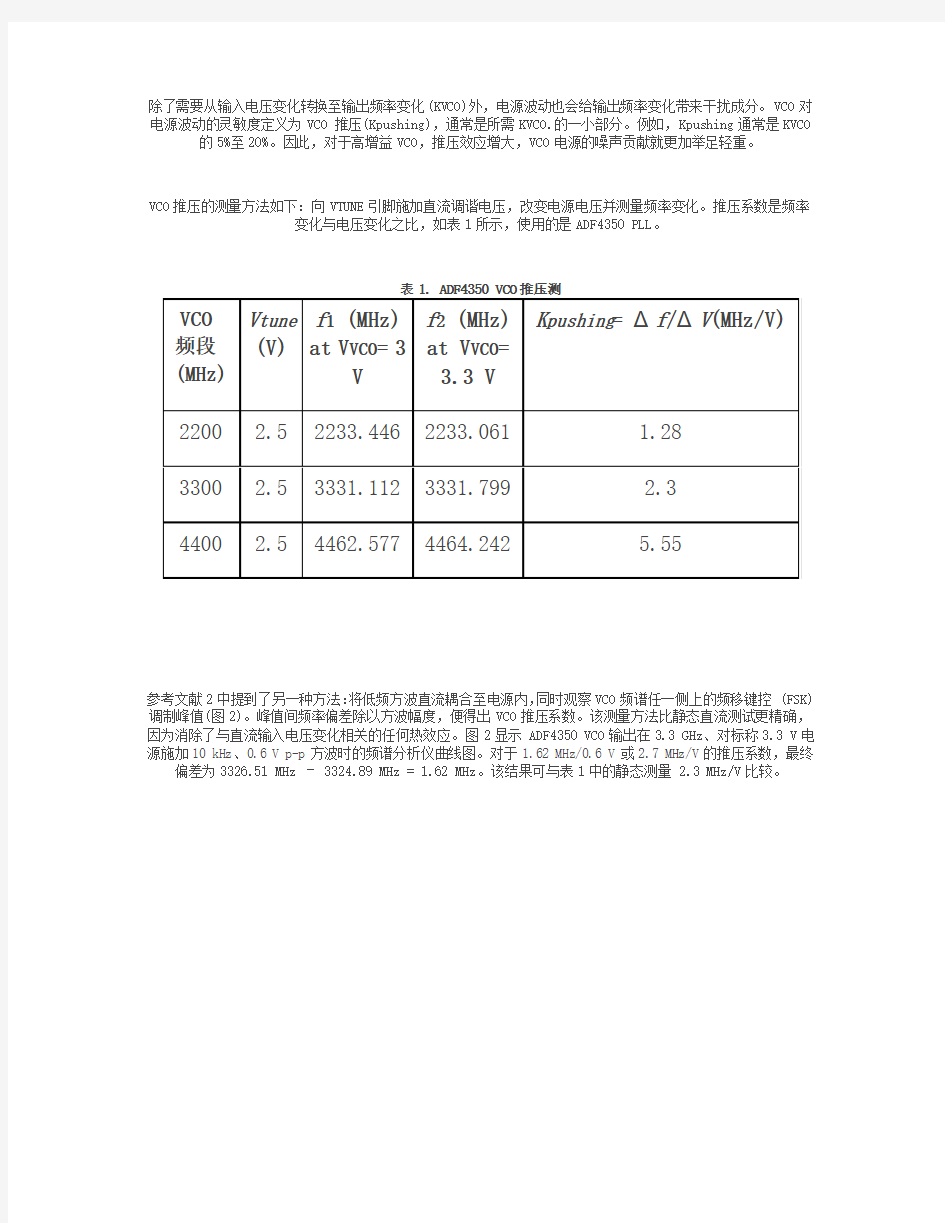

VCO推压的测量方法如下:向VTUNE引脚施加直流调谐电压,改变电源电压并测量频率变化。推压系数是频率变化与电压变化之比,如表1所示,使用的是ADF4350 PLL。

参考文献2中提到了另一种方法:将低频方波直流耦合至电源内,同时观察VCO频谱任一侧上的频移键控 (FSK)调制峰值(图2)。峰值间频率偏差除以方波幅度,便得出VCO推压系数。该测量方法比静态直流测试更精确,因为消除了与直流输入电压变化相关的任何热效应。图2显示 ADF4350 VCO输出在3.3 GHz、对标称3.3 V电源施加10 kHz、0.6 V p-p方波时的频谱分析仪曲线图。对于1.62 MHz/0.6 V或2.7 MHz/V的推压系数,最终偏差为3326.51 MHz – 3324.89 MHz = 1.62 MHz。该结果可与表1中的静态测量 2.3 MHz/V比较。

图2.ADF4350 VCO通过10kHz、0.6v p-p方波响应

电源调制的频谱分析仪曲线图

在PLL系统中,较高的VCO推压意味着VCO电源噪声的增加倍数更大。为尽可能降低对VCO相位噪声的影响,

需要低噪声电源。

参考文献3和参考文献4提供了不同低压差调节器(LDO)如何影响PLL相位噪声的示例。例如,文献中对ADP3334和ADP150 LDO为ADF4350供电时的性能进行了比较。ADP3334调节器的集成均方根噪声为27 μV(40多年来,从10 Hz至100 kHz)。该结果可与ADF4350评估板上使用的LDO ADP150的9 μV比较。图3中可以看出已测量PLL相位噪声频谱密度的差异。测量使用4.4 GHz VCO频率进行,其中VCO推压为最大值(表1),因此属于最差情况结果。ADP150调节器噪声足够低,因此对 VCO噪声的贡献可以忽略不计,使用两节(假定“无噪声”)AA

电池重复测量可确认这一点。

图3.使用ADP3334和ADP150LDO对(AA电池)供电时ADF4350在4.4GHz下的相位噪声比较

图3强调了低噪声电源对于ADF4350的重要性,但对电源或 LDO的噪声该如何要求呢?

与VCO噪声类似,LDO的相位噪声贡献可以看成加性成分LDO(t), 如图4所示。再次使用VCO超额相位表达式

得到:

或者在频域中为:

其中vLDO(f)是LDO的电压噪声频谱密度。

1 Hz带宽内的单边带电源频谱密度SΦ(f)由下式得出:

以dB表示时,用于计算电源噪声引起的相位噪声贡献的公式如下:

(1)

其中 L(LDO)是失调为f时,调节器对VCO相位噪声(以dBc/Hz表示)的噪声贡献; f; Kpushing是VCO推压系数,以Hz/V表示;vLDO(f)是给定频率偏移下的噪声频谱密度,以V/√Hz表示.

图4.小信号加性vco电源噪声模型

在自由模式VCO中,总噪声为 LLDO值加VCO噪声。以dB表示则为:

例如,试考虑推压系数为10 MHz/V、在100 kHz偏移下测得相位噪声为–116 dBc/Hz的VCO:要在100 kHz下不降低VCO噪声性能,所需的电源噪声频谱密度是多少?电源噪声和VCO噪声作为方和根添加,因此电源噪声应比VCO噪声至少低6 dB,以便将噪声贡献降至最低。所以LLDO应小于–122 dBc/Hz。使用公式1,

求解vLDO(f),

在100 kHz偏移下,vLDO(f) = 11.2 nV/√

给定偏移下的LDO噪声频谱密度通常可通过LDO数据手册的典型性能曲线读取。

当VCO连接在负反馈PLL内时,LDO噪声以类似于VCO噪声的方式通过PLL环路滤波器进行高通滤波。因此,上述公式仅适用于大于PLL环路带宽的频率偏移。在PLL环路带宽内,PLL可成功跟踪并滤 LDO噪声,从而降

低其噪声贡献。

LDO滤波

要改善LDO噪声,通常有两种选择:使用具有更少噪声的LDO,或者对LDO输出进行后置滤波。当无滤波器的噪声要求超过经济型LDO的能力时,滤波选项可能是不错的选择。简单的LC π滤波器通常足以将带外LDO噪

声降低20 dB(图5)。

图5.用于衰减LDO噪声的LCπ滤波器

选择器件时需要非常小心。典型电感为微亨利范围内(使用铁氧体磁芯),因此需要考虑电感数据手册中指定的饱和电流(ISAT), 作为电感下降10%时的直流电平。VCO消耗的电流应小于ISAT. 有效串联电阻(ESR) 也是一个问题,因为它会造成滤波器两端的IR压降。对于消耗300 mA直流电流的微波VCO,需要ESR小于0.33 ?的电感,以产生小于100 mV的IR压降。较低的非零ESR还可抑制滤波器响应并改善LDO稳定性。为此,选择具有极低寄生ESR的电容并添加专用串联电阻可能较为实际。上述方案可使用可下载的器件评估器如NI Multisim

?在SPICE 中轻松实现仿真。 .

电荷泵和滤波器

电荷泵将鉴相器误差电压转换为电流脉冲,并通过PLL环路滤波器进行积分和平滑处理。电荷泵通常可在最多低于其电源电压(VP)0.5 V的电压下工作。例如,如果最大电荷泵电源为5.5 V,那么电荷泵只能在最高5 V 输出电压下工作。如果VCO需要更高的调谐电压,则通常需要有源滤波器。有关实际PLL的有用信息和参考设计,请参见电路笔记CN-0174,5,处理高压的方式请参见利用高压VCO设计高性能锁相环,”6该文章发表于模拟对话第43卷第4期(2009)。有源滤波器的替代方案是使用PLL和针对更高电压设计的电荷泵,例如ADF4150HV ADF4150HV可使用高达30 V的电荷泵电压工作,从而在许多情况中省去了有源滤波器。

电荷泵的低功耗使其看似颇具吸引力,可使用升压转换器从较低的电源电压产生高电荷泵电压,然而与此类DC-DC转换器相关的开关频率纹波可能在VCO的输出端产生干扰杂散音。高PLL杂散可能造成发射机发射屏蔽测试失败,或者降低接收机系统内的灵敏度和带外阻塞性能。为帮助指导转换器纹波的规格,使用图6 的测量设置针对各种PLL环路带宽获得全面电源抑制曲线图与频率的关系。

图6.测量电荷泵电源抑制的设置

17.4 mV (–22 dBm)的纹波信号经交流耦合至电源电压,并在频率范围内进行扫描。在每一频率下测量杂散水平,并根据–22dBm输入与杂散输出电平间的差异(以dB表示)计算PSR。留在适当位置的0.1 μF和1 nF电荷泵电源去耦电容为耦合信号提供一定衰减,因此发生器处的信号电平增加,直至在各频率点下引脚上直接测得

17.4 mV。结果如图7所示。

在PLL环路带宽内,随着频率增加,电源抑制最初变差。随着频率接近PLL环路带宽,纹波频率以类似于基准噪声的方式衰减,PSR改善。该曲线图显示,需要具有较高开关频率(理想情况下大于1 MHz)的升压转换器,以便尽可能降低开关杂散。另外,PLL环路带宽应尽可能降至最低。

1.3 MHz时, ADP1613就是一款合适的升压转换器。如果将PLL环路带宽设置为10 kHz,PSR可能达到大约90 dB;环路带宽为80 kHz时,PSR为50 dB。首先解决PLL杂散水平要求后,可以回头决定升压转换器输出所需的纹波电平。例如,如果PLL需要小于–80 dBm的杂散,且PSR为50 dB,则电荷泵电源输入端的纹波功率需小–30 dBm,即20 mV p-p。如果在电荷泵电源引脚附近放置足够的去耦电容,上述水平的纹波电压可使用纹波滤波器轻松实现。例如,100 nF去耦电容在1.3MHz时可提供20 dB以上的纹波衰减。应小心使用具有适当电压额定值的电容;例如,如果升压转换器产生18 V电源,应使用具有20V或更高额定值的电容。

图7.ADF4150HF电荷泵电源抑制曲线图

使用基于Excel的设计工具ADP161x.可以简化升压转换器和纹波滤波器的设计。图8显示用于5 V输入至20 V 输出设计的用户输入。为将转换器级输出端的电压纹波降至最低,该设计选择噪声滤波器选项,并将VOUT纹波场设定为最小值。高压电荷泵的功耗为2 mA(最大值),因此OUT 为10 mA以提供裕量。该设计使用20 kHz 的PLL环路带宽,通过ADF4150HV评估板进行测试。根据图7,可能获得约70dB的PSR。由于PSR极佳,此设置未在VCO输出端呈现明显的开关杂散(< –110 dBm),即使是在省去噪声滤波器时。

图8.ADP1613升压转换器EXCEL设计工具

作为最终实验,将高压电荷泵的PSR与有源滤波器(目前用于产生高VCO调谐电压的最常见拓扑结构)进行比较。为执行测量,使用无源环路滤波器将幅度为1 V p-p的交流信号注入ADF4150HV的电荷泵电源(VP)与图6的测量设置相同。后以有源滤波器代替相等带宽的无源滤波器,重复相同的测量。所用的有源滤波器为CPA_PPFFBP1

型,如ADIsimPLL所述(图9)。

图9.ADlsimPLL中CPA_PPFFBP1滤波器设计的屏幕视图.

为提供公平的比较,电荷泵和运算放大器电源引脚上的去耦相同,即10 μF、10 nF和10 pF电容并联。测量结果显示于图10中:与有源滤波器相比,高压电荷泵的开关杂散水平降低了40 dB至45 dB。利用高压电荷泵改善的杂散水平部分可解释为通过有源滤波器看到的环路滤波器衰减更小,其中注入的纹波在第一极点之后,

而在无源滤波器中注入的纹波位于输入端

图10.有源环路滤波器与高压无源滤波器的电源纹波电平

最后一点:图1所示的第三电源电轨(分压器电源,AVDD/DVDD—与VCO和电荷泵电源相比具有较宽松的电源要求,因为PLL(AVDD)的RF部分通常是具有稳定带隙参考偏置电压的双极性ECL逻辑级,所以相对不受电源影响。另外,数字CMOS模块本质上对电源噪声具有更强的抵抗力。因此,建议选择(DVDD)能够满足此电轨电压和电流要求的中等性能LDO,并在所有电源引脚附近充分去耦;通常100 nF和10 pF并联就够了。

结束语

以上已讨论主要PLL模块的电源管理要求,并针对VCO和电荷泵电源推算出规格。ADI公司为电源管理和PLL IC 提供多种设计支持工具,包括参考电路和解决方案,还有各种仿真工具,如ADIsimPLL和 ADIsimPower. 了解电源噪声和纹波对PLL性能的影响后,设计人员可以回头推算电源管理模块的规格,进而实现性能最佳的PLL

设计。

https://www.360docs.net/doc/b116361053.html,/天域苍穹

DCDC开关电源管理芯片的设计

DC-DC开关电源管理芯片的设计 引言 电源是一切电子设备的心脏部分,其质量的好坏直接影响电子设备的可靠性。而开关电源更为如此,越来越受到人们的重视。目前的计算机设备和各种高效便携式电子产品发展趋于小型化,其功耗都比较大,要求与之配套的电池供电系统体积更小、重量更轻、效率更高,必须采用高效率的DC/ DC开关稳压电源。 目前电力电子与电路的发展主要方向是模块化、集成化。具有各种控制功能的专用芯片,近几年发展很迅速集成化、模块化使电源产品体积小、可靠性高,给应用带来极大方便。 从另一方面说在开关电源DC-DC变换器中,由于输入电压或输出端负载可能出现波动,应保持平均直流输出电压应能够控制在所要求的幅值偏差范围内,需要复杂的控制技术,于是各种 PWM控制结构的研究就成为研究的热点。在这样的前提下,设计开发开关电源DC-DC控制芯片,无论是从经济,还是科学研究上都是是很有价值的。 1. 开关电源控制电路原理分析 DC-DC变换器就是利用一个或多个开关器件的切换,把某一等级直流输入电压变换成另—等级直流输出电压。在给定直流输入电压下,通过调节电路开关器件的导通时间来控制平均输出电压控制方法之一就是采用某一固定频率进行开关切换,并通过调整导通区间长度来控制平均输出电压,这种方法也称为脉宽调制[PWM]法。 PWM从控制方式上可以分为两类,即电压型控制(voltage mode control)和电流型控制(current mode control)。电压型控制方式的基本原理就是通过误差放大器输出信号与一固定的锯齿波进行比较,产生控制用的PWM信号。从控制理论的角度来讲,电压型控制方式是一种单环控制系统。电压控制型变换器是一个二阶系统,它有两个状态变量:输出滤波电容的电压和输出滤波电感的电流。二阶系统是一个有条件稳定系统,只有对控制电路进行精心的设计和计算后,在满足一定的条件下,闭环系统方能稳定的工作。图1即为电压型控制的原理框图。 图1 电压型控制的原理框图 电流型控制是指将误差放大器输出信号与采样到的电感峰值电流进行比较.从而对输出脉冲的占空比进行控制,使输出的电感峰值电流随误差电压变化而变化。电流控制型是一个一阶系统,而一阶系统是无条件的稳定系统。是在传统的PWM电压控制的基础上,增加电流负反馈环节,使其成为一个双环控制系统,让电感电流不在是一个独立的变量,从而使开关变换器的二阶模型变成了一个一阶系统。信号。从图2中可以看出,与单一闭环的电压控制模式相比,电流模式控制是双闭环控制系统,外环由输出电压反馈电路形成,内环由互感器采样输出电感电流形成。在该双环控制中,由电压外环控制电流内环,即内环电流在每一开关周期内上升,直至达到电压外环设定的误差电压阂值。电流内环是瞬时快速进行逐个脉冲比较工作的,并且监测输出电

电池电源管理系统设计

电源招聘专家 我国是一个煤矿事故多发的国家,为进一步提高煤矿安全防护能力和应急救援水平,借鉴美国、澳大利亚、南非等国家成功的经验和做法,2010年,国家把建设煤矿井下避难硐室应用试点列入了煤矿安全改造项目重点支持方向。 为了满足井下复杂的运行环境及井下避难硐室对电池电源运行稳定、安全可靠、大电流输出等关键要求,研发了基于MAX17830的矿用电池电源管理系统。 1 总体技术方案 根据煤矿井下的环境及井下避难硐室对电池电源运行稳定、安全可靠、大电流输出等关键要求,结合磷酸铁锂电池的特性,采用MAX17830作为矿用电池管理系统的采集与保护芯片。 本矿用电池电源管理系统由五部分组成,分别为显示模块、管理模块、执行机构、电池组、防爆壳。整个电池电源管理系统共设有4对接线口:24 V直流输出端口、24 V直流充电端口、485通信端口和CAN通信端口[1-2]。 本矿用电池电源管理系统的工作流程如图1所示。 2 电池电源管理系统硬件设计 2.1 器件选择及布局 本矿用电池电源管理系统设计所采用的主要器件如表1所示。 按照器件的功能及电池管理系统的特点,对器件进行布局设计,器件布局情况如图2所示。 2.2 核心电路解析 2.2.1 MAX17830介绍 MAX17830芯片由美国的美信半导体公司生产,包含12路电压检测通道、12路平衡电路控制引脚及2路NTC温度传感器。在本电池电源管理系统中使用了8路电压检测通道、8路平衡电路控制引脚和2路NTC温度传感器。MAX17830采集8个单体电池的电压并使用IIC通信协议与CPU通信,将采集的数据发送给CPU,接受CPU的控制[3-4]。 2.2.2 电池电压采集与过充保护电路 此电路围绕着MAX17830而设计,负责整个电池组单体电池的电压采集、过充保护、平衡管理等,其电路设计的原理图如3所示。 3 电池电源管理系统软件设计 3.1 软件基本功能 为了保证电池电源系统的稳定,设计电池电源管理系统软件的基本功能如下[5]: (1)动态信息的采样,对单体电压、单体温度、电池组电流、电池组电压进行采样;(2)电管理,根据系统动态参数对充电过程、放电过程、短路情况进行报警、主动保护多级管理措施; (3)热管理,电池单体高于或低于指定界限时电池电源管理系统将采取保护措施并报警;(4)均衡管理,充、放电过程中可对单体电池持续有效地提供高达70 mA的均衡电流,每块单体电池设有一路均衡电路; (5)数据管理,使用CAN/485通信协议可实时读取、调用系统存储的数据及管理系统工作状态。详实记录过流、过压、过温等报警信息,作为系统诊断的依据; (6)电量评估,长时间精准剩余电量估计,实验室SoC估计精度在97%以上(-40 ℃~

智能手机电源管理模块的设计

龙源期刊网 https://www.360docs.net/doc/b116361053.html, 智能手机电源管理模块的设计 作者:芦昱昊 来源:《电子技术与软件工程》2017年第04期 摘要随着国民生活质量的不断提高,电子产品更新换代的速度也越来越快。通讯产品中的电源动力系统一直是开发者关注的重点,也是用户选择智能手机的关键选项,因此对智能手机电源管理模块的设计分析是十分必要的。 【关键词】智能手机电源模块设计管理 手机行业的发展变化可谓是日新月异,近年来肉眼可见的黑白屏到彩色屏、仅有通话功能到目前的各种实用应用,都是智能手机功能进步的体现。然而这些复杂功能的实现都是需要稳定的电源系统作为支持的,因此开展电源模块的电压以及效率设计管理是为智能手机的良好发展前景奠定基础。 1 智能手机电源管理模块的设计原则 智能手机的设计过程是设计师明确消费者对设备要求下进行的,因此需要从体积、重量、续航时间上等多方面进行详细考虑。智能手机体积的缩小处理是针对系统集中功能和元件封装技术的体现,因此需要考虑到减小PCB板后产生的各种影响。在体积和重量都有限制的情况下,提高电池的容量和密度是最佳的创新选择,同时注重电源系统在工作状态下的转化频率,也是处理续航时间的主要方案。由此可知,电源管理模块的转化率和能耗是手机改革重点,手机厂家需要从电能转化的效率和电源的使用效率两方面提高设备的科技含量,制造出具备高性价比和满足消费者需求的优势产品。 2 智能手机电源管理模块的设计分析 2.1 PMU 市面上很多电子产品需要根据实际功能调节出不同电压的电源,也就意味着电池在供电的同时还需要根据芯片迅速转换电压,转换期间的功率损耗也应当保持在规定范围之内,同时该电源模块还需要维持电源的充电安全。这样的新型电源模块电路被称作是电源管理单元,英文缩写为PMU,是为提高电源转化效率和降低能耗的电源管理方案。PMU的构架分为集中式和分布式,但是二者共同存在的几率很小,设计者需要在系统划分之初决定好使用哪种方案。集中式是仅执行PMU附近的单一处理器进行电压调节和电源切换工作,而分布式系统则是作用于每一个电源子系统上。二者的选择重点是从智能手机应用的数量和响应速度的要求,同时还要考虑到电源模块管理过程中的间隔距离。通过比较来看,PMU分布式的方案较集中式的灵活一些,只需要在系统之间加入一根电源轨,作为所有外围的电源连接线,那么每一个外围电

PLL设计关键基础及基本参数确定方法

PLL设计关键基础因素 锁相环的瞬态特性通常是一个非线性过程,并且不能够简单的用式子来表示。但是当环路带宽不大于参考时钟频率的1/10时,离散模型可以用连续时间模型(s域)较好地近似。 PLL在锁定状态下的包括每一个模块的传递函数的线性模型,以下理论中所有的公式都是没有分频电路(N)的基础上进行的分析。 如下图所示, 这个模型是用来证明总的相位特性的传递函数。因此,PD可以表示成一个减法器。 假设LPF的电压传递函数为。PLL的开环传递函数为: 闭环传递函数为: 假设低通滤波器为一个最简单的一阶无源滤波器,如下图所示

那么LPF的电压传递函数为为 其中,带入LPF传递函数得 这是一个二阶系统,一个极点是vco提供的,另外一个极点是由LPF提供的。 为环路增益,单位为rad/s。 为了方便分析PLL的动态特性,将PLL闭环传输函数的分母化为二阶函数形式: 其中为衰减因子,为系统的自然振荡频率。 则公式最终化为: 其中

自然频率是低通滤波器的-3dB带宽和环路增益的几何平均值,从近似的角度来看,可以认为是环路的增益带宽积。 进行波特图分析时(开环分析闭环),开环传输函数的单位增益带宽为 相位裕度为: 在一个好的二阶系统中,通常大于0.5,最好使其等于0.707,这样有一个优化的频率响应。 PLL闭环传输函数化为二阶函数形式得:如果输入偏差相位变化慢,则输出相位偏差能够跟上其变化:如果输入相位偏差变化快,输出相位偏差变化会比输入小。 定义“输入/输出相位差传递函数(phase error transfer function)”为: 则 为了更好的分析信号的传输特性,我们假设输入的信号相位有一个阶跃,则最终系统稳定下来后,输出信号的相位变化为

远程电源管理系统设计

远程电源管理系统设计 作者:吴能伟 来源:《现代电子技术》2013年第02期 摘要:在海军武器着靶试验中,为了保护实测数据和提高光电设备的可靠性,利用Atmegal61丰富的资源和接口,设计一套远程电源管理系统。该系统以锂电池组作为备用电源,依靠单片机处理远控中心发送的目标测量数据及控制命令,对固态继电器的工作状态进行控制。试验结果表明该系统能自主完成光电设备电源的远程管理,获取完整的目标实况景象,具有一定的现实意义。 关键词:AVR单片机;固态继电器;电源管理;串行通信 中图分类号:TN911?34;TP273 文献标识码:A 文章编号:1004?373X(2013) 02?0162?03 光电设备具有低成本、易布站、高精度的优点,逐步成为海军武器试验中获取空间目标飞行状态和轨迹的主力军[1]。随着精确制导、远程打击等高技术兵器武器的出现,要检验和鉴定此类目标的性能和威胁,不仅需要获取目标的空间坐标,同时要求测量目标着靶时的姿态信息。而目标着靶是一个瞬态过程,不易捕捉,因此常用高速光电设备在靶船上实时获取高质量的目标运动图像序列[2?3],经事后处理得到目标的运动参数。不难看出图像数据直接决定试验的成败,因此有必要对设备的工作状态及电源等情况进行远程监视和管理[4]。 该平台以AVR单片机为核心,利用2节串联的充电锂电池作为备用电源[5],依靠外围接口获取目标的实时信息(实测弹道数据、T0时刻等)。 在光电设备工作异常或落水时,控制固态继电器(Solid State Relay,SSR)实现系统的远程重启和关机[6],为获取及保护目标的实时图像数据提供有力保障,因而具有重要的现实意义。 AVR单片机所需的电源电压为2.7~5.5 V,为了简化电路设计,提高系统的可靠性,为AVR单片机设计外部基准电压为5 V,利用L7805防止电池出现过用现象。 2.2 主控电路 主控电路如图3所示,ATmegal61单片机有1个可编程的同步/异步串行接口USART,可以满足与远控中心的通信要求,2个具有比较模式的灵活定时/计数器,可以完成延时时间的计算,预留的8路10位ADC端口可以扩展其他功能。为了满足嵌入式的设计要求,选用易于安装在电路板的G6B?2014P?US固态继电器,实现两路直流电源的同步控制。而继电器的驱动需要控制系统具有大电流的输出能力,ULN2003是高压大电流达林顿晶体管系列产品,可以很好地满足要求[11]。

超顺手的公式之pll

M2 U M’U2 M U M2 M2 U’ M’U2 M U’ M2 巧计方法:遇到三棱换,不管三七二十一先M2,做M2的同时观察魔方左右两面,即可观察出是顺时针还是逆时针的三棱换。如果是顺时针,接下来就逆时针转U,反之,则顺时针转U。紧接着不管三七二十一M’U2 然后和之前一样,顺时针三棱换就转逆时针的U 逆时针三棱换就转顺的U,M2收尾。 PLL03,04 M2 U M2 U2 M2 U M2 M2 U M2 U’(M’E2)2注:E2指的是上层与下层的夹层旋转180° M2 U’ M2 U (M’E2)2方向不同U与U’互换 PLL05,06 05.(R U R' F') ( r U R' U') (r' F R2 U' R') 06. (R U)( R'2 F')(r U R U')(r' F R U' R') 是倒过来做的一样顺

07.x'(RU'R'D)(RUR'D')(RUR'D)(RU'R'D') (R2 UR'd') (R U R' U' R U R' U')( R U R' F U' F2) 08.(R U R' U')(R' F)(R2 U' R' U') (R U R' F') PLL09,10,11 09.(R'U'F')(RU R' U')(R' F)(R2 U' R' U' )(R U R' UR) 10.(R'UR'U)d(R'F'R2U')(R'UR'F)(RF) 11.F(R U'R' U')(R U R' F')(R U R' U') (R' F R F') Pll12,13 12.(R’U2)(RUR’)z(R2UR’DRU’) 13.(R U R'F')(R U R'U')(R'F R2 U'R'U') PLL14,15 14.(R' U2)(R U'U')(R' F)(R U R' U') (R'F')(R2 U')

PLL(锁相环)电路原理及设计 [收藏]

PLL(锁相环)电路原理及设计[收藏] PLL(锁相环)电路原理及设计 在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。 一PLL(锁相环)电路的基本构成 PLL(锁相环)电路的概要 图1所示的为PLL(锁相环)电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。 此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。 (将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。) 利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。 PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。 只要是基准频率的整数倍,便可以得到各种频率的输出。 从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。在此,假设基准振荡器的频率为fr,VCO的频率为fo。 在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。相反地,如果frlt;fo时,会产生负脉波信号。

电源管理模块

电源管理模块 手指康复机器人的数字电路部分需要直流电源供电,故电源管理模块首先采用的开关电源将220v 的交流电转换为直流电压,再利用低压线性稳压器为各个子模块供电。 为了避免模拟信号与数字信号地相互干扰,将交流电压转换为两个独立的直流电源,再分别为模拟电路和数字电路的电源供电。电源管理系统拓扑结构如下: 具体实现如下: ① +12V 转+8V 采用的是LM7808,这是一块三端集成的稳压电路,能够准确的降压到+8V 。电路两端的电容作用都为滤波,用来平滑电压与提高抗干扰能力。其中输出端并联220uF/25V 的电解电容,它自谐频率小,可以起到储能滤波的功能,消除低频干扰。但是由于大电容的电解电容自身存在一定的电感,对于高频信号以及脉冲干扰信号无法有效滤除,故并联一个或几个容值比较小的陶瓷电容,以达到滤除高频干扰信号的作用。 220V 交流电 12V 直流电源 LM2596S5 24V 直流电源 MRF 7808 NE555 LM117-3.3 7414 7474 ARM 外围电路 AD REF TLV5620 LT3080 LM358 WD5-24S5 直流电机电源 HCPL2630 TLP185 3.3 12 5 8 -8 24 5

②+12V转-8V采用NE555芯片,这是一款将模拟功能和逻辑功能很好的结合在一起的芯片,应用的范围十分广泛。 其内部结构如上,当NE555的第三脚输出高电平,通过D1向C1充电,电压可达11V。当NE555输出为低电平时,D1被C2反偏截止。C2向C3转移电荷,重复多次后C3电压达8V,相对地线则输出视为-8V ③+12V转+5V采用的是开关型集成稳压芯片LM2596,它内含固定频率振荡器,以及基准稳压器,并具备完善的保护电路、热关断电路、电流限制等。

三阶魔方单手PLL公式

说明:无法理解符号意思的或看不懂图案的请自觉学习初级玩法。 z U’ R U’ R’ U’ R’ U’ R U R U2 R U’ R U R U R U’ R’ U’ R2 z U z’ R U2 R’ z U’ z’ x’ u’ U’ R2 U z’ R U R’ U’ R U’ R U R U’ R’ U R U R2 U’ R’ x’ R U’ R D2 R’ U R D2 z’ U2 x’ R2 D2 R’ U’ R D2 R’ U R’ x’ R U’ R’ D R U R’ D’ R U R’ D R U’ R’ D’ R2 U’ R2 U’ R2 U y’ R U R’ B2 RU’ R’

R U R’ U’ R’ F R2 U’ R’ U’ R U R’ F’ R’ U R’ U’ y R’ F’ R2 U’ R’ U R’ F R F R’ U2 R’ U’ y R’ F’ R2 U’ R’ U R’ F R U’ F R U2 R’ U’ R U2 L’ U R’ U’ L z U’ R D’ R2 U R’ U’ R2 U D R’ U2 R U2 R’ F R U R’ U’ R’ x U’ R2 R U2 R’ U2 R x’ U’ R’ x U’ R U x’ R U R2 R2 u’ R U’ R U R’ D y R2 y R U’ R’

R U R’ y’ R2 u’ R U’ R’ U R’ D y R2 R’ U’ R y R2 z’ R x’ U’ z U R U’ R u’ R2 R2 z’ R x’ U’ z U R’ U’ R u’ R2 yz U’ R U z U z’ U’ R U2 z U’ R U z’ R’ U’ R U2 z U’ R D’ z U’ R z’ R’ U2 z U R’ U’ z’ R U R’ U2 L U’ R z U’ R D R’ U R U’ R z’ R’ U’ L U2 R U2 R’ R2 U’ R’ U R U’ x’ U’ z’ U’ R U’ R’ U’ z U R U’ R’ U R U’ R2 zx U’ R’ U R y’ R U R’ U’ R2

MAX1647电源管理电路设计详解

MAX1647电源管理电路设计详解 随着二极管泵浦全固态激光器相关技术的不断发展,它在工业、国防 科研、生物医学工程等领域的应用越来越广泛,对其输出功率、可靠性要求也 不断提高。作为二极管泵浦全固态激光器的重要组成部分的电源,其可靠性、 稳定性也就显得格外重要。二极管泵浦全固态激光器的电源功率较大,输出为 大电流、低电压,工作脉冲频率较高(可达1kHz),输出电流、电压的稳定性要求很高。微小的电流扰动将影响激光器的出光质量,不当的保护可能引起巨 大的损失。针对这些特点,我们选择功能强大的电源管理芯片MAX1647作为 整个系统控制的核心部分,设计出完全满足要求的大功率激光器电源。 MAX1647电源管理芯片介绍 MAX1647是MAXIM公司的新型电源管理芯片,其内部结构如 在MAX1647的电压调整环中,通过SMBUS总线,经内部10位DAC 设置预置电压,负载电压与预置电压通过GMV误差放大器进行比较放大后的 误差信号输出到CCV端口,然后送到一个由二选一电路组成的恒流/恒压自动 转换电路的一个端子上,其中由CCV端口输出的误差信号由内部钳位电路限 制在1/4到3/4参考电压之间的;与电压调整环工作原理相类似,被钳位的电 流误差信号由CCI端口送到自动转换电路的另一个端子上;利用PWM控制器,把电压/电流误差信号转换为脉宽调制信号,用以驱动两个N沟道MOSFET管,经同步整流、滤波器滤波后,得到所需的输出信号。 MAX1647的输出特性曲线如整体电路设计 整体电路设计框 MAX1647电源管理芯片是整个系统的控制核心部分,它完成恒流、恒 压及相互之间自动转换的功能。但MAX1647的最大输出4A,不足以达到设计

毕业设计论文:PLL锁相环电路

摘要 随着通信及电子系统的飞速发展,促使集成锁相环和数字锁相环突飞猛进。 本次毕业设计的主要任务是,采用0.18μm CMOS工艺,设计实现一个基于改进的鉴频鉴相器,压控振荡器,环路滤波器的全集成的CMOS PLL锁相环电路,设计重点为PLL锁相环电路的版图设计,设计工具为Laker。 本论文介绍了PLL锁相环电路的基本原理以及其完整的版图设计结果。本次设计表明,采用该方案实现的锁相环电路主要功能工作正常,初步达到设计要求。 关键词:PLL锁相环电路,鉴频鉴相器,压控振荡器,环路滤波器,版图设计,0.18μm CMOS工艺

Abstract With the development of the communications and electronic systems, the technology of the integrated PLL and digital PLL develops rapidly. The main task of graduation is to design and realize a fully integrated CMOS PLL circuit which is based on an improved phase detector, VCO, loop filter using the 0.18μm CMOS technology. The design focus on the layout of the PLL circuit, and the design tools is the Laker. This paper introduces the basic principles of PLL phase locked loop circuit and its comprehensive layout results. This design shows that the program implemented by the main function of PLL circuit is working well, and it meets the design requirements. Key words:PLL phase locked loop circuits, popularly used phase detectors, discrimination, VCO loop filter, layout design, 0.18 μm CMOS process

电源管理芯片MAX1631,1632资料电路图

PART TEMP. RANGE BOARD TYPE MAX1630EVKIT-SO 0°C to +70°C Surface Mount MAX1631EVKIT-SO 0°C to +70°C Surface Mount MAX1632EVKIT-SO 0°C to +70°C Surface Mount 19-1211; Rev 0; 3/97 MAX1630/MAX1631/MAX1632 Evaluation Kits _______________General Description The MAX1630/MAX1631/MAX1632 evaluation kits (EV kits) each consist of one of three preassembled and tested evaluation boards (EV boards) that embody the standard application circuits. The MAX1630 and MAX1632 EV boards provide the triple-output 3.3V/5V/ 12V circuit, and the MAX1631 EV board provides the dual-output 3.3V/5V circuit. All three use the same PC board but have different components to accommodate different input voltage ranges. The main differences between the MAX1630 and MAX1632 EV boards are in the turns ratio (1:4 or 1:2.2) and in the location of the transformer connection (3.3V side or 5V side). Connecting the transformer to the 3.3V side allows lower input voltage. Connecting the transformer to the 5V side provides slightly better efficiency and lower stress voltages. These circuits are configured to deliver up to 3A of out- put current on each of the main PWM outputs with greater than 90% efficiency. The MAX1630/MAX1631/ MAX1632 EV kits can also be used to evaluate other output voltages. ____________________________Featur es Battery Range: 5.2V to 20V (MAX1630) 5.2V to 28V (MAX1631) 6.5V to 28V (MAX1632) Outputs: 3.3V at 3A 12V at 120mA 5V at 3A 5V at 30mA Keep-Alive 1:4 Transformer (MAX1630) 1:2.2 Transformer (MAX1632) Adjustable 2.5V to 5.5V Outputs (optional resistor divider) Precision 2.5V Reference Output Oscillator Sync Input Low-Noise Mode Control Input (SKIP ) Power-Good Monitor (RESET output) Fully Assembled and Tested ______________Or dering Information Common to All Thr ee EV Kits Maxim Integrated Products 1

探究大型风力发电机组变桨后备电源管理系统设计120

探究大型风力发电机组变桨后备电源管理系统设计 摘要:当今我国风力发电技术变得愈加成熟,在大型风力发电机组变桨系统当中,为了保障整个系统的安全性与可靠性,通常都要配置变桨后备电源,这就需 要做好后备电源管理系统设计工作,提高风力发电机组运行的有效性。基于此, 本文首先提出蓄电池在变桨控制系统中的应用,进而从软硬件两个方面提出后备 电源管理系统设计。 关键词:大型风力发电机组;后备电源;管理系统;变桨;设计 引言 工业的不断发展,虽然经济有所提升,但是资源、能源紧缺问题却愈加严重。为了能够实现可持续发展道路的战略,加强可再生能源的研究与研究已经成为了 必然趋势,降低对传统能源的依赖性。风力发电是继火力发电、水利发电的又一 大发展体系,是当今电力领域研究的热点话题。风力发电技术作为当今能源领域 的新研究方向,已经从最初的几十千瓦逐渐升到了兆瓦级。但总体上来说,我国 风力发展技术还有很大的发展空间,特别是对于大型风力发电机组变桨问题来说,为了保证风力发电系统运行安全,需要全面加强后备电源管理工作,因此加强后 备电源管理系统设计尤为重要。 1蓄电池在变桨控制系统中的应用原理 结合能量守恒的原理,在能源转化当中,会在数量、时间、物质形态产生一 定差异。储能技术就是一种能量转化的“中介”,通过能量存储与释放,从而提高 能量转化与应用的灵活性。蓄电池作为化学储能的一种,具有易存储、易运输的 优势,在当今风电领域中的应用十分广泛。 为了可以提高大型风力发电系统的可靠性,变桨控制系统电源通常要设置备 用方案。后备电源主要是起到了紧急收浆的作用。如果大型风力发电机组产生了 故障问题,一组蓄电池可以为紧急变桨控制提供动力,在直流母线上并联电池组,之后统一安装到变频器上,在风电机正常运行当中,只需要通过浮点来保持电压 即可,假如在运行当中因为故障断电,系统会自动将直流电传输给变频器,变频 器通电之后即可实现相应功能,带动伺服电机运行实现收浆。 2硬件系统设计 2.1电源电路设计 (1)电池组串充电源 电源作为风电机的重要驱动装置,保证电源运行质量可以确保设备运行效率 以及运行安全性。这就需要保证电源电路设计的科学性。大部分电源管理系统都 是采用了4节电池组串充方法,电压为52VDC,因此主要的电源电路中需要融入 +52V电源电路。在实践应用当中需要采用MC34063芯片,包含了DC/DC变换器 各种功能,由单片机统一控制电路。 (2)其他电源 +15V电源,电路由MC34063芯片产生+15V电源,相比+52V电源,+15V电 源主要是采用了MC34063降压变换器形式;+5V电源,主要是采用了稳压块 7808芯片,之后通过+15V电源转化而来;+12V电源当中,主要是通过VOLTREG7812稳压块来实现相关功能,由+15V电源驱动。运行稳压7812模块过 程中,输入电源要比输出电源更大一些,通常为2V以上。 2.2 LED显示系统 LED驱动系统应用DIP-8开关和单片机I/O输出端口连接,个女警单片机实际

锁相环PLL设计调试小结

锁相环设计调试小结 一、系统框图 二、锁相环基础知识及所用芯片资料(摘录) (一)、并行输入 PLL (锁相环)频率合成器MC145152-2 MC145152 是 MOTOROLA 公司生产的大规模集成电路,它是一块采用并行码输入方式设定,由16根并行输入数据编程的双模 CMOS-LSI 锁相环频率合成器,其内部组成框图如图 3-32-3 所示。N 和 A 计数器需要 16 条并联输入线,而 R 计数器则需要三条输入线。该芯片内含参考频率振荡器,可供用户选择的参考频率分频器(12X8 ROM 参考译码器和12BIT ÷R 计数器组成的参考频率fr ),双端输出相位检测器,逻辑控制,10比特可编程序的÷N(N=3~1023) 计数器和 6比特可编程的÷A(A=3~63)计数器和锁定检测部分. 10比特 ÷ N 计数器,6 比特÷ A 计数器,模拟控制逻辑和外接双模前置分频器 (÷P /÷P +1)组成吞食脉冲程序分频器,吞脉冲程序分频器的总分频比为:N T =P*N+A 。 MC145152 的功能: * 借助于 CMOS 技术而取得的低功耗。 * 电源电压范围 3~9V 。 * 锁相检测信号。 * 在片或离片参考振荡器工作。 * 双模并行编程。 * N 范围 =3~1023,A 范围 =0~63。 * 用户可选的 8 个 R 值:8 ,64 , 128 , 256 , 512 , 1024 , 1160 ,2048. * 芯片复杂度——8000 个场效应管或 2000 个等效门。 鉴相器 MC145152 环路滤波器 LPF 压控振荡器 MC1648 分频器 MC12017 频率输出

2015新DK106高性能开关电源管理芯片

DK106(BOM)-5V1A

功能描述 DK106芯片是专用小功率开关电源控制芯片,广泛用于电源适配器、LED电源、电磁炉、空调、DVD等小家电产品。 一、产品特点 ?采用双芯片设计,高压开关管采用双极型晶体管设计,以降低产品成本;控制电路采用大规模MOS数字电路设计,并采用E极驱动方式驱动双极型晶体芯片,以提高高压开关管的安全耐压值。内建自供电电路,不需要外部给芯片提供电源,有效的降低外部元件的数量及成本。 ?芯片内集成了高压恒流启动电路,无需外部加启动电阻。 ?内置过流保护电路,防过载保护电路,输出短路保护电路,温度保护电路及光藕失效保护电路。 ?内置斜坡补偿电路,保证在低电压及大功率输出时的电路稳定。 ?内置PWM振荡电路,并设有抖频功能,保证了良好的EMC特性。 ?内置变频功能,待机时自动降低工作频率,在满足欧洲绿色能源标准(<0.3W)同时,降低了输出电压的纹波。 ?内置高压保护,当输入母线电压高于保护电压时,芯片将自动关闭并进行延时重启。 ?内建斜坡电流驱动电路,降低了芯片的功耗并提高了电路的效率。 ?4KV防静电ESD测试。

二、功率范围 输入电压(85~264V ac ) (85~145V ac ) (180~264V ac ) 最大输出功率 6W 8W 8W 三、封装与引脚定义 引脚符号功能描述引 脚符号功能描述 1Gnd 接地引脚。1HV 2Gnd 接地引脚。2Nc 空脚或接地。3Fb 反馈控制端。3Fb 反馈控制端。4Vcc 供电引脚。 4Vcc 供电引脚。 5678 Collector 输出引脚,连接芯片内高压开关管Col-lector 端,与开关变压器相连。 7,8 Collector 输出引脚,连接芯片内高压开关管Col-lector 端,与开关变压器相连。 5,6GND 引脚接地。 四、内部电路框图

三阶魔方CFOP公式(GAN)

OLL公式及手法Gan 1 (R U'U') (R2' F R F') U2 (R' F R F') 2 (F R U R' U' F') (f R U R' U' f') 3 f(R U R' U')f' U' F(R U R' U')F' 4 f(R U R' U')y x(R’ F)(R U R' U')F' 5 (r' U2) (R U R'U) r 6 (r U'U') (R' U' R U' r') 7 r U R' U R U'U' r' 8 r' U' R U' R' U2 r 9 (R' U' R) y' x' (R U')(R'F) (R U R') 10 (R U R'U)(R'F R F') (RU'U'R') 11 r'(R2 U R' U)(R U'U' R' U) (r R') 12 (r R'2 U' R U')(R' U2 R U' R)r' 13 (r U' r' U')(r U r') (F' U F) 14 R' F R U R' F'R (F U' F') 15 (r' U' r) (R'U'R U) (r' U r) 16 (r U r)' (R U R' U') (r U' r') 17 (R U R' U) (R' F R F'U2) R' F R F' 18 F (R U R' d)(R' U2) (R' F R F') 19 (r' R U)(R U R' U' r) (R'2 F R F') 20 r'(R U) (R U R'U' r2)(R2'U) (R U') r' 21 (R U'U') (R' U' R U R' U') (R U' R') 22 R U'U' (R'2 U') (R2 U') R'2 U' U'R 23 (R' U2) (R F U') (R' U' R U F') 24 (r U R' U') (r' F R F') 25 F'(r U R' U') (r' F R) 26 R U'U' R' U' R U' R' 27 R' U2 R U R' U R 28 (r U R' U') (r' R U) (R U' R') 29 (r U R' U')(R r'2 F R F') (r R') 30 (f R U)(R2 U'R' U R2 U' R' f') 31 (r' F' U F) (L F' L' U' r) 32 (R U)(B' U')(R' U R B R') 33 (R U R' U') (R' F R F') 34 (R'U'R U) y(r U R' U')r' R 35 R U'U'R2' F R F'(R U'U'R') 36 R'U'R U' R'U R U l U'R'U 37 F (R U' R'U'R U) (R' F') 38 (R U R'U) (RU'R'U') (R'F R F') 39 (r U' r' U' r)y(R U R' f') 40 (R' F R U R'U') (F' U R) 41 R U' R' U2 R U y R U' R' U' F' 42 (r' R2)y (R U R' U') (R' U R')r 43 (B' U') (R' U R B) 44 f (R U R' U')f' 45 F (R U R' U') F' 46 (R' U') R' F R F' (U R) 47 B'(R' U' R U)2 B 48 F (R U R' U')2 F' 49 R B'(R2 F)(R2 B) R2 F' R 50 L'B (L2 F')(L2B') L2 F L' 51 f (R U R' U')2 f' 52 R'U' R U' R' d R' U l U 53 (r' U2) (R U R'U') (R U R'U) r 54 (r U'U') (R' U' R U R' U') (R U' r') 55 (R U'U') (R'2 U') R U' R'U2 (F R F') 56 F (R U R'U')(R F')(r U R'U')r' =(r' U' r U')(R' U R U' R' U)(R r' U r) =(r U r')(U R U' R')2(r U' r') 57 (R U R' U' r)(R' U) (R U' r')

DCDC开关电源管理芯片得设计

DC-DC开关电源管理芯片得设计 引言 电源就是一切电子设备得心脏部分,其质量得好坏直接影响电子设备得可靠性。而开关电源更为如此,越来越受到人们得重视。目前得计算机设备与各种高效便携式电子产品发展趋于小型化,其功耗都比较大,要求与之配套得电池供电系统体积更小、重量更轻、效率更高,必须采用高效率得DC/ DC开关稳压电源。 目前电力电子与电路得发展主要方向就是模块化、集成化。具有各种控制功能得专用芯片,近几年发展很迅速集成化、模块化使电源产品体积小、可靠性高,给应用带来极大方便。 从另一方面说在开关电源DC-DC变换器中,由于输入电压或输出端负载可能出现波动,应保持平均直流输出电压应能够控制在所要求得幅值偏差范围内,需要复杂得控制技术,于就是各种 PWM控制结构得研究就成为研究得热点。在这样得前提下,设计开发开关电源DC-DC控制芯片,无论就是从经济,还就是科学研究上都就是就是很有价值得。 1、开关电源控制电路原理分析 DC-DC变换器就就是利用一个或多个开关器件得切换,把某一等级直流输 入电压变换成另—等级直流输出电压。在给定直流输入电压下,通过调节电路开关器件得导通时间来控制平均输出电压控制方法之一就就是采用某一固定频率进行开关切换,并通过调整导通区间长度来控制平均输出电压,这种方法也称为脉宽调制[PWM]法。 PWM从控制方式上可以分为两类,即电压型控制(voltage mode control)与电流型控制(current mode control) 。电压型控制方式得基本原理就就是通过误差放大器输出信号与一固定得锯齿波进行比较,产生控制用得PWM信号。从控制理论得角度来讲,电压型控制方式就是一种单环控制系统。电压控制型变换器就是一个二阶系统,它有两个状态变量:输出滤波电容得电压与输出滤波电感得电流。二阶系统就是一个有条件稳定系统,只有对控制电路进行精心得设计与计算后,在满足一定得条件下,闭环系统方能稳定得工作。图1即为电压型控制得原理框图。 图1 电压型控制得原理框图 电流型控制就是指将误差放大器输出信号与采样到得电感峰值电流进行比较.从而对输出脉冲得占空比进行控制,使输出得电感峰值电流随误差电压变化而变化。电流控制型就是一个一阶系统,而一阶系统就是无条件得稳定系统。就是在传统得PWM电压控制得基础上,增加电流负反馈环节,使其成为一个双环控制系统,让电感电流不在就是一个独立得变量,从而使开关变换器得二阶模型变成了一个一阶系统。信号。从图2中可以瞧出,与单一闭环得电压控制模式相比,电流模式控制就是双闭环控制系统,外环由输出电压反馈电路形成,内环由互感

采用PLL设计时需要注意的问题

采用PLL设计时需注意的问题 为了满足ASIC设计中时间进度上的要求,许多工程师都采用了锁相环(PLL)。PLL具有一些人们所希望的特性,包括时钟倍频能力、时钟占空度校正能力以及时钟分配延时消除能力。这些特性使得设计人员能够运用廉价的低频晶体作为其片外时钟脉冲源,并随后进行片上倍频,以生成任何数值的高频内部时钟信号。它们还令设计人员能够通过将建立-保持时间窗口与芯片的时钟脉冲源的边缘对准的方法来控制这些窗口以及芯片接口处的时钟-输出延时。 虽然在结构和功能上看起来很简单,但锁相环充满了各种隐含的复杂性,这些复杂性有可能给哪怕是最好的设计师带来麻烦。当今ASIC工艺中PLL的设计正变得越来越困难,原因是内核薄氧化物器件的阈值之上所留的电源电压峰值储备较为有限。这些器件往往被要求满足目标工作频率并保持电源电压的灵活性。但是,电源电压峰值储备的减少将会对PLL的噪声特性产生不良影响。 结构和操作 若要真正搞清PLL内部的性能问题,就必须首先了解其结构和工作原理。PLL的高级结构似乎是直观明了的,它由相位检测器、电荷泵、环路滤波器和压控振荡器(VCO)所组成。PLL 电路被启动后将立即进入一种“解锁”状态,因为VCO分割输出频率与基准频率无关。 然而,环路中的负反馈通过汇集周期性基准输入和VCO分割输出的时钟脉冲上升沿之间的相位误差来调整VCO输出频率。综合相位误差使得VCO分割输出频率接近基准频率。当PLL 到达“锁定”状态时,相位检测器所检测到的相位误差接近于零,这是因为VCO分割输出频率和相位与基准频率和相位是一致的。由于相位检测器只与VCO分割输出相比较,因此PLL 输出频率将比基准和反馈输入频率高N倍,从而使得PLL能够完成倍频。 此外,如果时钟分配被加至反馈通路,则PLL将把分配时钟信号对准基准信号,以有效消除时钟分配延时。 PLL内部的功能块可由可变数量的模拟和数字电路组成,甚至在全数字电路的极端情况下也是如此。然而,不管是由数字电路组成还是由模拟电路组成,PLL完成的都是时钟信号相位的生成和校准这样的模拟功能。和模拟功能块一样,它们也面临着象噪声这样的当今ASIC 苛刻的混合信号环境中常见且不可避免的模拟技术难题。如果PLL不能对噪声做出良好的响应,它就会导致输出时钟偏离其理想值的时间变换偏移。 输出时钟相位中的这些时间变换偏移通常被称为抖动(jitter)。抖动会通过引发建立时间扰乱而对内部定时通路产生灾难性的影响,也会通过引发导致数据传输误差的建立-保持时间扰乱而影响片外接口。与此同时,其他性能问题(如不稳定性、不适当的频率范围、锁定问题和静态相位偏移)也会影响PLL设计。输出抖动是最为重要的问题之一,也是PLL设计中最难得以合适解决的课题之一。 由片上和片外信号源生成的电源和基底噪声具有很高的数据依存性,并可具有大量包括低频在内的频率分量。基底噪声往往不会象电源噪声那样拥有大量的低频分量,因为在基底和电源之间没有明显的直流下降。在最差的条件下,PLL会出现电源噪声电平和基底噪声电平分别达到标称电源电压的10%和5%的情况。 基底噪声的实际电平取决于IC生产工艺所采用的基底的性质。为了降低出现闩锁的危险性,许多IC生产工艺采用了在同类重掺杂基底上的轻掺杂外延。这些基底往往会在芯片上进行长距离的基底噪声传输,使得噪声不易在通过保护环和附加的基底分接头时被消除。 电源和基底噪声通过引发VCO输出中的频移(它会导致积累多个周期、直到噪声脉冲下陷为止的相移)而对PLL产生影响,在没有影响的情况下PLL能够以其环路带宽所限定的速率对