接口第6次课_第8章输入输出接口基础

微机原理及接口技术概述

数据总线DB

控制总线CB

1.2.2 微型计算机的软件系统

操作系统 MS-DOS

汇编程序

文本编辑程序

MASM和LINK

调试程序

DEBUG.EXE

1.3 IBM PC系列机系统

16位IBM PC系列机是32位微机的基础 8088CPU

IBM PC机 IBM PC/XT机 IBM PC/AT机

(1)数—用来直接表征量的多少,它们有大小之分,可进行各种数学 运算。 (2)码—用来指代某个事物或事物的状态属性。计算机对码主要是做 管理、编辑、判断、检索、转换、存储及传输等工作。

1.4.1 计算机中的数

在讨论计算机中的数时,需要说明几个基本概念:

(1)进位计数制---即采用进位的计数方法。采用这种计数方法后人们可以用有限的数 码符号来表示无穷大或无穷小的数。在计算机领域,常用的进位计数制有二进制、十进 制、八进制和十六进制(因本课程不使用八进制数据,故以下从略)。例如,二进制中 有两个数码符号,即0和1,执行逢2进1的运算规则;十进制中有10个数码符号0-9,执行 逢10进1的运算规则;十六进制中有16个数码符号0一9及A一F,执行逢16进1的运算规则。 注意,在十六进制中,数码A表示十进制的10,但决不能记作10,因为1和0是两个十六 进制符号。 (2)基数---某种进位计数制中所包含的数码个数就是该数制的基数(Base),如二进制 的基数为2,N进制的基数为N。基数体现了该数制中进位和借位的原则:当我们在某个 数位上计够一个基数时需要向前进1;反之,从前一位借1可在后一位上当一个完整的基 数来使用。 (3)权—也称权重(Weight),表示进位计数制中各数位的单位值(可形象地理解为每个 数位的单位“重量”)。权可以用基数幂的形式来表示,例如在十进制数1111.11中, 各个“1”具有不同的权重,从左到右分别为:103、102 、101、100、10-1和10-2。还可进 一步推广到N进制数(1111.11)N,从左到右各数位上的权重分别是:N3、N2、 N1、N0, N-1和N-2。

第8章 51单片机输入输出接口-单片机原理与应用及C51程序设计(第4版)-谢维成-清华大学出版社

第8章 51单片机输入输出接口及应用

该最小系统的特点如下: (1) 由于P0、P2在扩展程序存储器时作为地址线和数 据线,不能作为I/O线,因此,只有P1、P3作为用户I/O接 口使用。 (2) 片内数据存储器同样有128B,地址空间为00H~ 7FH,没有片外数据存储器。 (3) 内部无程序存储器,片外扩展了程序存储器,其地 址空间随芯片容量不同而不一样。图8.2中使用的是2764 芯片,容量为8KB,地址空间为0000H~1FFFH。由于片 内没有程序存储器,只能使用片外程序存储器,EA 只能接 低电平。 (4) 同样可以使用两个定时/计数器T0和T1,一个全双 工的串行通信接口,5个中断源。

2.另一端送相应的编码(字段码)

第8章 51单片机输入输出接口及应用

8段发光管控制端与字节的关系。

76543210 dp g f e d c b a

00 11 1111

3FH

0 00 0 0110

06H

0101 1011

5BH

第8章 51单片机输入输出接口及应用

显示字符 共阴极字 共阳极字 显示字符 共阴极字 共阳极字

最小配置系统。对于单片机内部资源已能满足 系统需要的,可直接采用最小系统。MCS-51单 片机根据片内有无程序存储器最小系统分两种 情况。

8.1.1 8051/8751的最小系统

第8章 51单片机输入输出接口及应用

XTAL1

P0

8

8751

8051 P1

8

XTAL2

P2

8

RESET

EA GNDP3

8

+5V

+5V V

第8章 51单片机输入输出接口及应用

该最小系统的特点如下: (1) 由于片外没有扩展存储器和外设,P0、P1、P2、P3都 可以作为用户I/O接口使用。 (2) 片内数据存储器有128B,地址空间为00H~7FH,没有 片外数据存储器。 (3) 内部有4KB的程序存储器,地址空间为0000H~0FFFH

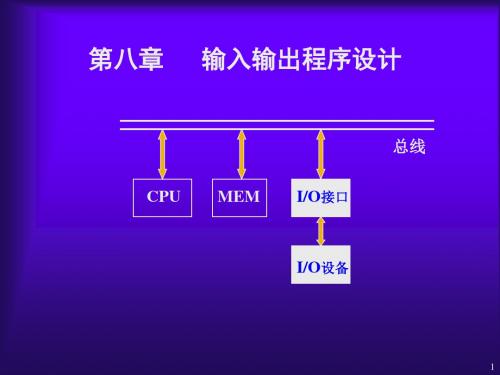

IBM—PC(80x86)汇编语言与接口技术-第8章 输入输出程序设计

8259A

76 5 4

中断屏蔽寄存器21H

打 印 机

3210

IN AL, 21H AND AL,0FDH

键定 时

盘器

OUT 21H,AL

76 5 4

中断命令寄存器20H

EOI

3 2 1 0 MOV AL, 20H OUT 20H, AL

11

中断向量表

00000 类型0的(IP) 类型0的(CS)

00004 类型1的(IP) 类型1的(CS)

speaker_on endp

speaker_off proc push ax in al, 61h and al, 0fch out 61h, al pop ax ret

speaker_off endp

end

8

3. 中断传送方式

中断源:引起中断的事件

外中断(硬中断):

外设的 I/O 请求 —— 可屏蔽中断 电源掉电 / 奇偶错 —— 非屏蔽中断

15

例:用 DOS 功能调用存取中断向量

MOV AL, N

MOV AH, 35H

INT 21H

PUSH BX

; 保存原中断向量

PUSH DS

MOV AX, SEG INTHAND

MOV DS, AX

MOV DX, OFFSET INTHAND

MOV AL, N

MOV AH, 25H

08 系统定时器 09 键盘 0A 彩色/图形接口 0B 保留 0C 串行通讯口 0D 保留 0E 软盘 0F 打印机

10

中断的条件:

设置CPU中断允许位:

FLAGS 中的 IF 位 = 1 允许中断 ( STI ) = 0 禁止中断 ( CLI )

HDL 第6次课

测试与仿真

测试仿真 施加 激励 待验证 设计模块 响应 输出 观察输出 对比结果

观察对比波形(波形仿真) 测试激励 待测设计 生成文本(命令式仿真)

对已设计模块的测试与仿真通常可分为以下三个步骤: 对被测设计的顶层接口进行例化。 给被测设计的输入接口添加激励。 判断被测设计的输出响应是否满足设计要求

//二输入与门 module and_2(A,B,F); input A,B; output F; and U1(F,A,B); endmodule

//半加器 开关级描述(调用开关级元件) module halfadder(A,B,F,CO); input A,B; UDP级描述(用户自定义元件) output F,CO; xor U1(F,A,B); and U2(CO,A,B); 元件名 (<时延>)<实例名>(<端口列表>) endmodule 类型 基本门 多输入门 元件

end

添加复位信号

//复位信号产生 //复位低有效,已定义“’timescale 1ns/1ps” initial begin rst_n=0; #100; //100ns延时

rst_n=1; //撤销复位

end

课后作业:

1、利用不同描述方式设计加法器、乘法器

2、练习编写加法器、乘法器测试模块

行为描述方式侧重反映电路输入、输出信号间的关系, 一般采用 initial 语句或 always 语句描述逻辑功能。

//二输入与门 module and_2(A,B,F); input A,B; output F; reg F; initial F=0; always@(A or B) assign=A&B; endmodule //半加器 module halfadder(A,B,F,CO); input A,B; output F,CO; reg F,CO; always@(A or B) begin case({A,B}) 2’b00:begin F=0;CO=0;end 2’b01:begin F=1;CO=0;end 2’b10:begin F=1;CO=0;end 2’b11:begin F=1;CO=1;end end endmodule

单片机实用教程_8 89C51单片机并行输入输出

P3 口的第二功能

口线 P3.0 P3.1 信号 RXD TXD 功 能 串行口数据输入(接收数据) 串行口数据输出(发3.5

P3.6 P3.7

INT0 INT1 T0 T1

WR RD

外部中断0输入 外部中断1输入 定时器0的外部输入(计数输入) 定时器1的外部输入(计数输入)

外部数据存储器写选通控制输出 外部数据存储器读选通输出控制

8.2 并行输入/输出端口P0、P1、P1和P3 8.2.1 P0端口 ⑴ P0口的结构: P0口有8位, 每一位由一个输出锁存器、两个三态 输入缓冲器和输出驱动电路及控制电路组成。

⑵ P0口作通用的I/O口使用

P0口是漏极开路的8位准双向I/O口. P0口为特殊功能寄存器, 既可以用直接寻址方式对P0口进行字节操作, 也可以按按位寻址方式,进行位操作。

P2端口及其各位的地址

位地址/位定义 A5H P2.5 A4H P2.4 A3H P2.3 A2H P2.2 A1H P2.1 LSB A0H P2.0 字节地址 A0H

P2口作输出时,直接用传送指令进行操作。 例如: MOV P2 ,A P2口作输入时, 要先写“1”, 然后读入(准双向口)。 例如: MOV P2 ,#0FFH MOV A ,P2

表8.1 P0端口及其各位的地址

SFR MSB 位地址/位定义 LSB 字节地址

P0

87H

P0.7

86H

P0.6

85H

P0.5

84H

P0.4

83H

P0.3

82H

P0.2

81H

P0.1

80H

P0.0

80H

P0口作输出时,直接用传送指令进行操作。 例如: MOV P0 ,A P0口作输入时,要先写“1”,然后读入(准双向口)。 例如: MOV P0 ,#0FFH MOV A ,P0

第8章可编程输入输出接口2014(新简)

当A1A0=11时 选择控制端口

20

表8.1 8255A的读写操作控制

21

8.1.2 8255A的控制字及其工作方式

8255A 共有两个控制字:即工作方 式控制字和对C口臵位/复位控制字。 1. 控制字 (1)工作方式控制字: 控制字和各位的含义如图所示。

22

D7

D6 D 5

D4 D3

D2 D1 D0

下图示出 8255A 方式 1 选通输入时的内部 结构图。

35

•STB:选通信号。外设准备好数据发 送STB#,低电平有效。

•IBF:输入缓冲器满信号,STB#下降 沿8255向外设输出IBF信号,表示输入 缓冲器满,高电平有效。

36

INTR:中断请求信号,高电平有效 。STB#上升沿使INTR从无效到有效 ,请求CPU读数据。CPU接到INTR, 读数据发送RD#,RD#下降沿变INTR 有效为无效,表示已经得到响应, RD#上升沿使IBF满变为不满,表示 数据已经读走。 INTE:中断允许信号,它是通过端 口PC4(端口A)或PC2(端口B)的位来编 程的内部位。

ACK: 外设应答信号。该信号的下 降沿使OBF臵高,表示输出缓冲器 空,低电平有效.当外设读取数据以 后,由外设输入给8255,表示数据

42

INTR:中断请求信号。写信 号的下降沿使INTR引脚无效, 表示CPU正在响应中断,高电 平有效。

INTE : 中断允许信号。在中

断允许情况下, ACK 的

出数据均受到锁存。

端口 B 和 C: 都包含一个 8 位数据输入缓

冲器和一个 8位的数据输出锁存器和缓冲器,

输出数据能锁存,输入数据不锁存。

7

端口 C: 可分成两个 4 位端口,分别定义 为输入或输出端口,还可定义为控制、状 态端口,配合端口A和端口B工作。 在实际应用中C口 的8位可分为两个4位

java08(第8章输入输出流)

在java.io包中定义了很多这二个基本类具体实现 包中定义了很多这二个基本类具体实现 输入输出功能的子类, 输入输出功能的子类,表8.1为部分常用字节输入 为部分常用字节输入 流类和字节输出流子类的功能。 流类和字节输出流子类的功能。

表8.1

类 名 FileInputStream 和 FileOutputStream ByteArrayInputStream和 ByteArrayOutputStream ObjectInputStream 和 ObjectOutputStream FilterInputStream 和 FilterOutputStream DataInputStream 和 DataOutputStream BufferedInputStream 和 BufferedOutputStream

【例8-1 】

1. /* 读取文件 */ 2. import java.io.FileInputStream; 3. import javax.swing.JOptionPane; 4. class Example8_1 5. { public static void main( String args[ ]) 6. { byte buffer[ ] = new byte[2056]; 7. String str; 8. try{ 9. File file=new File("d:/jtest/test.dat"); 10. FileInputStream fileInput = new FileInputStream(file); 11. int bytes = fileInput.read( buffer, 0, 2056 ); //读到的字节数 读到的字节数 12. str = new String( buffer, 0, bytes ); 13. } 14. catch(Exception e) 15. { 16. str= e.toString(); 17. } 18. JOptionPane.showMessageDialog(null,str); 19. System.exit(0); //退出程序 退出程序 20. } 21. }

第8章输入输出设备

教学内容安排•第一章绪论•第二章数码系统•第三章运算方法和运算器•第四章存储系统•第五章指令系统•第六章中央处理器•第七章输入输出设备•第八章输入输出系统第八章输入输出系统•8.1输入输出设备的编址方式•8.2总线结构•8.3输入输出控制方式•教学重点和难点•输入输出控制方式第八章输入输出系统8.1 输入输出设备的编址方式•计算机主机要与输入输出设备交换信息,仿照存储器的编址方式,可给各台外部设备分配一个或多个端口地址•输入输出控制方式–统一编址方式–独立编址方式第八章输入输出系统8.1 输入输出设备的编址方式•I/O端口与存储器独立编址•是指系统中的输入输出设备与主存储器构成两个独立的空间–直接端口寻址:端口地址用8位地址码表示,并且是指令码的一部分。

•IN AL,21H–间接寻址方式:端口地址由16位地址码表示,并存放在DX中,即DX寄存器的内容作为端口地址。

•OUT DX,AL第八章输入输出系统8.1 输入输出设备的编址方式•与内存统一编址–优点:不需专门的输入输出指令,缩小了指令规模–缺点:挤占了可供用户使用的内存空间第八章输入输出系统•8.1输入输出设备的编址方式•8.2总线结构•8.3输入输出控制方式•教学重点和难点•总线分类第八章输入输出系统8.2 总结结构•总线控制方式–串行链式查询方式–计数定时查询方式–独立请求方式第八章输入输出系统8.2 总结结构•总线通信方式–同步方式–异步方式第八章输入输出系统8.2 总结结构•总线上信息的传送方式–串行传送方式–并行传送方式第八章输入输出系统•8.1输入输出设备的编址方式•8.2总线结构•8.3输入输出控制方式•教学重点和难点•程序中断方式第八章输入输出系统8.2 输入输出控制方式•输入输出数据传送控制方式•主机速度与外围设备速度匹配问题•如何提高整机系统性能的问题第八章输入输出系统8.2 输入输出控制方式•程序查询方式•信息在主机和外设之间的传输完全靠计算机程序控制,是在CPU控制下进行的。

第8章 串并行通信

微型计算机各种接口框图

微机接口电路图

2.什么是I/O接口(电路)?

I/O接口是位于系统与外设间、用来协助 CPU实现CPU与外设之间的数据传送和 控制任务的逻辑电路 PC机系统板的可编程接口芯片、I/O总 线槽的电路板(适配器)都是接口电路

CPU

接口 电路

I/O 设备

3.为什么需要I/O接口(电路)?

数据端口

• 用于中转数据信息。一种情况是CPU通过数据总线,将待传送 给外设的数据先传送到数据端口,然后由I/O设备通过与I/O 接口电路相连接的数据线取得该数据 • 另一种情况是I/O设备首先将输入数据锁存于数据端口,然后, CPU通过数据端口将该数据读入CPU中。数据端口一般既有输 出寄存器(或称输出锁存器),又有输入寄存器(或称输入 锁存器)

一、统一编址

从内存空间划出一部分地址空间留给I/O设备编址,CPU把

I/O端口所指的寄存器当作存储单元进行访问,直接用访问内存 的指令访问I/O寄存器,这种I/O端口的编址方式被称之为统一

编址,或称为存储器映像的I/O编址方式。

统一编址优缺点 优点:不需要设立专门的I/O指令,用访问内存的指令就可 以访问外设,指令类型多,功能齐全,还可以对端口进行算术 运算,逻辑运算以及移位操作等。I/O端口空间不受限制 缺点:是I/O端口占用了内存空间,减少了内存容量

住址的总 线 地址总线

READY

M/IO

图8.2 查询式输入接口电路

WR

条件传送方式

数 据 锁 存 器

选通信号

数据总线

WR 地址 总线

输 出译码

Q

R

D +5V

RD M/IO

状 态 寄 存 器 图8.3 查询式输出的接口电路

第8章__8155芯片

➢ 256B的静态RAM; ➢ 两个可编程的8位并行I/O口PA和PB; ➢ 一个可编程的6位并行I/O口PC; ➢ 一个可编程14位减计数器TC; ➢ 8位地址锁存器。

8155的引脚封装图

12 13 14 15 16 17 18 19

AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7

问题的提出

❖ MCS-51系列单片机内部有4个双向的8位并行I/O端口: ❖ P0、P1、P2和P3口。 ❖ 在实际的应用系统中,P0、P2、P3口往往用来代替系统

总线使用,数据口仅剩下P1口了。另外,单片机内部I/O 口的功能也过于简单,只有数据锁存和缓冲功能,而没有 状态寄存和命令寄存功能,难以满足复杂的I/O操作的要 求。 ❖ 鉴于单片机的I/O资源比较有限,在实际应用中不得不使 用扩展的方法,以增加I/O口的数量,强化I/O的功能。

IO/M PC3

WR PC4

RD PC5

PB

8

AINTR ABF ASTB BINTR BBF BSTB

8

端口数据线

至CPU 至外设 自外设 至CPU 至外设 自外设 端口数据线

带联络信号的应答式输出时序

INTR CPU WR

OUTPUT BF

MOVX @DPTR,A MOVX @DPTR,A 端口数据

PC0 PC1 PC2 PC3 PC4 PC5

37 38 39 1 2 5

芯片引脚功能:

三态地址/数据 复用线

地址锁存线

RAM及IO选择

CPU

复位端

读选通信号线 写选通信号线

片选线

AD0

PA0

AD1

PA1

AD2

PA2

AD3 AD4 AADD56 AD7

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

11

... 执行指令 ... ...

1000:150H

MOV AX, 0 保存现场.断点 保存现场 断点 DX ADD 断点1000:150H AX, 恢复现场.断点 断点1000:150H 恢复现场 [ DI ], AX 断点 MOV执行指令

... ... ... ... ...

中断 ... 执行中断指令 ... ... ... ... ... ... ... ... ...

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

18

输入输出接口基础

The Basis of Input and Output Interface

Computer Application Dept. BME Faculty. FMMU.

内容(Outline) 内容(Outline)

• • • • • 输入输出的基础知识 输入输出的方式 PC机的系统级总线和资源 PC机的系统级总线和资源 80x86微机的中断系统 80x86微机的中断系统 可编程中断控制器8259A 可编程中断控制器8259A

• • • • • 输入输出的基础知识 输入输出的方式 PC机的系统级总线和资源 PC机的系统级总线和资源 80x86微机的中断系统 80x86微机的中断系统 可编程中断控制器8259A 可编程中断控制器8259A

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

7

中断源之间的关系 (Relationships of Interrupt) Interrupt)

不可屏蔽中断请求 NMI

IR0 IR1

INTR

08 系统定时器 09 键盘 彩色/ 0A 彩色/图形接口 保留(通信) 0B 保留(通信) 0C 串行通信接口 0D 保留(ALT打印机) 保留(ALT打印机) (ALT打印机 0E 软盘 0F 保留(打印机) 保留(打印机)

PUSH AX

... ... ... ... ...

IRET

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

12

实模式下中断的响应过程 (Interrupt response in real mode )

• 可屏蔽中断 IF – 执行完当前指令 • NMI IF – 从总线上获取中断号 – NMI引脚出现正跳变 • NMI引脚出现正跳变 IF 软中断 – 压栈FLAGS, CS, IP 压栈FLAGS,

• 可接受15级中断,12个在AT总线上 可接受15级中断,12个在AT总线上 • 键盘占用1级,定时器占用0级中断 键盘占用1级,定时器占用0

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

5

内容(Outline) 内容(Outline)

• 中断服务程序(Interrupt Service Routine)地址 Service Routine)

– 前两个字节段内偏移(IP) 前两个字节段内偏移(IP) – 段地址(CS) 段地址(CS)

2011-11-16 ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU 9

2011-11-16 ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU 3

XT – ISA(AT) - PCI

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

4

PC系统的接口资源 PC系统的接口资源

• 系统总线 • 基本配置

– 鼠标,键盘扬声器接口逻辑 – 主板上的8259A中断控制器 主板上的8259A中断控制器

– – – – – – –

主板上的DMA控制逻辑 主板上的DMA控制逻辑 CPU的外围芯片8254定时器 CPU的外围芯片8254定时器 显示器接口 并口 RS232串口 RS232串口 磁盘驱动器接口 .......

2011-11-16 ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU 15

中断响应流程图 (Flow chart of interrupt response)

中断的特点 (Characteristics of Interrupt) Interrupt)

80486中断类型号

问题: 问题: 计算中断号为0CH的中断 计算中断号 服务程序地址。 解答: 解答: 中断号=0CH 中断号 中断向量=0000:0030H 中断向量 中断服务程序入口地址 =0F000H:0EF6FH。

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

8

中断号n 中断号

×4

中断向量表

中断程序入口地址

• 中断号(Interrupt Number)区分中断 Number)

– 范围:0~255 (INT 21H) 范围:0~255 21H)

• 中断向量表( Interrupt Vector Table)定位 Vector able)

– 位于存储器最低的1024个单元中 位于存储器最低的1024个单元中 – 每4个字节为一个中断向量( Interrupt Vector) 个字节为一个中断向量 Vector) – 入口地址 = 中断号 * 4

• 软中断

– 类似函数调用 – 不受IF影响 不受IF影响 – 立即响应

13

• 异常中断

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

保护模式下中断和异常处理

• NMI和INTR引脚,或者内部INT n指令 NMI和INTR引脚,或者内部INT n指令 • IDTR , IDT

6

80x86的中断系统 80x86的中断系统 (Interrupt system of 80x86) 80x86)

• 按中断源不同来划分

–外部中断(硬件中断) 外部中断(硬件中断)

• 可屏蔽(INTR,INTA) 可屏蔽(INTR,INTA) • 不可屏蔽(NMI) 不可屏蔽(NMI)

–内部中断

• 异常中断 • 软件中断(INT n) 软件中断(

10

现场保护(Store 现场保护(Store Interrupt Status) Status)

• 断点地址(Interrupt address) 断点地址(Interrupt

– 现行程序被中断时的下一条指令的地址,又 称断点

• 中断现场(Interrupt Status) 中断现场(Interrupt Status)

– – – –

• 可屏蔽 • NMI

– 受IF影响 IF影响 CLI STI – 必须响应 – 响应NMI期间, 响应NMI期间, 新NMI会被保存 NMI会被保存 – IRET后才响应 IRET后才响应

– 置中断号为2 置中断号为2 – 清除IF,异常中断 IP 清除IF,INT n • TF IF – 压栈FLAGS, CS, 压栈FLAGS, n – 置中断号为 置中断号为n 计算中断向量TF – 异常 – 清除IF,FLAGS, CS, IP 清除IF, – 压栈 压栈FLAGS, 中断服务 – 自动形成中断号 – 计算中断向量 清除IF, IRET – 清除IF,TF – 压栈 压栈FLAGS, – 中断服务 FLAGS, CS, IP – 计算中断向量 清除IF, – IRET– 清除IF,TF – 中断服务 – 计算中断向量 – IRET – 中断服务 – IRET

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

2

IBM PC/XT 总线

• • • • • 数据线 D0~D7 地址线 A0~A19 IOW IOR IRQ2~IRQ7

8086/PC/XT/8Bits 80286/AT(ISA)/16Bits EISA/32Bits PCI/32Bits

CPU

中断逻辑

INT 8259A 可编程 中 断 控制器

( PIC )

IR2 IR3 IR4 IR5 IR6 IR7

INTn

指令

单字节 中断指 令

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

• 发生的随机性 • 处理的确定性

– 发生的时间无法预知,是随机的。 – 事件的性质及处理方法则是已知的, 确定的。 即中断服务程序是事先编写好的, 即中断服务程序是事先编写好的,只是何时执 行未知。

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU

– 是指CPU转去执行中断服务程序前的运行状 是指CPU转去执行中断服务程序前的运行状 态,包括CPU内部各寄存器、断点地址等。 态,包括CPU内部各寄存器、断点地址等。

2011-11-16

ZhangGuoPeng Computer Application Dept. BME Faculty. FMMU