FPGA创新实验平台的设计与应用

用fpga简易数字钟电路设计实验报告 概述及解释说明

用fpga简易数字钟电路设计实验报告概述及解释说明1. 引言1.1 概述本实验报告旨在介绍使用FPGA(可编程门阵列)设计的简易数字钟电路。

数字钟是一种可以显示时间的时钟装置,广泛应用于日常生活和工业领域。

本文将详细讲解数字钟的设计原理、硬件要求、设计步骤以及实验的实现过程。

1.2 文章结构本文共分为五个部分,即引言、FPGA简易数字钟电路设计、实验实现过程、实验结果分析和结论与总结。

下面将对每个部分进行具体说明。

1.3 目的该实验旨在通过学习和操作FPGA,深入理解数字电路设计的基本原理和方法,并通过设计一个简易的数字钟电路来巩固所学知识。

通过本实验,我们还将探索数字钟电路的性能评估和可能的改进方向,并对未来发展方向进行展望。

同时,通过参与这个项目,我们也将获得一定的实践经验和技能提升。

2. FPGA简易数字钟电路设计:2.1 设计原理:在本次实验中,我们使用FPGA(现场可编程逻辑门阵列)来设计一个简易的数字钟电路。

FPGA是一种集成电路芯片,可依据用户需要重新配置其内部互连,从而实现不同的逻辑功能。

我们将利用FPGA的可编程性和强大的计算能力来实现数字钟的功能。

该数字钟电路主要由时钟模块、倒计时模块和显示模块组成。

时钟模块负责产生稳定而精确的脉冲信号作为系统的时基;倒计时模块通过对输入时间进行倒计时操作,并发出相应信号提示时间变化;显示模块用于将倒计时结果以数码管显示出来。

2.2 硬件要求:为了完成该设计,我们需要准备以下硬件设备:- FPGA开发板:提供了外部接口和资源,用于连接其他硬件设备并加载程序。

- 数码管:用于显示时间信息。

- 时钟源:提供稳定而精确的脉冲信号作为系统的时基。

2.3 设计步骤:以下是设计步骤的详细说明:1. 确定所需功能:首先明确数字钟需要具备哪些功能,例如12小时制还是24小时制、倒计时功能等。

2. 确定FPGA型号:根据设计需求和资源限制,选择适合的FPGA型号。

基于FPGA的EDA创新实验探讨

成 。具体 步 骤是 : 根 据 实 验 内容 编 写 好 程 序 并进 行 先

仿 真 , 后 参照 实验 指 导 书 选 择 一 个 合适 的 实验 箱 上 然 的电路 连接 模 式 , 并锁定 管 脚 。最 后下 载程 序 , 行验 进

E A技 术 已 日趋成 熟 逐 渐 成 为现 代 电 子技 术 的 核 心 。 D

cmp sn n h is u cin o P 3 T 1 4 3 i e ̄1 n l nrd c ste p n il o o nod l e a d tl o on d t .a d as it u e h r cpe fd w la —i el o K o o i n n s

维普资讯

第2卷第6 5 期

20 0 6年 6月

实 验

室 研

究 与 探

索

VD.5 No 6 12 .

R S R H ND EX L AT 0 I A RA O Y E EA C A P . 0R 1 N N L BO T R

jn. O6 u 20

Ke r s raie e p r n ;m n mu F G y tm;d w la - n y wo d :ce t x e me t i i m P A s se v i o nod l e i

1 引 言

随着 微 电子技术 、 计算 机技术 的不 断发展 和完 善 ,

hwt cn i t l tcc c i on i epr e t tdnscndel k o bu tecm oi ftemnm m o oj n h e c i i u .D igt s xe m n,s et a epy nw aot h o ps go iiu o o e e r r t h i u n h

FPGA 实验报告

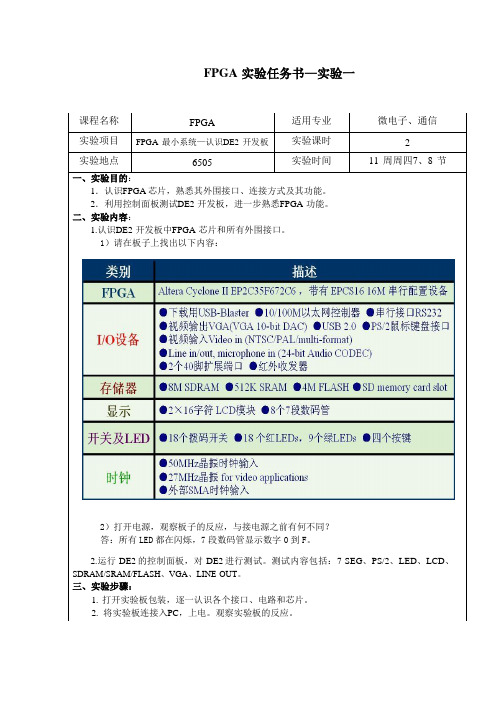

FPGA 实验任务书—实验一课程名称FPGA 适用专业微电子、通信实验项目FPGA 最小系统—认识D E2 开发板实验课时 2实验地点6505 实验时间11 周周四7、8 节一、实验目的:1.认识F PGA 芯片,熟悉其外围接口、连接方式及其功能。

2.利用控制面板测试D E2 开发板,进一步熟悉F PGA 功能。

二、实验内容:1.认识D E2 开发板中F PGA 芯片和所有外围接口。

1)请在板子上找出以下内容:2)打开电源,观察板子的反应,与接电源之前有何不同?答:所有LED都在闪烁,7段数码管显示数字0到F。

2.运行DE2的控制面板,对DE2进行测试。

测试内容包括:7-SEG、PS/2、LED、LCD、SDRAM/SRAM/FLASH、VGA、LINE OUT。

三、实验步骤:1. 打开实验板包装,逐一认识各个接口、电路和芯片。

2. 将实验板连接入P C,上电。

观察实验板的反应。

3.打开Q uartus II,运行第一个程序。

打开控制面板,逐一对主要外围接口进行测试,并记录。

4.运行 DE2_control_panel 目录下的 DE2_Control_Panel.exe,Open->Open_USB_port,下面即可对开发板进行测试了;图 2- 4 DE2 Control Panel5.PS2 和 7-SEG 的测试。

在开发板的插上键盘,输入字符即可显示在上图文本框中;设置HEX0 到 HEX7 的数字,点击 Set,开发板上相应位置的数码管显示相应数字。

6.LED 和 LCD 的测试。

如同上一步。

7.VGA 测试。

将一台显示器数据线连接到开发板的 VGA 口上。

选择 SRAM,将 File Length单选框选中。

点击下面的 Write a File to SRAM,打开DE2_demonstration\pictures\picture.dat;100%完成。

如下图示选 VGA 项。

文华学院FPGA课课程设计

文华学院FPGA课课程设计一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理、设计和应用方法。

通过本课程的学习,学生将能够:1.理解FPGA的基本概念、结构和特点。

2.掌握FPGA的设计流程,包括硬件描述语言的编写、逻辑综合、布局布线和编程下载等。

3.熟悉FPGA的应用领域,如数字信号处理、嵌入式系统、网络通信等。

4.培养学生动手实践能力和团队协作精神。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA的基本原理:介绍FPGA的起源、发展历程、工作原理和主要性能指标。

2.FPGA的结构与特点:讲解FPGA的内部结构、编程方式及其与ASIC、ASIP的区别。

3.硬件描述语言(HDL):学习Verilog和VHDL两种常用硬件描述语言的基本语法和编程技巧。

4.FPGA设计流程:熟悉FPGA的设计流程,包括需求分析、硬件描述语言编写、逻辑综合、布局布线和编程下载等。

5.FPGA应用案例:分析数字信号处理、嵌入式系统、网络通信等领域的FPGA应用实例。

6.实践环节:进行FPGA实验,锻炼学生的动手实践能力和实际问题解决能力。

三、教学方法为了达到本课程的教学目标,将采用以下几种教学方法:1.讲授法:讲解FPGA的基本原理、结构和设计方法。

2.案例分析法:分析具体的FPGA应用案例,让学生了解FPGA在实际工程中的应用。

3.实验法:安排FPGA实验,让学生动手实践,巩固所学知识。

4.讨论法:学生进行小组讨论,培养团队协作精神和沟通能力。

四、教学资源为了支持本课程的教学,将准备以下教学资源:1.教材:选用权威、实用的教材,如《FPGA原理与应用》。

2.参考书:提供相关的参考书籍,以便学生深入研究。

3.多媒体资料:制作PPT、视频等多媒体教学资料,丰富教学手段。

4.实验设备:准备FPGA开发板、编程器等实验设备,确保学生能够动手实践。

5.在线资源:推荐一些在线教程、论坛和学术资源,方便学生自主学习。

fpga课程设计课题

fpga课程设计课题一、教学目标本课程旨在通过学习FPGA的基本概念、原理和应用,使学生掌握FPGA技术的基本知识和技能,能够运用FPGA设计简单的数字系统,培养学生的创新能力和实践能力。

具体目标如下:知识目标:使学生了解FPGA的基本概念、工作原理和应用领域;掌握FPGA设计的基本流程和方法;掌握VHDL或Verilog硬件描述语言的基本用法。

技能目标:培养学生能够使用FPGA开发工具进行数字系统的设计、仿真和验证;培养学生能够独立完成FPGA硬件电路的搭建和调试。

情感态度价值观目标:培养学生对新技术的敏感性和好奇心,培养学生的创新意识和团队合作精神。

二、教学内容本课程的教学内容主要包括FPGA的基本概念、FPGA的设计流程、VHDL和Verilog硬件描述语言、FPGA的应用实例等。

具体安排如下:第1-2课时:FPGA的基本概念和原理。

介绍FPGA的定义、结构、工作原理和应用领域。

第3-4课时:FPGA的设计流程。

介绍FPGA设计的基本流程,包括需求分析、逻辑设计、硬件描述语言编写、仿真验证、综合布局和布线、下载配置等。

第5-6课时:VHDL和Verilog硬件描述语言。

介绍VHDL和Verilog的基本语法、数据类型、逻辑电路描述、模块化和层次化设计方法等。

第7-8课时:FPGA的应用实例。

介绍FPGA在数字系统设计中的应用实例,如数字信号处理器、数字逻辑电路、数字通信系统等。

三、教学方法本课程采用讲授法、案例分析法、实验法等多种教学方法,以激发学生的学习兴趣和主动性。

讲授法:通过讲解FPGA的基本概念、原理和应用,使学生掌握FPGA技术的基本知识和技能。

案例分析法:通过分析具体的FPGA应用实例,使学生了解FPGA技术在实际工程中的应用和价值。

实验法:通过动手实践,使学生掌握FPGA设计的基本流程和方法,培养学生的创新能力和实践能力。

四、教学资源本课程的教学资源包括教材、实验设备、多媒体资料等。

基于FPGA的集成式测试系统的设计与实现

based on FPGA is designed,the detailed design of backplane bus is introduced and the key design of

data synchronization,arbitration mechanism and so on are discussed. The design of USB2.0 bus based on

CY7C68013A chip and the transmission mechanism of the function sub card are also introduced. The

backplane bus has a 50 MB/s instantaneous transmission rate and supports the simultaneous operation of

收稿日期:2020-04-13

模块化插卡式结构设计具有以下优点:

1)功能扩展卡的引脚设计基本一致,增强了设

计的兼容性,也利于系统后续设计的可扩展性和可

稿件编号:202004103

作者简介:钱宏文(1975—),男,江苏无锡人,研究员级高级工程师。研究方向:集成电路应用和微系统。

- 75 -

《电子设计工程》2021 年第 5 期

总 线 后 状 态 机 跳 转 回 初 始 状 态 时 ,6 个 BR 信 号全

高,对应 6 个 BG 信号也全高,等待开始新的一轮 总 线

裁决。

同时传输。功能卡一次获取的数据量为 500 字节,设

计数据缓存 FIFO 位宽为 16 位,为保证数据在传输中

不至丢失,各功能卡的数据缓存 FIFO 深度至少应为

FPGA实验报告实验

西南科技大学实验报告课程名称:基于FPGA的现代数字系统设计实验名称:基于HDL十进制计数、显示系统设计姓名:学号:班级:通信1301指导教师:刘桂华西南科技大学信息工程学院制基于HDL十进制计数、显示系统设计一、实验目的1、掌握基于语言的ISE 设计全流程;2、熟悉、应用VerilogHDL描述数字电路;3、掌握基于Verilog的组合和时序逻辑电路的设计方法;4、掌握chipscope 片内逻辑分析仪的使用与调试方法。

二、实验原理1、实验内容:设计具有异步复位、同步使能的十进制计数器,其计数结果可以通过七段数码管、发光二极管等进行显示。

2、模块端口信号说明:输入信号:Clk_50m ---系统采样时钟clk -------待计数的时钟clr ---------异步清零信号,当clr=0,输出复位为0,当clr=1,正常计数ena---------使能控制信号,当ena=1,电路正常累加计数,否则电路不工作输出信号:q[6:0]---------驱动数码管,显示计数值的个位cout -----------1bit 数据,显示计数值向十位的进位COM-----------共阳级数码管,公共端(接地,参考开发板原理图3、以自顶向下的设计思路进行模块划分:整个系统主要设计的模块是:十进制计数模块和数码管驱动模块,由于实验板的按键为实现硬件防抖,则需要将按键输入的时钟clk,先通过消抖模块消抖后,再输出至后续使用。

1)十进制计数器模块设计输入: CLK -------待计数的时钟CLR ---------异步清零信号,当CLR =0,输出复位为0,当CLR =1,正常计数。

EN---------使能控制信号,当EN=1,电路正常累加计数,否则电路不工作输出:SUM[3:0]---------- 计数值的个位。

即,在CLK 上升沿检测到SUM=9 时,SUM 将被置0,开始新一轮的计数。

tc ------------计数值的十位进位,即:只有在时钟CLK 上升沿检测到SUM=9 时,TC将被置1,其余情况下TC=0;在设计中可以使用always,if-else-if语句实现,设计中注意不要在两个以上的always 模块中对同一个变量进行赋值,否则会产生多重赋值源(multi-source)的问题。

fpga课程设计大纲

fpga课程设计大纲一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理、设计和应用。

通过本课程的学习,学生将能够:1.理解FPGA的基本概念、结构和特点。

2.掌握FPGA的设计流程和开发工具。

3.学会使用FPGA进行数字电路设计和验证。

4.掌握FPGA在实际应用中的调试和优化方法。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA的基本概念、结构和特点:包括FPGA的定义、发展历程、主要厂商和产品介绍,以及FPGA的优势和局限性。

2.FPGA的设计流程:包括FPGA的设计原理、开发工具和使用方法,以及常见的FPGA设计和验证技巧。

3.数字电路设计:包括数字电路的基本概念、组成原理和设计方法,以及常见的数字电路模块和算法实现。

4.FPGA在实际应用中的调试和优化:包括FPGA的编程和配置方法、调试技巧和性能优化策略。

三、教学方法为了达到本课程的教学目标,我们将采用多种教学方法进行授课,包括:1.讲授法:通过讲解FPGA的基本概念、设计和应用,使学生掌握FPGA的基本知识和技能。

2.案例分析法:通过分析实际的FPGA设计和应用案例,使学生了解FPGA在实际工程中的应用和调试方法。

3.实验法:通过进行FPGA实验,使学生掌握FPGA的设计和验证技巧,以及调试和优化方法。

四、教学资源为了支持本课程的教学内容和教学方法,我们将准备以下教学资源:1.教材:选用权威、实用的FPGA教材,为学生提供系统的学习资料。

2.参考书:提供相关的FPGA参考书籍,为学生提供丰富的学习资源。

3.多媒体资料:制作精美的教学PPT和视频,增强课堂教学的趣味性和生动性。

4.实验设备:准备FPGA开发板和实验工具,为学生提供实践操作的机会。

五、教学评估本课程的评估方式包括平时表现、作业和考试三个方面,以全面客观地评价学生的学习成果。

1.平时表现:通过课堂参与、提问和讨论等方式,评估学生在课堂上的积极性和主动性。

基于FPGA的高性能计算加速器设计与实现

基于FPGA的高性能计算加速器设计与实现高性能计算在当今科学研究和工程领域中扮演着重要的角色。

为了满足对计算速度和效率的需求,许多研究人员和工程师开始探索新的计算加速方法。

其中,基于FPGA的高性能计算加速器设计与实现成为一种备受关注的方法。

FPGA(可编程逻辑门阵列)是一种可编程的硬件设备,能够用于构建各种数字电路。

它相比其他硬件设计方法具有更高的灵活性和适应性,使得它成为设计计算加速器的理想选择。

基于FPGA的高性能计算加速器设计与实现的关键在于将计算任务映射到FPGA的可编程逻辑中,并通过并行和硬件优化来提高计算性能。

下面将介绍几个关键方面,使你对这一领域有更深入的了解。

首先,设计和实现一个基于FPGA的高性能计算加速器需要一个合适的硬件架构。

这个架构应该被精心设计,以适应特定的计算任务。

一个合理的硬件架构可以通过并行计算单元、高带宽内存接口和高速数据传输通道来提高计算速度。

其次,为了实现高性能的计算加速,优化算法和数据结构是非常重要的。

通过合理选择和设计算法,可以提高计算效率和性能。

此外,通过优化数据结构的存储和访问方式,可以减少数据传输和存取的开销,进一步提高计算速度。

同时,要注意到FPGA和CPU之间的数据传输延迟问题。

由于FPGA与CPU 通常通过PCIe等总线进行通信,数据传输往往会成为整体计算性能的瓶颈。

一种解决方法是使用流水线或者数据并行的方式来降低数据传输的延迟。

此外,对于大规模计算任务,使用多个FPGA协同工作也是一种有效的方法。

通过将计算任务划分成多个子任务,并使用多个FPGA并行进行计算,可以进一步提高计算速度和性能。

最后,为了实现基于FPGA的高性能计算加速器的设计和实现,软件开发和硬件描述语言编程(HDL)技术是必须的。

通过使用HDL(如Verilog或VHDL)编写硬件描述代码,可以描述FPGA的架构和功能。

然后,通过软件开发工具(如Xilinx或Altera提供的开发工具)将硬件描述代码编译成可在FPGA上运行的二进制代码。

浅谈FPGA应用与设计实践教学与改革

门 阵列 ) 是 一 种 目前 应 用 非 常 广 泛 的 现 场 可 编程 逻 辑 器 件 ,被 称 之 为可 编程 ASC ( p l ain S eicItga— I A pi t p cf ne rt c o i

1 传统 F G P A应 用 与 设计 实践 教 学

. P e i ut,专 用 集 成 电路 ) P A 的 应 用 几 乎 遍 及 各 1 1 F GA 的特 点 及 其 开发 流程 dCr i c s ,F G

. . P A 行 各 业 , 比如 ASC设 计 、通 信 、控 制 、 电 力 电 子 等 领 1 1 1 F G 的 特 点 I

域 。其 主要 优 点 有 :设 计 周 期 短 ,功 耗 低 ,可 实 现 更 高

FG P A是 由掩 膜 可 编 程 阵 列 和 可 编 程 逻 辑 器 件 发 展

教 学方 法 进 行探 讨 、研 究 ,并 结合 实 际教 学经 验 及 F G 的特 点 提 出 了其 改 革 的 目的与 方 向 。 PA

关 键 词 :F GA;动 手 能 力 ;创 新 能 力 ;改 革 P

F G ( il rga P A FedP ormma l t A ry,现 场 可 编 程 点 放 在 自主 创 新 能 力 的 培养 上 。 beGae ra

总第 l3期第 3期 l

21 0 2年 9月

高 校 实S YANS HIGONGZ UO YANJ U I

S ra NO. 1 NO. e il 1 3, 3

Se . 201 pt 2

浅谈 F G P A应 用 与 设 计 实 践 教 学 与 改 革

PA 集 成 度 的 数 字 系 统 、嵌 入 式 系 统 等 。用 户 可 对 F GA 内 而来 ,所 以 F G 既 有 门 阵 列 器 件 的 通 用 性 和 高 集 成 P P 部 的逻 辑 模 块 和 I O模 块 重新 进行 配 置 ,以 实 现 数 字 逻 性 ,又有 可 编 程 器 件 的 用 户 可 编 程 性 。F GA与 传 统 的 / 辑 电路 , 以及 基 于 F G 的 S A PA R M、查 找 表 ( U L T) 等 , 可 编 程器 件 相 比 ,具 有 规 模 大 、速 度 快 、功 能 强 、功 耗 PA AI 它 还 具 有 静 态 可 重 复 编 程 和 动 态 在 系 统 重 构 的特 性 ,使 低 、适 用 性 广 的 特 点 。F G 与 专 用 集 成 电 路 ( SC, A piai p cf nertdCrut 相 比 ,具 有设 计 灵 p l t n S e icItgae i i) c o i c 得 硬 件 的 功能 可 以像 软 件 一 样 通 过 编 程 来 修 改 ,从 而 提 高 了设 计 的可 靠 性 、稳 定 性 和 灵 活 性 。传 统 的 设 计 ,将 活 、开 发 周 期 短 、设 计 成 本 低 廉 等 诸 多 优 势 。 FG P A是 由 R M 中的 程 序来 完 成 其 工 作 状 态 的 ,所 A F GA的 角 色 仅 仅 局 限 于 集成 电路 的应 用 和验 证 ,然 而 , P PA AM 进 行 编 程 。使 用 者 随 着 电子 技 术 的 迅 猛 发 展 ,集 成 度 更 高 ,功 耗 更 低 ,基 以 在 F G 运 行 过 程 中需 要 对 R 可 以根 据 不 同 的配 置模 式 ,采 取 不 同 的 编 程 方 式 。系 统 于 F G 的 电路 设 计 将 发 挥 出更 大 的 优 势 … 。 PA