DSP(第3章)

第3章-1 TMS320C6000系列DSP指令系统

B3,B4,B2 B5,B6,B7 ;能检测, 无冲突

|| [B0] SUB.S2 L5: [!B1] ADD.L2

B8,B9,B7 B5,B6,B7 ;不能检测

|| [B0] SUB.S2

B8,B9,B7

TMS320C6000系列DSP指令集

7.常用指令描述

(1)ABS整型数饱和绝对值

语法:ABS (.unit)

指令后一个周期 3FF6 0010h(1073086480) 3FF6 0010h(1073086480)

TMS320C6000系列DSP指令集

(2)ADD(U)有符号/无符号整型饱和加 语法:ADD (.unit) src1, src2,dst 或 ADDU (.L1 or .L2) src1,src2, dst 或 ADD (.D1 or .D2) src2, src1, dst .unit = .L1, .L2, .S1, .S2 .L1,.L2和.S1, .S2操作数描述:src2加到src1,将结果放入

TMS320C6000系列DSP指令集

• 在代码中使用方括号对条件操作进行描述,方括号内为条 件寄存器名。

[B0] ADD .L1 A1, A2, A3

|| [!B0] ADD .L2 B1, B2, B3 互斥指令

TMS320C6000系列DSP指令集

6.资源限制

(1)使用相同功能单元指令的限制 下面的执行包是无效的: ADD .S1 A0, A1, A2 || SHR .S1 A3, 15, A4 ;.S1被两条指令同时使用 下面的执行包是有效的: ADD .L1 A0, A1, A2 || SHR .S1 A3, 15, A4 ;使用两个不同功能单元

0000 4B7h

第3章节TMS320C54x数据寻址方式

返回本节

3.3 累加器寻址

累加器寻址是用累加器中的数值作为一个地址读 写程序存储器。共有两条指令可以采用累加器寻 址: READA

返回首页

3.2.1 数据存储器(dmad)寻址

使用数据存储器寻址的指令有:

MVDK Smem, dmad MVKD dmad, Smem MVDM dmad, MMR MVMD MMR, dmad

数据存储器寻址使用符号(符号地址)或一个表 示16位地址的立即数来指明寻址的数据存储单元 的16位绝对地址。例如:

程序存储器(pmad)寻址使用符号(符号地址)或一个 表示 16 位地址的立即数来给出程序空间的地址。例如, 把程序存储器中标号为 TABLE 单元中的值复制到 AR7 所 指定的数据存储器中去,指令可写为: MVPD TABLE,*AR7; 返回本节

3.2.3 端口地址(PA)寻址

使用端口地址的指令有:

LD

#0,ARP

;ARP=0(#k3)

LD

LD LD

#3,ASM

#50,DP #1234,A

;ASM=3(#k5)

;DP=50(#k9) ;A=1234(#lk)

返回首页

3.2 绝对寻址

3.2.1 数据存储器(dmad)寻址

3.2.2 程序存储器(pmad)寻址 3.2.3 端口地址(PA)寻址 3.2.4 长立即数*(lk)寻址

第三章DSP指令寻址方式

DP值 0000 0000 0

偏移量 000 0000

数据存储器 第0页:0000h~007Fh

0000 0000 0 0000 0000 1

0000 0000 1 0000 00010

0000 00010 1111 1111 1

1111 1

~ ~ ~ ~

111 1111 000 0000 第1页:0080h~00FFh

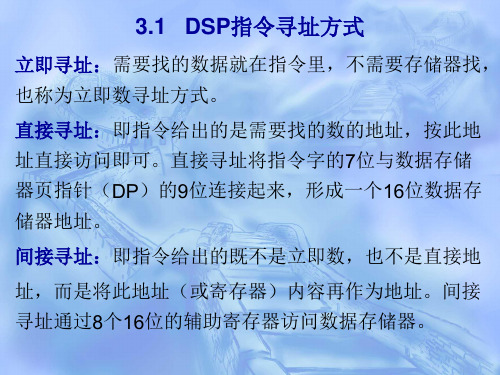

址,而是将此地址(或寄存器)内容再作为地址。间接

寻址通过8个16位的辅助寄存器访问数据存储器。

1.1 立即寻址方式 在立即寻址方式中,指令字中包含指令所需 的一个常数。两种立即寻址方式为: 短立即寻址。用短立即寻址的指令将一个8位、9 位或13位的常数作为操作数。短立即寻址指令为 一个单指令字,并且有一个常数嵌在该指令中。 长立即寻址。用常立即寻址的指令将一个16位常 数作为操作数,从而需要两个指令字。该常数作 为第二个指令字被发送。这个16位字值可以是绝 对常数或二进制补码。

3.1 DSP指令寻址方式

也称为立即数寻址方式。

立即寻址:需要找的数据就在指令里,不需要存储器找, 直接寻址:即指令给出的是需要找的数的地址,按此地

址直接访问即可。直接寻址将指令字的7位与数据存储 器页指针(DP)的9位连接起来,形成一个16位数据存 储器地址。 间接寻址:即指令给出的既不是立即数,也不是直接地

下一个辅助寄存器 除了更新当前辅助寄存器的内容外,某些指令还可以指 明下一个辅助寄存器或下一个AR。当这条指令执行完 成后,这个寄存器就成为当前辅助寄存器。允许用于指 定下一个辅助寄存器的指令用新的值装载ARP。当ARP 用该值装载时,以前的ARP值被装入辅助寄存器指针缓 冲器(ARB)。 例1.6说明了下一个辅助寄存器的选择和其他间接寻址的 特点。 例1.6 选择新的当前辅助寄存器。 MAR *,AR1;向ARP装入1,指令执行后使得AR1成为 当前辅助寄存器 LT *+,AR2;AR2是下一个辅助寄存器。用AR1指定的 地址内容装载TREG,AR1内容加1,指令执行后使得 AR2成为当前辅助寄存器。 MPY *;TREG乘以AR2所指定的单元内容

第3章C28xDSP的CPU与指令系统35页PPT

Fast & flexible interrupt management significantly reduce interrupt latency

28.05.2020

Code compatible with the TMS320C24x™ DSP family

CPU的信号主要包括4种: ① 存储器接口信号 ② 时钟和控制信号 ③ 复位和中断信号 ④ 仿真信号

28.05.2020

山东大学控制学院 张东亮

2

F281x DSP的CPU 单元结构框图

28.05.2020

山东大学控制学院 张东亮

3

C28x的CPU主要由总线、CPU寄存器、程序地址发 生器和控制逻辑、地址寄存器算术单元(ARAU)、算术逻 辑单元(ALU)、乘法器和移位器等逻辑部件组成,还包括 指令队列和指令译码单元、中断处理逻辑等。

28.05.2020

山东大学控制学院 张东亮

4

TMS320F2812 / TMS320F2810

Most Powerful - Most Integrated Dual Function Digital Signal Controller

Code security

128Kw Flash + 2Kw OTP

File

28.05.2020

Peripheral Bus

High-Performance CPU (C28xTM DSP Core)

Event Mgr A Event Mgr B 12-Bit ADC

Watchdog GPIO

150MIPS performance Single cycle 32 x32-bit MAC (or dual 16 x16 MAC) Very Fast Interrupt Response Single cycle read-modified-write F24x/LF240x Source Code Compatible

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

第3章TMS320F2812中断系统

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812的中断管理分为三级:

外设级中断管理 PIE(Peripheral Interrupt Expansion, PIE, 外设中断扩展)级中断管理 CPU级中断管理

4

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812支持32个CPU级中断源,并支持软 件和硬件两种中断。 软件中断:由INTR、ORIFR或TRAP指令激发。 硬件中断: 外部中断——由外部中断引脚上的信号触发。 内部中断——由片内外设的信号触发。

5

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812外设级中断管理主要负责外设内

部的中断源的屏蔽与使能。 PIE级中断管理主要负责将各种已使能的外设 中断进行分组管理并形成最终的CPU中断请求。 CPU级中断管理主要负责处理直接向CPU申请 的中断请求,这些中断请求分别来自PIE外设中 断模块、外部中断引脚和片内32位的CPU定时 器。 操作顺序: 首先由某个事件引起外设产生中断 请求并传送到PIE模块。

17

3.2 PIE中断扩展

TMS320F2812中断处理模式 在标准中断处理模式下,不使用调试中断使能寄存 器(DBGIER);只有在使用F2812实时调试模式 (Real-time Debug)且CPU被停止时,才使用调试中 断使能寄存器(DBGIER),这种情况下中断总开关 INTM不起作用。 特别地,若F2812采用实时调试模式而CPU仍然正 常运行时,则采用标准的中断处理模式。

10

3.1 TMS320F2812中断的基本原理与结构

TMS320F2812对于中断的处理主要分为下列4个步骤: ⑴硬件中断或软件中断提出中断请求。 ⑵F2812在能够响应中断的情况下响应中断请求。 ⑶保存现场,为执行中断服务程序作好准备。 ⑷执行中断服务子程序

DSP原理与应用---第3章 EMIF

DRAM是Dynamic RAM的缩写,中文含义为动态随机存取存储器, 需要不断的刷新,才能保存数据。而且是行列地址复用的,许多都有 页模式。SDRAM:Synchronous DRAM,即数据的读写需要时钟 来同步。 一个是静态的,一个是动态的,静态的是用的双稳态触发器来保存信 息,而动态的是用电子,要不时的刷新来保持。

DRAM容量大,SRAM容量小

SDRAM的结构

FLASH ROM

Flash-ROM(闪存)已经成为了目前最成功、流行的一种固态内存,与 EEPROM 相比具有读写速度快,而与 SRAM 相比具有非易失、以及价廉等优 势。而基于 NOR 和 NAND 结构的闪存是现在市场上两种主要的非易失闪存技 术。 Intel 于 1988 年首先开发出 NOR flash 技术,彻底改变了原先由 EPROM 和 EEPROM 一统天下的局面。紧接着,1989 年东芝公司发表了 NAND flash 技术(后将该技术无偿转让给韩国 Samsung 公司),强调降低每比特的成 本,更高的性能,并且象磁盘一样可以通过接口轻松升级。 NOR 的特点是芯片内执行(XIP,eXecute In Place),这样应用程序可以直 接在闪存内运行,不必再把代码读到系统 RAM 中。NOR 的传输效率很高,在 1~4MB 的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影 响了它的性能。 NAND 结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的 速度也很快,这也是为何所有的 U 盘都使用 NAND 闪存做为存储介质的原因。 应用 NAND 的困难在于需要特殊的系统接口。

NAND flash和NOR flash的对比

接口差别 NOR 闪存带有SRAM接口,有足够的地址引脚来寻址,可 以很容易地存取其内部的每一个字节。 NAND闪存使用复杂的I/O口来串行地存取资料,各个产品 或厂商的方法可能各不相同。8个引脚用来传送控制、地 址和资料信息。NAND读和写操作采用512字节的块,这 一点有点像硬盘管理此类操作,很自然地,基于NAND的 闪存就可以取代硬盘或其它块设备。

DSP原理与应用考试重点

DSP原理与应用考试重点DSP原理与应用考试重点(仅供参考,祝大家考试顺利)第一章 DSP概述1.3 哈弗结构:采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线。

独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大提高了数据的处理能力和指令的执行速度,非常适合实时的数字信号处理。

思考题与习题1-1论述通用微处理器和DSP芯片之间的共同特点和主要区别。

答:共同特点:都具有高速运算和控制能力主要区别:DSP具有特殊结构,其芯片内部采用程序和数据分开的哈弗结构,同时能读取指令和数据。

1-2论述DSP芯片结构上的主要特点。

答:DSP芯片内部采用程序和数据分开的哈弗结构,采用双存储空间,有各自独立的程序总线和数据总线,使取指、译码、执行并行完成。

什么是DSP给记下。

第二章 CUP结构与指令集2.1 CPU的结构1.CPU部分结构:程序的取指、指令分配和译码机构:程序取指单元(由程序总线与片内程序存储器相连)、指令分配单元和指令译码单元。

2.程序执行机构:2个对称数据通道(A和B)、2个对称的通用寄存器组、2组对称的功能单元(每组4个)、控制寄存器、控制逻辑及中断逻辑等。

3.芯片测试、仿真端口及其控制逻辑。

取指包:如C67xx系列芯片的程序总线宽度为2.流水线译码的2个节拍:1.指令分配(DP)2.指令译码(DC)。

2.5.1 中断类型和中断信号中断类型:1.复位 2.不可屏蔽中断 3.可屏蔽中断。

2.5.2中断服务表(IST)1.中断服务表(IST):是包含中断服务代码取指包的一个地址表。

2.中断服务取指包(ISFP):包含8条指令,主要存放中断服务指令,当中断指令过长不能存放在单个FP中时,就需要跳转到下一个中断程序。

3.中断服务表指针(ISTP)寄存器:用于确定中断服务程序在中断服务表中的地址,ISTP中的字段ISTB确定IST的地址基址,另一个字段HPEINT确定当前响应的中断,并给出取指包在IST中的位置。

DSP原理及应用第五版汪春梅课后答案

DSP原理及应用第五版汪春梅课后答案第一章绪论1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低道滤波器等。

DSP系统的工作过程:将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

数字信号处理器对x(n)进行处理,得数字信号y(n)。

经D/A转换器,将y(n)转换成模拟信号经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

9、简述DSP系统的设计步骤。

答:明确设计任务,确定设计目标。

算法模拟,确定性能指令。

选择DSP芯片和外围芯片。

设计实时的DSP芯片系统。

硬件和软件调试。

系统集成和测试。

第二章TMS320C54x硬件结构1、TMS320C54X芯片的基本结构都包括哪些部分,答:中央处理器内部总线结构2、TMS320C54X芯片的CPU主要由哪几部分组成,答:40位的算术运算逻辑单2个40位的累加器(ACCA、ACCB).1个运行-16至31位的桶形移位寄存器。

17X17位的乘法器和40位加法器构成的乘法器-加法器单元(MAC)。

比较、选择,有所无指令编码器。

CPU状态和控制寄存器。

3、TMS320VC5402共有多少可屏蔽中断,它们分别是什么,和属于哪一-类中断RSMI源,答:TMS320VC5402有13个可屏肢中断,和属于外部硬件中断。

RSNMI 第三章TMS320C54x指令系统第一次1、已知(80H)=-50H,AR2-84H,AR3-86H,AR4 88H。

MVKD 80H,*AR2WVDD*AR2,*AR3.WVDM 86H,AR4运行以上程序后,(80I)、(84H)、*AR3和AR4的值分别等于多少,解:(80H)--50H,(84H);-50H,*AR3=50H,AR4-50H 2、已知,(80H):20H、(8IH)=30H。

《DSP系统设计及应用》第三章

3.2.3

TMS320F206引脚 TMS320F206引脚

6

7

8

9

10

11

3.2.4

包括: 包括:

中央处理单元(CPU)

一个16位的比例转移器、 一个16位的比例转移器、 16位的比例转移器 一个16*16位并行乘法器 16*16位并行乘法器、 一个16*16位并行乘法器、 一个32 中央算术逻辑单元、 32位 一个32位中央算术逻辑单元、 一个32 累加器以及一个条件转移器。 32位 以及一个条件转移器 一个32位累加器以及一个条件转移器。 1.状态和控制寄存器 ST0和ST1两个状态寄存器保存各种各样的条件和模式的状态 两个状态寄存器保存各种各样的条件和模式的状态, ST0和ST1两个状态寄存器保存各种各样的条件和模式的状态, 包含状态位和控制位。 包含状态位和控制位。

12

13

2.输入比例转移器 (参看结构图)

DRDB它有一个 16 位的输入连到了数据总线DRDB DRDB 它有一个16 位的输入连到了数据总线 DRDB , 它有一个 16位的输入连到了数据总线 DRDB, 一个32位输出连到了CALU 32位输出连到 据空间来的数据得到CALU的路径, CALU的路径 据空间来的数据得到CALU的路径,这部分操作不需要 时钟周期,它用来把从内存来的16位数据与32 16位数据与32位 时钟周期,它用来把从内存来的16位数据与32位CALU 对齐。这对于位逻辑运算是很有用的。 对齐。这对于位逻辑运算是很有用的。 这个比例转移器在输入数据上产生一个0 16位 这个比例转移器在输入数据上产生一个0到16位 的左移,输出的LBS LBS用 填满;MSB可以被 可以被0 的左移,输出的LBS用0填满;MSB可以被0或有符号扩 展位填满,具体由状态寄存器的ST1的SXM位的值决定。 展位填满, 具体由状态寄存器的ST1 SXM位 的值决定。 ST 转移数据由一个存在于指令的常数或TREG TREG中的一 转移数据由一个存在于指令的常数或TREG中的一 个变量来确立。 个变量来确立。在指令中的转移数允许为特定的比例 或调整操作在代码中特定的点。TREG基本转移允许比 或调整操作在代码中特定的点。TREG基本转移允许比 例因素去适应系统。 例因素去适应系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

块的建立 注意,C编译器(将C语言程序转换为汇编程序)产生的块: 会产生已初始化块(如.text,.cinitm,.const,.switch) 和未初始化块(如.bss,.stack,.sysmem) 不使用.data块 会产生一些新块

第三章 公共目标文件格式

3.2 COFF文件

第三章 公共目标文件格式

3.2 COFF文件

块的建立

汇编器有六个伪指令来创立块: – .bss 创立未初始化块 – .usect – .text – .data 创立已初始化块 – .sect – .asect 【注】如用户未使用任何伪指令,则汇编器将把所以内容汇编入.text 块。

第三章 公共目标文件格式

第三章tion) 实现方法:

重定位的工作通常由汇编器和链接器共同完成。 – 汇编器为块内所需重定位的标号创建一个重定位入口表,表中提供各 个符号的相应重定位入口信息(如其定义行的SPC值,重定位地址的 计算方法等)。此表在汇编结束各个块的COFF中提供。 – 链接器按如下步骤完成重定位: • 把块定位到存储器中以确定各块的起始位置; • 计算各个需重定位符号在存储器中的具体位置; • 修改引用符号处的符号值以便引用。

第三章 公共目标文件格式

3.2 COFF文件

块的概念及分类

块(section)是目标文件的最小单位。即指最终在存储器中占据连续 空间的一块代码或数据。 COFF文件中可包含如下几种块: – 程序块(.text section):通常包含可执行代码 – 数据块(.data section):通常包含已初始化数据 – 变量块(.bss section):通常用来为未初始化变量保留 存储空间 – 命名块(.named section):是用户自定义块 前三种是DSP系统的基本缺省块。

第三章 公共目标文件格式

3.2 COFF文件

程序重定位(Relocation)

运行时的重定位: – 有时希望程序目标码存储和运行使用不同的存储器空间,如 保存在ROM中,运行却希望在SRAM中完成,此时需对程序 进行重定位。 – 运行时的重定位也是由链接器完成。即使用SECTIONS命令对 块进行二次分配。如:.text : load=CODE run=RAMB0 其中, load和 run分别是用于装载地址和运行地址的关键字。

.asect “section name”, address

第三章 公共目标文件格式

3.2 COFF文件

关于块程序计数器SPC 汇编器在对源程序分块汇编时,为每种类型 的块分配一个SPC,用来指示各块的内容顺 序。SPC总是指向本块的当前值。

伪指令效用期 • 长效应伪指令:如.text,.data,.sect 和.asect,汇编器遇到 该类伪指令时,则停 止对当前块的汇编,开始对该指令指 定块的 汇编,直至遇到另一个长效应伪指令为止。 • 短效应伪指令:如.bss和.usect,汇编器 遇到该类伪指令 时,则暂停对当前块的汇编, 开始对该指令指定块的汇 编,然后继续进行 对上一个长效应伪指令的汇编。

第三章 公共目标文件格式

3.2 COFF文件

块的组合及其在存储器中的映象

汇编器将源文件的块类别识别出来,由链接器将各种块组合起来, 形成可执行的COFF输出模块。同时,链接器还将为各输出块选 择存储器地址。 • 链接器用两条伪指令完成上述功能: – MEMORY: 定义目标系统的存储器映象,可以给它们命名,规 定 起始地址和长度 – SECTIONS:指定怎样组合各输入块以及将各输出块存放在存储器 的哪个位置 • 链接器定位块的两种方法 – 缺省的定位算法 – 用MEMORY和SECTIONS 命令分配存储器

第三章

公共目标文件格式(COFF)

第三章 公共目标文件格式

3.1 引言

1、DSP开发环境

第三章 公共目标文件格式

3.2 COFF文件

COFF文件格式是基于块(section)的概念建立的,即程序被分解 成各种块的组合体:如文本块、数据块等。 COFF的特点: 便于实现模块化程序设计 为管理代码块和目标系统存储器提供更强有力和更加灵活的方法 程序员设计时只需基于代码块和数据块等概念进行,不需关注每 条命令或每个数据的具体目标地址。至于它们的最终将处于存储器 的哪个位置,将由链接器来安排 为程序编写和移植提供了很大的方便

第三章 公共目标文件格式

3.2 COFF文件

程序重定位(Relocation) 概念:

汇编器在汇编源程序时,给各个块分配一个SPC,且每个块的SPC 均 从0开始。 此时,源程序中的标号(如前例中的aloop)值取该块在本语句的SPC 值(aloop=0001H),即相当该块起始位置的偏移量。 链接器在给各个块分配存储器空间的时候,不能保证每个块都从 0000H单元开始,故源程序中的标号需随各块在存储器中的具体位置重新 赋值,此即重定位。

第三章 公共目标文件格式

3.2 COFF文件

COFF文件内的符号

由汇编器和链接器创建的COFF文件中包含一个符号表,专门存储程序 中所用到的符号信息。 • 内部符号和外部符号 – 内部符号:本块内定义,本块内使用。重定位由链接器借助SPC完 成,不列入符号表中。 – 外部符号:在一个模块中定义,在另一个模块中使用,汇编时需列 入符号表,以便帮助链接器重定位该符号。 • 外部符号的声明 – .global :全局符号,所有模块都可使用,可能时参考符号和 定义符号。 – .ref :参考符号,在其它模块中定义,在本模块中只引用。 – .def :定义符号,在当前模块中声明,在其它模块中引用。

第三章 公共目标文件格式

3.2 COFF文件

初始化块的创立

初始化块的作用是包含可执行代码或初始化数据。 有四条伪指令可创立 初始化块:.text,.data,.sect 和.asect。 .text .text:创建存放可执行代码的.text块 例:add: LAC 0FH aloop: SBLK #1 BLEZ aloop SACL varl , 0 .data:创建存放已初始化数据的.data块 .data coeff .word 011h, 022h, 033h .sect:创建具可重定位地址的命名块 .sect “section name” .asect:创建具绝对地址的命名块

第三章 公共目标文件格式

3.2 COFF文件

COFF文件的装载

链接器只是为COFF文件的各块分配了在存储器中的地址空间,并 未真正将它们装载至存储器中。程序运行之前,还需人为完成程 序的装 载。常用的装载方法有如下三种: 用TMS320C1X/C2X/C2XX/C5X的调试工具装载; 用十六进制转换实用程序dspdex装载; 在操作系统和监视器软件的控制下装载,此时用户需自己编写 装载程序。

未初始化块的创立

• 未初始化块的作用是在存储器(一般是RAM型)中保留部分空间,以便 程序运行时创建和存储变量。 • 一般用两条伪指令.bss和.usect创立未初始化块。 .bss: – 功能:在.bss内保留空间 – 语法格式: .bss 符号,字数 符号指向.bss命令保留的第一个字,通常用第一个未初始化变 量的变量名来表示。 字数指明保留空间的大小。 – 例:.bss varl, 1 .usect – 语法格式:符号 .usect “块名”,字数 – 功能:在指定块内为由符号指向的变量表保留一定字数的空 间,该 块必须是用户自定义的。 – 例:inbuf .usect newvars, 7