ad834乘法器电路

AD8348ARU中文资料

50 MHz to 1000 MHzQuadrature DemodulatorAD8348 Rev. AInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.FEATURESIntegrated I/Q demodulator with IF VGA amplifier Operating IF frequency 50 MHz to 1000 MHz(3 dB IF BW of 500 MHz driven from R S = 200 Ω) Demodulation bandwidth 75 MHzLinear-in-decibel AGC range 44 dBThird-order interceptIIP3 +28 dBm @ minimum gain (F IF = 380 MHz) IIP3 −8 dBm @ maximum gain (F IF = 380 MHz) Quadrature demodulation accuracyPhase accuracy 0.5°Amplitude balance 0.25 dBNoise figure 11 dB @ maximum gain (F IF = 380 MHz) LO input −10 dBmSingle supply 2.7 V to 5.5 VPower-down modeCompact, 28-lead TSSOP packageAPPLICATIONSQAM/QPSK demodulatorW-CDMA/CDMA/GSM/NADCWireless local loopLMDS FUNCTIONAL BLOCK DIAGRAM3678-1Figure 1.GENERAL DESCRIPTIONThe AD8348 is a broadband quadrature demodulator with an integrated intermediate frequency (IF), variable gain amplifier (VGA), and integrated baseband amplifiers. It is suitable for use in communications receivers, performing quadrature demodulation from IF directly to baseband frequencies. The baseband amplifiers are designed to interface directly with dual-channel ADCs, such as the AD9201, AD9283, and AD9218, for digitizing and post-processing.The IF input signal is fed into two Gilbert cell mixers through an X-AMP® VGA. The IF VGA provides 44 dB of gain control.A precision gain control circuit sets a linear-in-decibel gain char-acteristic for the VGA and provides temperature compensation. The LO quadrature phase splitter employs a divide-by-2 frequency divider to achieve high quadrature accuracy and amplitude balance over the entire operating frequency range.Optionally, the IF VGA can be disabled and bypassed. In this mode, the IF signal is applied directly to the quadrature mixer inputs via the MXIP and MXIN pins. Separate I- and Q-channel baseband amplifiers follow the baseband outputs of the mixers. The voltage applied to the VCMO pin sets the dc common-mode voltage level at the baseband outputs. Typically, VCMO is connected to the internal VREF voltage, but it can also be connected to an external voltage. This flexibility allows the user to maximize the input dynamic range to the ADC. Connecting a bypass capacitor at each offset compensation input (IOFS and QOFS) nulls dc offsets produced in the mixer. Offset compensation can be overridden by applying an external voltage at the offset compensation inputs.The mixers’ outputs are brought off-chip for optional filtering before final amplification. Inserting a channel selection filter before each baseband amplifier increases the baseband amplifiers’ signal handling range by reducing the amplitude of high level, out-of-channel interferers before the baseband signal is fed into the I/Q baseband amplifiers. The single-ended mixer output is amplified and converted to a differential signal for driving ADCs.AD8348Rev. A | Page 2 of 28TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 Functional Block Diagram..............................................................1 General Description.........................................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 Absolute Maximum Ratings............................................................6 ESD Caution..................................................................................6 Pin Configuration and Function Descriptions.............................7 Equivalent Circuits...........................................................................9 Typical Performance Characteristics...........................................11 VGA and Demodulator.............................................................11 Demodulator Using MXIP and MXIN....................................14 Final Baseband Amplifiers........................................................15 VGA/Demodulator and Baseband Amplifier.........................16 Theory of Operation......................................................................18 VGA..............................................................................................18 Downconversion Mixers...........................................................18 Phase Splitter...............................................................................18 I/Q Baseband Amplifiers...........................................................18 Enable...........................................................................................18 Baseband Offset Cancellation...................................................18 Applications.....................................................................................20 Basic Connections......................................................................20 Power Supply...............................................................................20 Device Enable.............................................................................20 VGA Enable................................................................................20 Gain Control...............................................................................20 LO Inputs.....................................................................................20 IF Inputs......................................................................................20 MX Inputs...................................................................................20 Baseband Outputs......................................................................21 Output DC Bias Level................................................................21 Interfacing to Detector for AGC Operation...............................21 Baseband Filters..........................................................................22 LO Generation............................................................................23 Evaluation Board........................................................................23 Outline Dimensions.......................................................................28 Ordering Guide.. (28)REVISION HISTORY4/06—Rev. 0 to Rev. AUpdated Format..................................................................Universal Changes to Specifications................................................................3 Changes to IF Inputs Section........................................................20 Changes to Evaluation Board Section..........................................23 Changes to Table 6..........................................................................27 Changes to Ordering Guide..........................................................28 8/03—Revision 0: Initial VersionAD8348Rev. A | Page 3 of 28SPECIFICATIONSV S = 5 V , T A = 25o C, F LO = 380 MHz, F IF = 381 MHz, P LO = −10 dBm, R S (LO) = 50 Ω, R S (IFIP and MXIP/MXIN) = 200 Ω, unless otherwise noted. Table 1.Parameter Conditions Min Typ Max Unit OPERATING CONDITIONS LO Frequency Range External input = 2 × LO frequency 100 2000 MHz IF Frequency Range 50 1000 MHz Baseband Bandwidth 75 MHz LO Input Level 50 Ω source −12 −10 0 dBm V SUPPLY (V S ) 2.7 5.5 V Temperature Range −40 +85 °C IF FRONT END WITH VGA IFIP to IMXO (QMXO), ENVG = 5 V, IMXO/QMXO load = 1.5 kΩ Input Impedance Measured differentially across MXIP/MXIN 200||1.1 Ω||pF Gain Control Range 44 dB Maximum Conversion Voltage Gain VGIN = 0.2 V (maximum voltage gain) 25.5 dB Minimum Conversion Voltage Gain VGIN = 1.2 V (minimum voltage gain) −18.5 dB 3 dB Bandwidth 500 MHz Gain Control Linearity VGIN = 0.4 V (+21 dB) to 1.1 V (−14 dB) ±0.5 dB IF Gain Flatness F IF = 380 MHz ± 5% (VGIN = 1.2 V) 0.1 dB p-p F IF = 900 MHz ± 5% (VGIN = 1.2 V) 1.3 dB p-p Input 1 dB Compression Point (P1dB) VGIN = 0.2 V (maximum gain) −22 dBmVGIN = 1.2 V (maximum gain) +13 dBm Second-Order Input Intercept (IIP2) IF1 = 385 MHz, IF2 = 386 MHz+3 dBm each tone from 200 Ω source, 65 dBm VGIN = 1.2 V (minimum gain)−42 dBm each tone from 200 Ω source, 18 dBmVGIN = 0.2 V (maximum gain) Third-Order Input Intercept (IIP3) IF1 = 381 MHz, IF2 = 381.02 MHz Each tone 10 dB below P1dB from 200 Ω source,28 dBm VGIN = 1.2 V (minimum gain)Each tone 10 dB below P1dB from 200 Ω source,−8 dBmVGIN = 0.2 V (maximum gain)LO Leakage Measured at IFIP , IFIN −80 dBm Measured at IMXO/QMXO (LO = 50 MHz) −60 dBm Demodulation Bandwidth Small signal 3 dB bandwidth 75 MHz Quadrature Phase Error 1LO = 380 MHz (LOIP/LOIN 760 MHz) −0.7 ±0.1 +0.7 Degrees vs. temperature −0.0032 °/°C vs. baseband frequency (dc to 30 MHz) +0.01 °/MHzI/Q Amplitude Imbalance 1−0.3 ±0.05 +0.3 dB vs. temperature 0 dB/°C vs. baseband frequency (dc to 30 MHz) ±0.0125 dB Noise Figure (Double Sideband) Maximum gain, from 200 Ω source,F IF = 380 MHz10.75 dB Mixer Output Impedance 40 Ω Capacitive Load Shunt from IMXO, QMXO to VCMO 0 10 pF Resistive LoadShunt from IMXO, QMXO to VCMO 200 1.5 kΩ Mixer Peak Output Current 2.5 mAAD8348Rev. A | Page 4 of 28Parameter Conditions Min Typ Max Unit IF FRONT END WITHOUT VGA From MXIP , MXIN to IMXO (QMXO), ENVG = 0 V, IMXO/QMXO load = 1.5 kΩ Input Impedance Measured differentially across MXIP/MXIN 200||1.5 Ω||pF Conversion voltage Gain 10.5 dB 3 dB Output Bandwidth 75 MHz IF Gain Flatness F IF = 380 MHZ ± 5% 0.1 dB p-p F IF = 900 MHZ ± 5% 0.15 dB p-p Input 1 dB Compression Point (P1dB) −4 dBm Third-Order Input Intercept (IIP3) IF1 = 381 MHz, IF2 = 381.02 MHz 14 dBm Each tone 10 dB below P1dB from200 Ω sourceLO Leakage Measured at MXIP/MXIN −70 dBm Measured at IMXO, QMXO −60 dBm Demodulation Bandwidth Small signal 3 dB bandwidth 75 MHz Quadrature Phase Error LO = 380 MHz (LOIP/LOIN 760 MHz,single-ended)−2 ±0.5 +2 Degrees I/Q Amplitude Imbalance 0.25 dB Noise Figure (Double Sideband) From 200 Ω source, F IF = 380 MHz 21 dB I/Q BASEBAND AMPLIFIER From IAIN to IOPP/IOPN and QAIN to QOPP/QOPN, R LOAD = 2 kΩ, single-ended to groundGain 20 dB Bandwidth 10 pF differential load 125 MHz Output DC Offset (Differential) LO leakage offset corrected using 500 pFcapacitor on IOFS, QOFS (V IOPP − V IOPN )−50 ±12 +50 mV Output Common-Mode Offset (V IOPP + V IOPN )/2 − VCMO −75 ±35 +75 mV Group Delay Flatness 0 MHz to 50 MHz 3 ns p-p Input-Referred Noise Voltage Frequency = 1 MHz 8 nV/√Hz Output Swing Limit (Upper) V S −1 V Output Swing Limit (Lower) 0.5 V Peak Output Current 1 mA Input Impedance 50||1 kΩ||pF Input Bias Current 2 μARESPONSE FROM IF AND MX INPUTS TO BASEBAND AMPLIFIER OUTPUT IMXO and QMXO connected directly toIAIN and QAIN, respectivelyGain From MX I P/MX I N 30.5 dB From IFIP/IFIN, VGIN = 0.2 V 45.5 dB From IFIP/IFIN, VGIN = 1.2 V 1.5 dB CONTROL INPUT/OUTPUTS VCMO Input Range V S = 5 V 0.5 1 4 V V S = 2.7 V 0.5 1 1.7 V VREF Output Voltage 0.95 1 1.05 V Gain Control Voltage Range VGIN 0.2 1.2 V Gain Slope −55 −50 −45 dB/V Gain Intercept Linear extrapolation back to theoreticalgain at VGIN = 0 V55 61 67 dB Gain Control Input Bias Current 1 μA LO INPUTSLOIP Input Return Loss LOIN ac-coupled to ground(760 MHz applied to LOIP)−6 dBAD8348Rev. A | Page 5 of 28Parameter Conditions Min Typ Max Unit POWER-UP CONTROL ENBL Threshold Low Low = standby 0 V S /2 1 V ENBL Threshold High High = enable V S − 1 V S /2 V S V Input Bias Current 2 μA Power-Up Time Time for final baseband amplifiers to bewithin 90% of final amplitude45 μs Power-Down Time Time for supply current to be <10% ofenabled value700 ns POWER SUPPLIES VPOS1, VPOS2, VPOS3Voltage 2.7 5.5 V Current (Enabled) V S = 5 V, V ENBL = 5 V 38 48 58 mA Current (Standby) V S = 5 V, V ENBL = 0 V 75 μA1These parameters are guaranteed but not tested in production. Limits are ±6 Σ from the mean.AD8348Rev. A | Page 6 of 28ABSOLUTE MAXIMUM RATINGSTable 2.Parameter RatingSupply Voltage on VPOS1, VPOS2, VPOS3 Pins 5.5 VLO Input Power 10 dBm (re: 50 Ω)IF Input Power 18 dBm (re: 200 Ω)Internal Power Dissipation 450 mWθJA 68°C/WMaximum Junction Temperature 150°C Operating Temperature Range −40°C to +85°C Storage Temperature Range −65°C to +125°CLead Temperature (Soldering, 60 sec) 300°CStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stressrating only; functional operation of the device at these or anyother conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affectdevice reliability.ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.AD8348Rev. A | Page 7 of 28PIN CONFIGURATION AND FUNCTION DESCRIPTIONSLOIPVPOS1IOPN IOPP VCMO IAIN COM3IMXO COM2IFIN IFIP VPOS2IOFS VREF 03678-002Figure 2. 28-Lead TSSOP Pin ConfigurationTable 3. Pin Function Descriptions—28-Lead TSSOPPin No. Mnemonic DescriptionEquivalent Circuit 1, 28LOIP , LOINLO Inputs. For optimum performance, these inputs should be ac-coupled and driven differentially. Differential drive from single-ended sources can be achieved via a balun. To obtain a broadband 50 Ω input impedance, connect a 60.4 Ω shunt resistor between LOIP and LOIN. Typical input drive level is equal to −10 dBm.A2, 12, 20 VPOS1, VPOS2, VPOS3 Positive Supply for LO, IF, and Biasing and Baseband Sections, Respectively. These pinsshould be decoupled with 0.1 μF and 100 pF capacitors.3, 4, 25, 26 IOPN, IOPP , QOPP , QOPN I- and Q-Channel Differential Baseband Outputs. Typical output swing is equal to 2 V p-pdifferential. The dc common-mode voltage level on these pins is set by the voltage on VCMO.B 5 VCMO Baseband DC Common-Mode Voltage. The voltage applied to this pin sets the dccommon-mode levels for all the baseband outputs and inputs (IMXO, QMXO, IOPP , IOPN, QOPP , QOPN, IAIN, and QAIN). This pin can be connected either to VREF or to a reference voltage from another device (typically an ADC).C6, 23 IAIN, QAIN I- and Q-Channel Baseband Amplifier Inputs. The single-ended signals on these pins arereferenced to VCMO and must have a dc bias equal to the dc voltage on the VCMO pin. If IMXO (QMXO) is dc-coupled to IAIN (QAIN), biasing will be provided by IMXO (QMXO). If an ac-coupled filter is placed between IMXO and IAIN, these pins can be biased from the source driving VCMO through a 1 kΩ resistor. The gain from IAIN/QAIN to the differential outputs (IOPP/IOPN and QOPP/QOPN) is 20 dB.D7, 22 COM3 Ground for Biasing and Baseband Sections. 8, 21 IMXO, QMXO I- and Q-Channel Mixer Baseband Outputs. These are low impedance (40 Ω) outputs whosebias levels are set by the voltage applied to the VCMO pin. These pins are typically connected to IAIN and QAIN, respectively, either directly or through a filter. Each output can drive a maximum current of 2.5 mA.H9 COM2 IF Section Ground. 10, 11 IFIN, IFIP IF Inputs. IFIN should be ac-coupled to ground. The single-ended IF input signal shouldbe ac-coupled into IFIP . The nominal differential input impedance of these pins is 200 Ω. For a broadband 50 Ω input impedance, a minimum-loss L pad should be used; R SERIES = 174 Ω, R SHUNT = 57.6 Ω. This provides a 200 Ω source impedance to the IF input. However, the AD8348 does not necessarily require a 200 Ω source impedance, and a single shunt 66.7 Ω resistor can be placed between IFIP and IFIN.E13, 16 IOFS, QOFS I- and Q-Channel Offset Nulling Inputs. DC offsets on the I-channel mixer output (IMXO)can be nulled by connecting a 0.1 μF capacitor from IOFS to ground. Driving IOFS with a fixed voltage (typically a DAC calibrated such that the offset at IOPP/IOPN is nulled) can extend the operating frequency range to include dc. The QOFS pin can likewise be used to null offsets on the Q-channel mixer output (QMXO).F14 VREF Reference Voltage Output. This output voltage (1 V) is the main bias level for the deviceand can be used to externally bias the inputs and outputs of the baseband amplifiers. The typical maximum drive current for this output is 2 mA.GAD8348Rev. A | Page 8 of 28Pin No. Mnemonic Description EquivalentCircuit 15 ENBL Chip Enable Input. Active high. Threshold is equal to V S /2. D 17 VG IN Gain Control Input. The voltage on this pin controls the gain on the IF VGA. The gain control voltage range is from 0.2 V to 1.2 V and corresponds to a conversion gain range from +25.5 dB to −18.5 dB. This is the gain to the output of the mixers (that is, IMXO and QMXO). There is an additional 20 dB of fixed gain in the final baseband amplifiers (IAIN to IOPP/IOPN and QAIN to QOPP/QOPN). Note that the gain control function has a negative sense (that is, increasing voltage decreases gain).D18, 19 MXIP , MXIN Auxiliary Mixer Inputs. If ENVG is low, the IFIP and IFIN inputs are disabled and MXIP and MXIN are enabled, allowing the VGA to be bypassed. The auxiliary mixer inputs are fully differential inputs that should be ac-coupled to the signal source.I24 ENVG Active High VGA Enable. When ENVG is high, IFIP and IFIN inputs are enabled and MXIP and MXIN inputs are disabled. When ENVG is low, MXIP and MXIN inputs are enabled and IFIP and IFIN inputs are disabled.D27 COM1 LO Section Ground.AD8348Rev. A | Page 9 of 28EQUIVALENT CIRCUITSLOIN LOIP03678-003Figure 3. Circuit A VCMOVPOS3IOPP , IOPN,QOPP , QOPN 03678-004Figure 4. Circuit BVCMO03678-005Figure 5. Circuit C 03678-006Figure 6. Circuit DVPOS2IFIPIFIN03678-007Figure 7. Circuit E03678-008Figure 8. Circuit FAD8348Rev. A | Page 10 of 2803678-009Figure 9. Circuit G03678-010Figure 10. Circuit H03678-011Figure 11. Circuit IRev. A | Page 11 of 28TYPICAL PERFORMANCE CHARACTERISTICSVGA AND DEMODULATORVGIN (V)V G A A N D M I X E R G A I N (d B )L I N E A R I T Y E R R O R (d B )0.20.30.4–20–5–10–15105030252015–6–3–4–50–1–243210.50.60.70.80.9 1.0 1.1 1.203678-012Figure 12. Mixer Gain and Linearity Error vs. VGIN, V POS = 5 V, F IF = 380 MHz,F BB = 1 MHz, Temperature = −40°C, +25°C, +85°CVGIN (V)V G A A N D M I X E R G A I N (d B )L I N E A R I T Y E R R O R (d B )0.20.30.4–25–10–15–2050–525201510–6–3–4–50–1–243210.50.60.70.80.9 1.0 1.1 1.203678-013Figure 13. Mixer Gain and Linearity Error vs. VGIN, V POS = 5 V, F IF = 900 MHz,F BB = 1 MHz, Temperature = −40°C, +25°C, +85°C VGIN (V)V G A A N D M I X E R G A I N (d B )L I N E A R I T Y E R R O R (d B )0.20.30.4–6–3–4–50–1–243210.50.60.70.80.91.01.11.203678-014Figure 14. Mixer Gain and Linearity Error vs. VGIN, V POS = 2.7 V, F IF = 380 MHz,F BB = 1 MHz, Temperature = −40°C, +25°C, +85°CVGIN (V)V G A A N D M I X E R G A I N (d B )L I N E A R I T Y E R R O R (d B )0.20.30.4–25–10–15–2050–525201510–6–3–4–50–1–243210.50.60.70.80.91.01.11.203678-015Figure 15. Mixer Gain and Linearity Error vs. VGIN, V POS = 2.7 V, F IF = 900 MHz,F BB = 1 MHz, Temperature = −40°C, +25°C, +85°CIF FREQUENCY (MHz)V G A A N D M I X E R G A I N (d B )100182022242628200300400500600700800900100003678-016Figure 16. Gain vs. F IF , VGIN = 0.2 V, F BB = 1 MHz,Temperature = −40°C, +25°C, +85°CIF FREQUENCY (MHz)V G A A N D M I X E R G A I N (d B )100–30–25–20–15200300400500600700800900100003678-017Figure 17. Gain vs. F IF , VGIN = 1.2 V, F BB = 1 MHz,Temperature = −40°C, +25°C, +85°CRev. A | Page 12 of 28BASEBAND FREQUENCY (MHz)V G A A N D M I X E R G A I N (d B )1001718192021222325262427203040506070809010003678-018Figure 18. Gain vs. F BB , VGIN = 0.2 V, F IF = 380 MHz, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°CBASEBAND FREQUENCY (MHz)V G A A N D M I X E R G A I N (d B )10–26–23–20–17203040506070809010003678-019Figure 19. Gain vs. F BB , VGIN = 1.2 V, F IF = 380 MHz, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°C VGIN (V)I N P U T 1d B C O M P R E S S I O N P O I N T (d B m ) (r e 200Ω)0.30.2–25–10–15–20–515100.40.50.60.70.80.91.01.11.203678-020Figure 20. Input 1 dB Compression Point (IP1dB) vs. VGIN, F IF = 380 MHz, F BB = 1 MHz, V POS = 2.7 V, 5 V, Temperature = −40°C, +25°C, +85°CVGIN (V)I N P U T 1d B C O M P R E S S I O N P O I N T (d B m ) (r e 200Ω)0.30.2–20–5–10–15105020150.40.50.60.70.80.91.01.11.203678-021Figure 21. Input 1 dB Compression Point (IP1dB) vs. VGIN, F IF = 900 MHz, F BB = 1 MHz, V POS = 2.7 V, 5 V, Temperature = −40°C, +25°C, +85°CIF FREQUENCY (MHz)I N P U T I I P 3 (d B m ) (r e 200Ω)20010024262528273029300400500600700800900100003678-022Figure 22. IIP3 vs. F IF , VGIN = 1.2 V, F BB = 1 MHz, V POS = 2.7 V, 5 V, Temperature = −40°C, +25°C, +85°C, Tone Spacing = 20 kHzIF FREQUENCY (MHz)I N P U T I I P 3 (dB m ) (r e 200Ω)100200–15–10–5300400500600700800900100003678-023Figure 23. IIP3 vs. F IF , VGIN = 0.2 V, F BB = 1 MHz, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°CRev. A | Page 13 of 28BASEBAND FREQUENCY (MHz)V G A A N D M I X E R I N P U T I I P 3 (d B m ) (r e 200Ω)100202226242830323040506070809010003678-024Figure 24. IIP3 vs. F BB , VGIN = 1.2 V, F IF = 380 MHz, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°C BASEBAND FREQUENCY (MHz)V G A A N D M I X E R I N P U T I I P 3 (d B m ) (r e 200Ω)10020–20–15–10–53040506070809010003678-025Figure 25. IIP3 vs. F BB , VGIN = 0.2 V, F IF = 380 MHz, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°C IF FREQUENCY (MHz)N O I S E F I G U R E (d B )15050250891011121314151635045055065075085095003678-026Figure 26. Noise Figure vs. F IF , T = 25°C, VGIN = 0.2 V, F BB = 1 MHzVGIN (V)N O I S E F I G U R E (d B )I N P U T I I P 3 (d B m ) (r e 200Ω)0.20.30.4015105302520454035–1050–51510353025200.50.60.70.80.9 1.0 1.11.203678-027NFIIP3Figure 27. Noise Figure and IIP3 vs. VGIN, Temperature = 25°C,F IF = 380 MHz, F BB = 1 MHz, V POS = 2.7 VVGIN (V)N O I S E F I G U R E (d B )I N P U T I I P 3 (d B m ) (r e 200Ω)0.20.30.40151053025204035–1050–51510353025200.50.60.70.80.9 1.0 1.11.203678-028NFIIP3Figure 28. Noise Figure and IIP3 vs. VGIN, Temperature = 25°C,F IF = 380 MHz, F BB = 1 MHz, V POS = 5 VLO INPUT LEVEL (V)N O I S E F I G U R E (d B )P H A S E E R R OR (D e g r e e s )–12–108111091413121615–2.0–0.5–1.0–1.502.01.51.00.5–8–6–4–203678-029Figure 29. Noise Figure and Quadrature Phase Error IMXO/QMXO vs. LO InputLevel, Temperature = 25°C, VGIN = 0.2 V, V POS = 5 V for F IF = 50 MHz,380 MHz, and 900 MHzRev. A | Page 14 of 28DEMODULATOR USING MXIP AND MXINIF FREQUENCY (MHz)M I X E R G A I N (d B )1002008.58.010.09.59.011.010.5300400500600700800900100003678-030Figure 30. Mixer Gain vs. F IF , V POS = 2.7 V, 5 V, F BB = 1 MHz,Temperature = −40°C, +25°C, +85°CIF FREQUENCY (MHz)M I X E R I N P U T P 1d B (d B m ) (r e 200Ω)100200–8.0–6.5–7.0–7.5–3.0–2.5–2.0–3.5–4.0–4.5–5.0–5.5–6.0–1.5300400500600700800900100003678-031Figure 31. Input 1 dB Compression Point vs. F IF , F BB = 1 MHz, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°CIF FREQUENCY (MHz)I N P U T I I P 3 (d B m ) (r e 200Ω)50150101421.01312111716151825035045055065075085095003670-032N O I S E F I G U R E (d B )19.020.520.019.523.022.522.021.5Figure 32. IIP3 and Noise Figure vs. F IF , V POS = 2.7 V, 5 V, Temperature = 25°CRev. A | Page 15 of 28FINAL BASEBAND AMPLIFIERSBASEBAND FREQUENCY (MHz)G A I N (d B )0.1141317161520191821110100100003678-033Figure 33. Gain vs. F BB , V VCMO = VREF = 1 V, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°C BASEBAND FREQUENCY (MHz)O P 1d B (d B V )0.1–15–20–10–55110100100003678-034Figure 34. OP1dB Compression vs. F BB , V VCMO = VREF = 1 V, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°CBASEBAND FREQUENCY (MHz)O I P 3 (d B V )10–101015202530–15–505355070903013011015017019003678-035Figure 35. OIP3 vs. F BB , V VCMO = VREF = 1 V, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°CFREQUENCY (kHz)11010010001000010000003678-036Figure 36. Noise Spectral DensityRev. A | Page 16 of 28VGA/DEMODULATOR AND BASEBAND AMPLIFIERIF FREQUENCY (MHz)Q U A D R A T U R E P H A S E E R R O R (D e g r e e s )100–1.50.51.01.5–2.0–1.0–0.52.0200300400500600700800900100003678-037Figure 37. Quadrature Phase Error vs. F IF , VGIN = 0.7 V, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°CBASEBAND FREQUENCY (MHz)Q U A D R A T U R E P H A S E E R R O R (D e g r e e s )–1.50.51.01.5–2.0–1.0–0.52.0501015202530354003678-038Figure 38. Quadrature Phase Error vs. F BB , VGIN = 0.7 V, V POS = 2.7 V, 5 V,Temperature = −40°C, +25°C, +85°C, F IF = 380 MHzBASEBAND FREQUENCY (MHz)I /QA M P L I T U D E M I S M A T C H (dB )–0.4–0.20.20.451015202530354003678-039Figure 39. I/Q Amplitude Imbalance vs. F BB , Temperature = 25°C, V POS = 5 VIF FREQUENCY (MHz)I /Q A M PL I T U D E M I S M A T C H (d B )–1.500.51.01.5–2.0–1.0–0.52.020*******400500600700800900100003678-040Figure 40. I/Q Amplitude Imbalance vs. F IF , Temperature = 25°C, V POS = 5 VIF FREQUENCY (MHz)S H U N T R E S I S T A N C E (Ω)S H U N T C A P A C I T A N C E (p F )501502501001601401202202001803002802602400.20.80.60.41.41.21.02.22.01.81.635045055065075085095003678-041Figure 41. Input Impedance of IF Input vs. F IF , VGIN = 0.7 V, V POS = 5 V03678-042Figure 42. S11 of IF Input vs. F IF , F IF = 50 MHz to 1 GHz, VGIN = 0.7 V,V POS = 5 V (with L Pad, with No Pad, Normalized to 50 Ω)。

混频器AD部分

(五)设计过程Altium Designer篇1.1原理图新建pcb项目。

在PCB中建立原理图文件和pcb文件图(4.1)新建项目1.2添加和使用库具体步骤:File>New>Project>Integrated Library,即可新建一个集成库新建原理图库File>New>Library>Schematic Library,即可新建一个原理图库新建PCB库File>New>Library>PCB Library,即可新建一个PCB库保存以上三个新建的库:右键单击新建的库,选择保存,即可图(4.2)新建原理图库实验元件清单AD835下面是AD835的原理图库图(4.3)AD835原理图库1.3建立完原理图库记住保存,方便调用先选择一个元件库,再点place xxx 拖动到原理图(4.4)新建的库以schlib开头的库,包括:schlib排线,schli接口,schlib res ,schlib151,schlib1,schlib2图(4.5)从自制的schlib1库调用741381.4原理图的连接图(4.6)摆放元件由于我们所做的混频器是承接上一个实验的输出作为我们的输入,所以需要制作上下变频。

图(4.7)AD835外部电路如5.7所示,该部分为AD835的外部电路,组成了混频器中的乘法器部分,作用是混合两个输入信号,从而输出所需要的信号。

图(4.8)上变频电路如图(5.8)所示,该电路由电感,电容,电阻组成,构成带通滤波器,起到了上变频的作用。

图(4.9)下变频电路如图(5.9)所示,该电路由电感,电容,电阻组成,构成带通滤波器,起到了下变频的作用。

图(4.10)连接元器件P1~P10为排针。

其中包括了VCC,接地,输入及输出,其余原件为图(5.7)(5.8)(5.9)的组合。

AD835 的五管脚为输出,接入两个带通滤波器的输入端。

1.5元件的封装原理图库中绘制自制元件后完成封装,图(4.11)自制AD835原理图库下面进项PCB封装图(4.12)建立PCB元件库图(4.13)PCB元件库打开图(4.12)即得到图(4.13)所示界面。

AD734模拟乘法器的原理与应用

AD734模拟乘法器的原理与应用作者:龙侃彭玉涛蒋熔罗超来源:《价值工程》2011年第18期摘要: AD734是一款高速精密四象限模拟乘法器,典型静态满量程误差仅为0.1%,它提供对分母的直接精确控制,这是模拟乘法器的一个新特点。

本文主要介绍了AD734的内部结构框图,分母控制电路,最后给出了AD734应用于乘法运算中的电路图。

Abstract: The AD734 is an accurate high speed, four-quadrant analog multiplier, Total static error is only 0.1% of full scale. It provide the direct control for the denominator which is a new feature of analog multiplier. The inner block diagram and the denominator control circuitry of AD734 are mainly introduced, at last, the applications of AD734 as a multiplier and a divider are showed in circuit diagram.关键词: AD734;分母直接控制;乘法器Key words: AD734;direct control of the denominator;multiplier中图分类号:TP322+.2 文献标识码:A文章编号:1006-4311(2011)18-0141-011概述乘法器在模拟信号处理中应用广泛,它可以完成模拟信号的乘除运算,对信号进行调制解调,还广泛应用于锁相环、混频器等电路当中。

AD734是AD公司生产的一款高速度高精度四象限模拟乘法器,输入输出信号的峰-峰值可达20V,带宽为10MHz,包括放大倍数误差、偏置和非线性误差在内的总误差仅为0.1%,输出信号变形小于-80dBc,在大多数应用中几乎不用外接任何元件。

ADS8364 与TMS320LF2407 的接口及应用

电力系统配网自动化是一个庞大、复杂、综合性的系统工程,如何将配电网在正常及事故情况下的监测、保护、控制有机地融合在一起,提高供电质量,是电力系统微机保护的一个重要课题;而对配电网的电压、电流参数进行快速、准确地采集,及时反映配电网的故障状态并进行相应处理,是配电系统微机保护的首要任务。

使用美国德州仪器公司(TI)推出的ADS8364 A/D芯片与TMS320LF2407DSP芯片构成控制系统是一个较好的解决方案,现已将其成功应用到配电网中。

本文在简介ADS8364和TMS320LF2407的功能、性能和特点的基础上,介绍ADS83 64与TMS320LF2407的硬件接口电路和软件编程方法。

1 ADS8364介绍[1]ADS8364是TI公司推出的专为高速同步数据采集系统设计的高速、低功耗、6通道同步采样的16位A/D转换芯片,共有64个引脚,大致可以分为两类,各引脚功能如表1所示。

ADS8364有6个模拟输入通道,分为A、B、C三组,每组包括2个通道,启动A/D转换。

模拟量的输入采用差分方式,可以抑制共模干扰。

模拟电源为单+5 V供电,将ADS8364的REFin和REFout引脚接到一起可以输出+2.5V的参考电压提供给差分电路。

ADS8364的时钟信号由外部提供,转换时间为20个时钟周期,最高频率为5MHz,在5MHz的时钟频率下ADS8364转换时间为3.2μs,相应的数据采集时间为0.8μs,每个通道的总的转换时间为4μs,A/D转换完成后产生转换结束信号数字电源供电电压为3V~5V,即可以与3.3V供电的微控制器接口,也可以与5V供电的微控制器接口。

A/D转换结果为16位,最高位为符号位,数据输出方式很灵活,分别由BYTE、ADD与地址线A2A1A0的组合控制,如表2所示。

从表2中可以看出,转换结果的读取方式有三种:直接读取、循环读取和FIFO方式。

根据BYTE为0或者为1可确定每次读取时得到的数据位数,根据ADD为0或者为1可确定第一次读取的是通道地址信息还是通道A/D转换结果。

5毕业设计说明书_单片机AdμC834完整的数据采集系统芯片

前言ADμC834是一种真正意义上的完整的数据采集系统芯片。

这种崭新的微处理转换器和先进的混合信号处理工艺显著提高了数据采集系统的性能,并大幅度减少了应用系统的开发时间和成本。

ADμC834是美国模拟器件(AD)公司最新(2003年前)投入市场的一款微处理转换器产品,它集成了双路∑—△型ADC、温度传感器、增益可程控放大器(PGA)、8位51MCU、62k的可编程程序EEPROM、4k的数据Flash Memory、2304字节的片内RAM、12位DAC以及定时器、I2C兼容的SPI和标准的串行I/O等。

由此可见,ADμC834本身就是一个内嵌MCU 的高性能数据采集系统。

ADμC834内部集成了两路独立的∑—△ADC,其中主通道ADC为24位,辅助通道ADC为16位。

两个独立的ADC通道由于使用了数字滤波,因而可以实现宽动态范围的低频信号测量,非常适用于称重仪、张力应变仪、压力转换器和温度测量等方面的应用。

其中主通道的AD输入范围在±20mV~±2.56V之间分为8档,使用时可任选一档。

由于使用了∑—△转换技术,因此可以实现高达24位无丢失码性能,且辅助通道还可以作为温度传感器使用。

ADμC834利用32kHz晶振来驱动片内锁相环(PLL)以产生内部所需要的工作频率,它的微控制器内核与8051兼容。

片内外围设备包括一个与SPI和I2C兼容的串行端口、多路数字输入/输出端口、看门狗定时器、电源监视器以及时间间隔计数器。

同时片内还提供了62kB闪速/电擦除程序存储器以及2304字节的片内RAM。

ADμC834本身能提供程序串行下载,所以可以直接下载调试程序,非常方便于程序的开发和设计。

对于已经掌握了51系列单片机的用户,可以轻而易举的掌握ADμC834位转换器的开发应用技术,但要注意ADμC834微转换器与8051的若干不同之处。

而对于没有接触过单片机的用户,由于ADμC834微转换器所具有的在线下载/调试/编程的功能,把ADμC834作为学习单片机或微控制器的入门,是一种上佳选择。

低失真有源混频器AD831的工作原理及应用

低失真有源混频器AD831的工作原理及应用类别:无线通信作者:空军雷达学院杨加功石雄彭世蕤来源:《国外电子元器件》摘要:AD831是美国AD公司生产的单片低失真混频器,它采用双差分模拟乘法器混频电路。

文中介绍了AD831的工作原理、内部电路、引脚排列及功能说明,最后给出了AD831在频踪式雷达本振中的应用电路。

关键词:混频器射频本振中频 AD831混频器在广播、通信、电视等外差式设备及频率合成设备中具有广泛的应用,它是用来进行信号频率变换并可保持调制性质不变的电路组件,其性能对整个系统有着足轻得的作用。

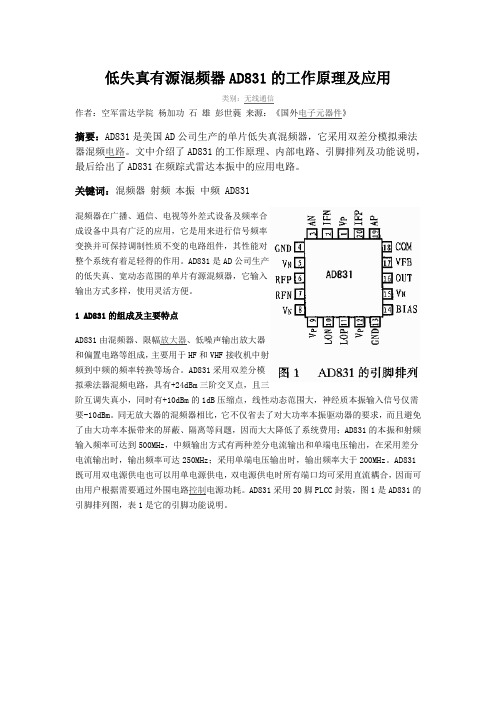

AD831是AD公司生产的低失真、宽动态范围的单片有源混频器,它输入输出方式多样,使用灵活方便。

1 AD831的组成及主要特点AD831由混频器、限幅放大器、低噪声输出放大器和偏置电路等组成,主要用于HF和VHF接收机中射频到中频的频率转换等场合。

AD831采用双差分模拟乘法器混频电路,具有+24dBm三阶交叉点,且三阶互调失真小,同时有+10dBm的1dB压缩点,线性动态范围大,神经质本振输入信号仅需要-10dBm。

同无放大器的混频器相比,它不仅省去了对大功率本振驱动器的要求,而且避免了由大功率本振带来的屏蔽、隔离等问题,因而大大降低了系统费用;AD831的本振和射频输入频率可达到500MHz,中频输出方式有两种差分电流输出和单端电压输出,在采用差分电流输出时,输出频率可达250MHz;采用单端电压输出时,输出频率大于200MHz。

AD831既可用双电源供电也可以用单电源供电,双电源供电时所有端口均可采用直流耦合,因而可由用户根据需要通过外围电路控制电源功耗。

AD831采用20脚PLCC封装,图1是AD831的引脚排列图,表1是它的引脚功能说明。

表1 AD831的引脚功能说明混频原所示是部电路框图。

图中,频频输入信号加到晶体管Q1、Q2的基极,由于电阻R1、R2的负反馈潮作用,因而差分电流射频信号的幅度成线性关系。

ADuC834BSZ资料

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

8051-BASED MCU WITH ADDITIONAL PERIPHERALS 62 KBYTES FLASH/EE PROGRAM MEMORY 4 KBYTES FLASH/EE DATA MEMORY 2304 BYTES USER RAM

RESET DVDD DGND POR PLL AND PROG CLOCK DIV OSC WAKE- UP/ RTC TIMER

3 ؋ 16 BIT TIMERS BAUD R ATE TIMER 4 ؋ PARALLEL PORTS

POWER SUPPLY MON WATCHDOG TIMER UART, SPI, AND I2C SERIAL I/O

IPTION

模拟乘法器调幅实验报告

模拟乘法器调幅实验报告模拟乘法器调幅实验报告引言:调幅(Amplitude Modulation, AM)是一种常用的调制技术,广泛应用于无线通信、广播电视等领域。

在调幅技术中,模拟乘法器是一个关键的组件,它能够实现信号的调幅处理。

本实验旨在通过搭建模拟乘法器电路,深入了解调幅原理,并通过实验验证其效果。

一、实验目的通过搭建模拟乘法器电路,掌握调幅原理,并验证其调幅效果。

二、实验原理调幅是通过将调制信号与载波信号相乘,实现信号的幅度调制。

模拟乘法器是实现这一功能的关键元件。

在本实验中,我们采用二极管作为模拟乘法器的核心元件。

当二极管正向偏置时,其电流与输入电压成正比。

将调制信号与载波信号输入到二极管的正向偏置端,通过电流与电压的乘积,实现信号的幅度调制。

三、实验器材和仪器1. 信号发生器:提供调制信号和载波信号。

2. 二极管:作为模拟乘法器的核心元件。

3. 示波器:用于观察输出信号的波形。

四、实验步骤1. 搭建电路:将信号发生器的调制信号输出与载波信号输出分别连接到二极管的正向偏置端,将二极管的反向端接地。

将二极管的输出端连接到示波器,观察输出信号的波形。

2. 调节信号发生器:分别调节调制信号和载波信号的频率、幅度和相位,观察输出信号的变化。

3. 记录实验数据:记录不同调制信号和载波信号参数下的输出信号波形和幅度。

五、实验结果与分析在实验中,我们通过调节信号发生器的调制信号和载波信号的频率、幅度和相位,观察了输出信号的变化。

实验结果显示,当调制信号的频率与载波信号的频率相等时,输出信号呈现出明显的幅度调制效果。

当调制信号的幅度增大时,输出信号的幅度也相应增大。

当调制信号的相位与载波信号的相位相差90度时,输出信号的幅度最大,表现出最明显的幅度调制效果。

通过实验结果的分析,我们可以得出以下结论:1. 调制信号的频率与载波信号的频率相等时,能够实现明显的幅度调制效果。

2. 调制信号的幅度与输出信号的幅度成正比,调制信号的幅度增大时,输出信号的幅度也相应增大。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ad834乘法器电路

AD834是一款高性能乘法器电路芯片,广泛应用于射频(RF)

和微波领域。

它使用先进的集成电路技术,能够实现高精度的模拟

乘法功能。

下面我将从不同角度来介绍AD834乘法器电路。

1. 基本原理:

AD834乘法器电路的基本原理是利用四象限乘法器实现信号的

乘法运算。

它接受两个输入信号,分别称为X和Y,经过乘法运算

后输出结果为Z。

乘法器的原理是将输入信号X和Y进行乘法运算,得到的结果与输入信号的幅度和相位相关。

2. 工作频率范围:

AD834乘法器电路适用于宽频带的应用,其工作频率范围通常

在几百MHz到几GHz之间。

这使得它在射频和微波系统中能够处理

高频信号,并实现频率转换、调制解调、幅度调制等功能。

3. 电路结构:

AD834乘法器电路采用集成电路技术,通常由多个功能模块组成。

其中包括输入缓冲放大器、四象限乘法器、输出缓冲放大器等。

这些模块相互配合,实现了高性能的乘法运算。

4. 特点和性能:

AD834乘法器电路具有以下特点和性能:

高线性度,能够实现高精度的乘法运算,输出结果与输入信号

的幅度和相位关系准确。

宽动态范围,能够处理大幅度的输入信号,适用于各种信号强

度情况。

低功耗,采用低功耗设计,适合用于电池供电或功耗敏感的应用。

高速响应,能够快速响应输入信号的变化,适用于高速数据处

理和调制解调等应用。

5. 应用领域:

AD834乘法器电路广泛应用于射频和微波系统中,包括无线通信、卫星通信、雷达、无线电广播、电视、航空航天等领域。

它在

这些领域中扮演着重要的角色,实现了信号处理、频率转换、调制

解调等功能。

总结:

AD834乘法器电路是一款高性能的乘法器芯片,具有高线性度、宽动态范围、低功耗和高速响应等特点。

它在射频和微波系统中应

用广泛,能够实现信号的乘法运算,并在无线通信、雷达、电视等

领域中发挥重要作用。