verilog 乘法运算转换

verilog简单乘法器

verilog简单乘法器Verilog简单乘法器Verilog是一种硬件描述语言,用于描述数字系统的行为。

在数字电路设计中,乘法器是一个常见的电路组件,它用于执行乘法运算。

本文将介绍一个简单的Verilog乘法器的设计与实现。

乘法器是一种数字电路,用于计算两个数的乘积。

它接收两个输入数,将它们相乘得到一个输出。

在本文中,我们将实现一个4位乘法器,即输入和输出都是4位的二进制数。

我们需要定义输入和输出端口。

在Verilog中,我们可以使用“input”和“output”关键字来声明端口。

对于4位乘法器,我们可以声明两个4位的输入端口A和B,以及一个8位的输出端口P。

module simple_multiplier(input [3:0] A,input [3:0] B,output [7:0] P);接下来,我们需要实现乘法器的功能。

乘法器的实现可以通过多次执行加法运算来实现。

具体地,我们可以将输入的两个4位数逐位相乘,然后将得到的部分乘积相加得到最终的乘积。

在Verilog中,我们可以使用“assign”关键字来执行赋值操作。

我们可以定义一些临时变量,用于存储部分乘积和最终乘积的结果。

然后,通过多次执行加法运算,将部分乘积相加得到最终乘积。

下面是一个实现4位乘法器的简单示例代码:reg [7:0] temp;reg [7:0] result;always @(*) begintemp = A[0] * B;result = temp;temp = A[1] * B;result = result + (temp << 1);temp = A[2] * B;result = result + (temp << 2);temp = A[3] * B;result = result + (temp << 3);endassign P = result;在上述代码中,我们使用了一个“always”块来执行乘法器的功能。

verilog代码乘法除法编写

Verilog代码乘法除法1. 引言Verilog是一种硬件描述语言,用于设计和建模数字电路。

在数字电路中,乘法和除法是常见的运算操作。

本文将介绍如何使用Verilog编写乘法和除法的代码,并提供一些示例来帮助读者更好地理解。

2. 乘法2.1 基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在数字电路中,我们可以使用逻辑门和触发器来实现乘法运算。

2.2 Verilog代码示例下面是一个简单的Verilog代码示例,用于实现两个8位无符号整数的乘法运算:module multiplier (input [7:0] a,input [7:0] b,output reg [15:0] result);always @(*) beginresult = a * b;endendmodule上述代码定义了一个名为multiplier的模块,该模块有两个输入端口a和b,以及一个输出端口result。

在always @(*)块中,我们使用乘法操作符将输入端口a和b相乘,并将结果存储在输出端口result中。

2.3 测试与验证为了测试上述的乘法模块,我们可以编写一个测试台,输入一些测试用例,并验证输出结果是否正确。

module multiplier_test;reg [7:0] a;reg [7:0] b;wire [15:0] result;multiplier dut(.a(a),.b(b),.result(result));initial begin// Test case 1: a = 5, b = 3a = 5;b = 3;#10; // Wait for 10 time unitsif (result !== 15)$display("Test case 1 failed");// Test case 2: a = 10, b = 0a = 10;b = 0;#10; // Wait for 10 time unitsif (result !== 0)$display("Test case 2 failed");// Add more test cases here...endendmodule上述代码定义了一个名为multiplier_test的测试台模块。

乘法器的verilog实现(并行、移位相加、查找表)

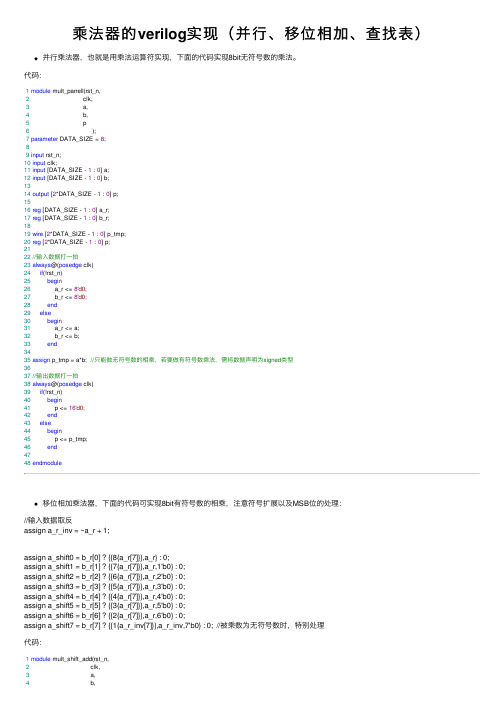

乘法器的verilog实现(并⾏、移位相加、查找表)并⾏乘法器,也就是⽤乘法运算符实现,下⾯的代码实现8bit⽆符号数的乘法。

代码:1module mult_parrell(rst_n,2 clk,3 a,4 b,5 p6 );7parameter DATA_SIZE = 8;89input rst_n;10input clk;11input [DATA_SIZE - 1 : 0] a;12input [DATA_SIZE - 1 : 0] b;1314output [2*DATA_SIZE - 1 : 0] p;1516reg [DATA_SIZE - 1 : 0] a_r;17reg [DATA_SIZE - 1 : 0] b_r;1819wire [2*DATA_SIZE - 1 : 0] p_tmp;20reg [2*DATA_SIZE - 1 : 0] p;2122//输⼊数据打⼀拍23always@(posedge clk)24if(!rst_n)25begin26 a_r <= 8'd0;27 b_r <= 8'd0;28end29else30begin31 a_r <= a;32 b_r <= b;33end3435assign p_tmp = a*b; //只能做⽆符号数的相乘,若要做有符号数乘法,需将数据声明为signed类型3637//输出数据打⼀拍38always@(posedge clk)39if(!rst_n)40begin41 p <= 16'd0;42end43else44begin45 p <= p_tmp;46end4748endmodule移位相加乘法器,下⾯的代码可实现8bit有符号数的相乘,注意符号扩展以及MSB位的处理://输⼊数据取反assign a_r_inv = ~a_r + 1;assign a_shift0 = b_r[0] ? {{8{a_r[7]}},a_r} : 0;assign a_shift1 = b_r[1] ? {{7{a_r[7]}},a_r,1'b0} : 0;assign a_shift2 = b_r[2] ? {{6{a_r[7]}},a_r,2'b0} : 0;assign a_shift3 = b_r[3] ? {{5{a_r[7]}},a_r,3'b0} : 0;assign a_shift4 = b_r[4] ? {{4{a_r[7]}},a_r,4'b0} : 0;assign a_shift5 = b_r[5] ? {{3{a_r[7]}},a_r,5'b0} : 0;assign a_shift6 = b_r[6] ? {{2{a_r[7]}},a_r,6'b0} : 0;assign a_shift7 = b_r[7] ? {{1{a_r_inv[7]}},a_r_inv,7'b0} : 0; //被乘数为⽆符号数时,特别处理代码:1module mult_shift_add(rst_n,2 clk,3 a,4 b,5 p6 );7parameter DATA_SIZE = 8;89input rst_n;10input clk;11input [DATA_SIZE - 1 : 0] a;12input [DATA_SIZE - 1 : 0] b;1314output [2*DATA_SIZE - 2 : 0] p;1516//输⼊数据打⼀个时钟节拍17reg [DATA_SIZE - 1 : 0] a_r;18reg [DATA_SIZE - 1 : 0] b_r;1920//输⼊数据取反21wire [DATA_SIZE - 1 : 0] a_r_inv;2223//输⼊数据移位24wire [2*DATA_SIZE - 1 : 0] a_shift0;25wire [2*DATA_SIZE - 1 : 0] a_shift1;26wire [2*DATA_SIZE - 1 : 0] a_shift2;27wire [2*DATA_SIZE - 1 : 0] a_shift3;28wire [2*DATA_SIZE - 1 : 0] a_shift4;29wire [2*DATA_SIZE - 1 : 0] a_shift5;30wire [2*DATA_SIZE - 1 : 0] a_shift6;31wire [2*DATA_SIZE - 1 : 0] a_shift7;3233//输出数据打⼀个时钟节拍34wire [2*DATA_SIZE - 1 : 0] p_tmp;35reg [2*DATA_SIZE - 1 : 0] p;3637//输⼊数据打⼀个时钟节拍38always@(posedge clk)39if(!rst_n)40begin41 a_r <= 8'd0;42 b_r <= 8'd0;43end44else45begin46 a_r <= a;47 b_r <= b;48end49//输⼊数据取反50assign a_r_inv = ~a_r + 1;5152//输⼊数据移位,注意符号扩展,不仅仅是最⾼位扩展53//对每⼀个bit都需扩展54assign a_shift0 = b_r[0] ? {{8{a_r[7]}},a_r} : 0;55assign a_shift1 = b_r[1] ? {{7{a_r[7]}},a_r,1'b0} : 0;56assign a_shift2 = b_r[2] ? {{6{a_r[7]}},a_r,2'b0} : 0;57assign a_shift3 = b_r[3] ? {{5{a_r[7]}},a_r,3'b0} : 0;58assign a_shift4 = b_r[4] ? {{4{a_r[7]}},a_r,4'b0} : 0;59assign a_shift5 = b_r[5] ? {{3{a_r[7]}},a_r,5'b0} : 0;60assign a_shift6 = b_r[6] ? {{2{a_r[7]}},a_r,6'b0} : 0;61assign a_shift7 = b_r[7] ? {{1{a_r_inv[7]}},a_r_inv,7'b0} : 0; //被乘数为⽆符号数时,特别处理6263assign p_tmp = a_shift0 + a_shift1 + a_shift2 + a_shift3 + a_shift464 + a_shift5 + a_shift6 + a_shift7;6566always@(posedge clk)67if(!rst_n)68begin69//p <= 16'd0;70 p <= 15'd0;71end72else73begin74//p <= p_tmp[15:0];75 p <= p_tmp[14:0];76end7778endmoduletestbench:1module mult_shift_add_tb;23// Inputs4reg rst_n;5reg clk;6reg [7:0] a;7reg [7:0] b;89// Outputs10wire [14:0] p;1112// Instantiate the Unit Under Test (UUT)13 mult_shift_add uut (14 .rst_n(rst_n),15 .clk(clk),16 .a(a),17 .b(b),18 .p(p)19 );2021parameter CLK_PERIOD = 10;2223initial begin24 rst_n = 0;25 clk = 0;2627 #100;28 rst_n = 1;29end3031always #(CLK_PERIOD/2) clk = ~clk;3233always@(posedge clk)34if(!rst_n)35begin36 a = 8'd0;37 b = 8'd0;38end39else40begin41 a = a + 1;42 b = b - 1;43end4445endmoduleISIM仿真结果:移位相加乘法器树:将assign p_tmp = a_shift0 + a_shift1 + a_shift2 + a_shift3 + a_shift4 + a_shift5 + a_shift6 + a_shift7;换为:assign sum_01 = a_shift0 + a_shift1;assign sum_23 = a_shift2 + a_shift3;assign sum_45 = a_shift4 + a_shift5;assign sum_67 = a_shift6 + a_shift7;assign sum_0123 = sum_01 + sum_23;assign sum_4567 = sum_45 + sum_67;assign p_tmp = sum_0123 + sum_4567;就成为乘法器树。

verilog 乘法 除法

verilog 乘法除法摘要:一、引言二、Verilog 简介三、Verilog 乘法模块设计1.点乘法2.阵列乘法四、Verilog 除法模块设计1.循环除法2.快速除法五、Verilog 乘除法模块的应用六、总结正文:一、引言Verilog 是一种硬件描述语言,广泛应用于数字电路设计领域。

在数字电路设计中,乘法和除法是基本的运算操作。

本文将详细介绍如何使用Verilog 实现乘法和除法功能。

二、Verilog 简介Verilog 是一种基于文本的硬件描述语言,用于描述数字电路和模拟混合信号电路。

Verilog 具有简洁、清晰的语法结构,易于学习和使用。

通过Verilog 描述的电路可以被仿真和验证,确保设计正确性。

1.点乘法点乘法是两个数相乘的简单运算。

在Verilog 中,可以使用assign 语句实现点乘法。

例如:```verilogmodule multiplier(input [15:0] a, b, output [31:0] result);assign result = a * b;endmodule```2.阵列乘法阵列乘法是实现多个数相乘的操作。

在Verilog 中,可以使用for 循环和循环阵列实现阵列乘法。

例如:```verilogmodule multiplier_array(input [15:0] a, b, output [31:0] result);reg [15:0] temp_result [15:0];integer i;for (i = 0; i < 16; i = i + 1)temp_result[i] = a * b[i];assign result = temp_result[15] + temp_result[14] + ...+temp_result[0];endmodule```1.循环除法循环除法是一种简单的除法实现方法,通过不断减去除数和更新商来实现。

verilog有符号数和无符号数乘法运算

verilog有符号数和无符号数乘法运算Verilog有符号数和无符号数乘法运算在Verilog中,有符号数和无符号数乘法运算是非常重要的概念。

它们在数字电路设计和硬件描述语言中起着至关重要的作用。

在本文中,我们将深入探讨有符号数和无符号数乘法运算的原理、应用和区别,以便读者深入理解这一主题。

1. 有符号数和无符号数的定义在Verilog中,有符号数和无符号数是两种不同的数据类型。

无符号数是指仅由非负数组成的数字,而有符号数是指包含正负号的数字。

在硬件设计中,我们经常会遇到这两种类型的数据,并需要对它们进行不同的处理。

2. 有符号数和无符号数的乘法原理在Verilog中,有符号数和无符号数的乘法运算原理是有所不同的。

对于无符号数,乘法运算可以直接按照普通的乘法规则进行,即将两个数相乘得到结果。

而对于有符号数,由于需要考虑正负号的影响,乘法运算则需要根据补码或原码进行相应的转换和处理。

3. 有符号数和无符号数乘法运算的应用在数字电路设计中,有符号数和无符号数的乘法运算被广泛应用于各种计算单元和逻辑电路中。

它们可以用于实现乘法器、数据处理器和信号处理器等功能模块,为数字系统的运算提供强大的支持。

4. 有符号数和无符号数乘法运算的区别有符号数和无符号数的乘法运算在应用上有一些明显的区别。

在进行乘法运算时,需要考虑有符号数的溢出和符号位的处理,而无符号数则不需要。

在逻辑电路设计中,有符号数和无符号数的乘法运算通常需要采用不同的电路结构和算法来实现。

5. 个人观点和理解在我看来,有符号数和无符号数的乘法运算是数字电路设计中非常重要的问题。

它们不仅涉及到硬件描述语言的应用,也涉及到数字系统的实际运算。

深入理解和掌握有符号数和无符号数乘法运算的原理和实现方法,对于提高数字电路设计的水平和能力是非常有益的。

总结回顾通过本文的探讨,我们对Verilog中有符号数和无符号数乘法运算有了更深入的理解。

我们深入分析了它们的原理、应用和区别,也分享了个人的观点和理解。

状态机verilog乘法器实验结果讨论

状态机verilog乘法器实验结果讨论

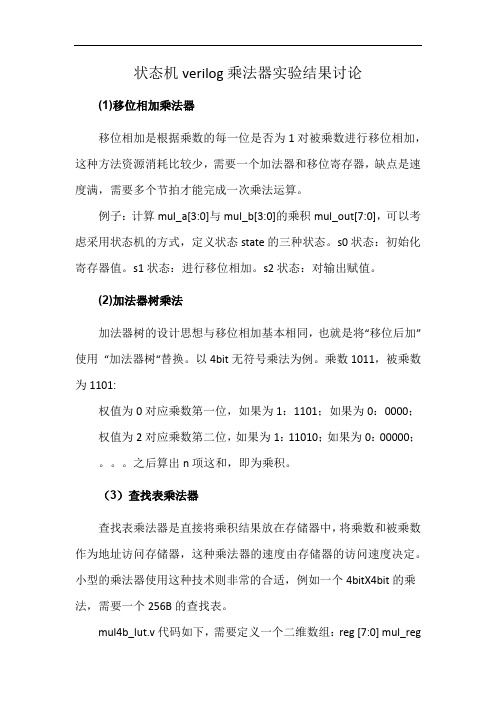

(1)移位相加乘法器

移位相加是根据乘数的每一位是否为1对被乘数进行移位相加,这种方法资源消耗比较少,需要一个加法器和移位寄存器,缺点是速度满,需要多个节拍才能完成一次乘法运算。

例子:计算mul_a[3:0]与mul_b[3:0]的乘积mul_out[7:0],可以考虑采用状态机的方式,定义状态state的三种状态。

s0状态:初始化寄存器值。

s1状态:进行移位相加。

s2状态:对输出赋值。

(2)加法器树乘法

加法器树的设计思想与移位相加基本相同,也就是将“移位后加” 使用“加法器树“替换。

以4bit无符号乘法为例。

乘数1011,被乘数为1101:

权值为0对应乘数第一位,如果为1:1101;如果为0:0000;

权值为2对应乘数第二位,如果为1:11010;如果为0:00000;。

之后算出n项这和,即为乘积。

(3)查找表乘法器

查找表乘法器是直接将乘积结果放在存储器中,将乘数和被乘数作为地址访问存储器,这种乘法器的速度由存储器的访问速度决定。

小型的乘法器使用这种技术则非常的合适,例如一个4bitX4bit的乘法,需要一个256B的查找表。

mul4b_lut.v代码如下,需要定义一个二维数组:reg [7:0] mul_reg

[255:0],然后以乘数mul_a和mul_b作为地址,初始化阶段写入乘积值mul_in,之后再读出对应乘数和被乘数的乘积结果即可。

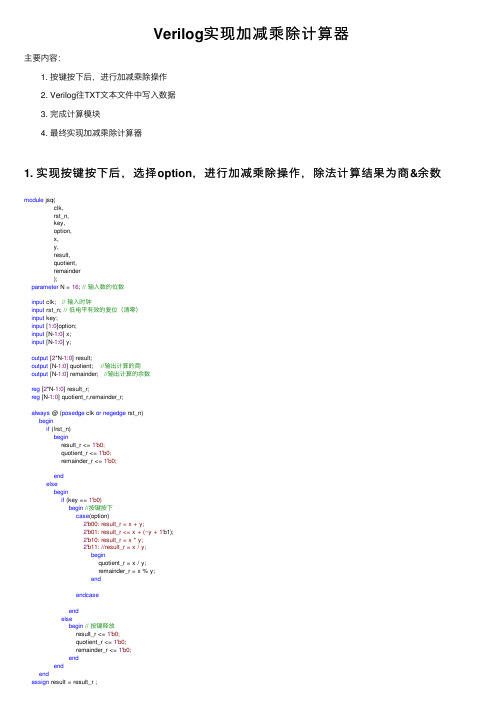

Verilog实现加减乘除计算器

Verilog实现加减乘除计算器主要内容: 1. 按键按下后,进⾏加减乘除操作 2. Verilog往TXT⽂本⽂件中写⼊数据 3. 完成计算模块 4. 最终实现加减乘除计算器1. 实现按键按下后,选择option,进⾏加减乘除操作,除法计算结果为商&余数module jsq(clk,rst_n,key,option,x,y,result,quotient,remainder);parameter N = 16; // 输⼊数的位数input clk; // 输⼊时钟input rst_n; // 低电平有效的复位(清零)input key;input [1:0]option;input [N-1:0] x;input [N-1:0] y;output [2*N-1:0] result;output [N-1:0] quotient; //输出计算的商output [N-1:0] remainder; //输出计算的余数reg [2*N-1:0] result_r;reg [N-1:0] quotient_r,remainder_r;always @ (posedge clk or negedge rst_n)beginif (!rst_n)beginresult_r <= 1'b0;quotient_r <= 1'b0;remainder_r <= 1'b0;endelsebeginif (key == 1'b0)begin//按键按下case(option)2'b00: result_r = x + y;2'b01: result_r <= x + (~y + 1'b1);2'b10: result_r = x * y;2'b11: //result_r = x / y;beginquotient_r = x / y;remainder_r = x % y;endendcaseendelsebegin// 按键释放result_r <= 1'b0;quotient_r <= 1'b0;remainder_r <= 1'b0;endendendassign result = result_r ;assign quotient= quotient_r;assign remainder = remainder_r;endmoduleView Code`timescale 1ns/1ps`define clock_period 20module jsq_tb;reg clk;reg rst_n;reg key;reg [1:0]option;reg [15:0] x,y;wire [31:0] result;wire [15:0] quotient;wire [15:0] remainder;initial beginclk = 1'b1;rst_n = 1'b0;key = 1'b1; // 复位时,按键释放# 20//复位20nsrst_n = 1'b1;# 20key = 1'b0;option = 2'b10;# 100key = 1'b1;# 20key = 1'b0;option = 2'b11;# 100// key = 1'b1;// # 20$stop;endalways #(`clock_period/2) clk = ~clk; //50Mjsq #(.N(16)) jsq_0(.clk(clk),.rst_n(rst_n),.key(key),.option(option),.x(x),.y(y),.result(result),.quotient(quotient),.remainder(remainder));initial beginx = 0;repeat(20)#(`clock_period) x = {$random}%100; //通过位拼接操作{}产⽣0—59范围的随机数endinitial beginy = 0;repeat(20)#(`clock_period) y = {$random}%50;end/*integer i;initial beginx = 0;y = 0;for(i = 0; i < 20; i = i + 1)begin//利⽤$random系统函数产⽣随机数。

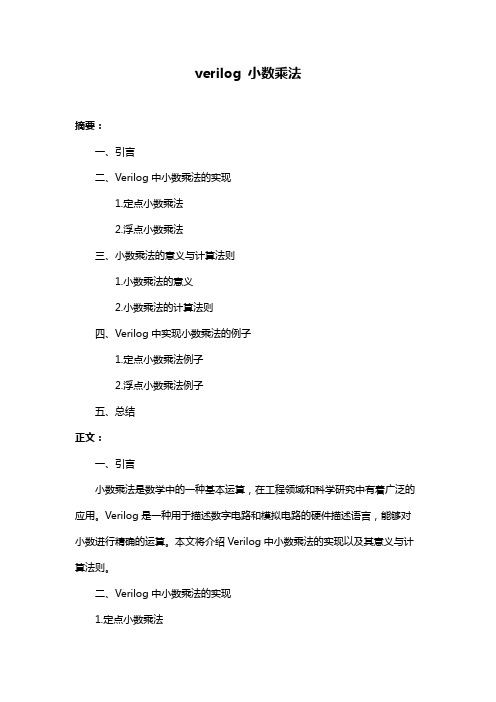

verilog 小数乘法

verilog 小数乘法摘要:一、引言二、Verilog中小数乘法的实现1.定点小数乘法2.浮点小数乘法三、小数乘法的意义与计算法则1.小数乘法的意义2.小数乘法的计算法则四、Verilog中实现小数乘法的例子1.定点小数乘法例子2.浮点小数乘法例子五、总结正文:一、引言小数乘法是数学中的一种基本运算,在工程领域和科学研究中有着广泛的应用。

Verilog是一种用于描述数字电路和模拟电路的硬件描述语言,能够对小数进行精确的运算。

本文将介绍Verilog中小数乘法的实现以及其意义与计算法则。

二、Verilog中小数乘法的实现1.定点小数乘法定点小数乘法是指将两个定点小数相乘,并保留一定的小数位数。

在Verilog中,我们可以通过编写代码实现定点小数乘法。

例如,假设两个定点小数为a和b,小数点后保留n位,则可以通过以下代码实现定点小数乘法:```verilogmodule fixed_point_multiplication (input [n-1:0] a,input [n-1:0] b,output [2*n-1:0] result);wire [2*n-1:0] partial_products [1:n];genvar i;generatefor (i = 0; i < n; i++) beginpartial_products[i] = a * b[i];endendgeneratewire [n-1:0] sum [1:n];wire [n-1:0] carry;generatefor (i = 0; i < n; i++) beginsum[i] = {partial_products[i][n-1:0], carry};carry = partial_products[i][2*n-1];endendgenerateresult = sum[n-1] + carry;endmodule```2.浮点小数乘法浮点小数乘法是指将两个浮点小数相乘,并保留一定的小数位数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog乘法运算转换一、概述Verilog是一种硬件描述语言,广泛应用于数字电路设计中。

在数字电路设计中,乘法运算是一种常见的运算操作,因为乘法运算需要消耗较多的硬件资源,设计一个高效的乘法运算电路对于数字电路设计而言至关重要。

本文将介绍Verilog乘法运算的转换方法,帮助读者更好地理解乘法运算电路的设计。

二、乘法运算原理乘法运算是一种基本的算术运算,其原理是将两个数相乘得到一个结果。

在数字电路中,乘法运算通常使用乘法器来实现。

乘法器的实现原理是将两个数分别拆分成多个部分,然后通过加法器和移位器等逻辑电路进行运算,最终得到乘法的结果。

三、乘法运算电路的转换针对Verilog中乘法运算的转换,可以采取以下几种方法来实现:1. 使用乘法器IP核现代的FPGA和ASIC芯片通常都内置了乘法器IP核,可以直接在Verilog代码中调用该IP核来进行乘法运算。

这种方法非常简单方便,但是需要注意IP核的资源占用情况。

2. 使用移位和加法如果没有乘法器IP核或者需要优化硬件资源的情况下,可以使用移位和加法来实现乘法运算。

这种方法需要将乘数和被乘数分别拆分成多个部分,然后通过移位和加法器来进行运算。

这种方法虽然相对复杂一些,但是可以更好地控制硬件资源的使用。

3. 使用查找表实现乘法器另一种常见的方法是使用查找表来实现乘法器。

通过预先计算乘法运算的结果并存储在查找表中,然后根据乘数和被乘数的值来索引查找表来获得乘法的结果。

这种方法可以大大减少乘法运算的计算量,提高运算的速度。

四、案例分析下面通过一个简单的Verilog代码示例来说明乘法运算的转换方法:```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法一:使用乘法器IP核assign result = a * b;endmodule```上述Verilog代码中,我们定义了一个模块mul,其中包含两个输入端口a和b,一个输出端口result。

在这个模块中,我们将乘法运算直接使用乘法器IP核来实现,通过assign语句来进行赋值操作。

这种方法非常简单直接,适用于对硬件资源占用要求不高的情况。

```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法二:使用移位和加法wire [15:0] temp;assign temp = a * b;always (*) beginresult = temp[7:0] + (temp << 8);endendmodule```在上面的Verilog代码中,我们采用了移位和加法的方法来实现乘法运算。

首先将乘数a和被乘数b相乘得到一个临时的变量temp,然后通过移位和加法来得到最终的乘法结果result。

这种方法相对于直接使用乘法器IP核来实现,可以更好地控制硬件资源的使用,适用于对硬件资源有较高要求的情况。

```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法三:使用查找表实现乘法器reg [15:0] lut [255:0];integer i, j;always * beginfor (i = 0; i < 256; i = i + 1) beginfor (j = 0; j < 256; j = j + 1) beginlut[i][j] = i * j;endendendalways * beginresult = lut[a][b];endendmodule```在上述Verilog代码中,我们采用了查找表的方法来实现乘法器。

首先定义了一个大小为256×256的二维数组lut,用于存储乘法运算的结果。

然后在两个循环中,根据乘数a和被乘数b的值进行乘法运算,并将结果存储在查找表中。

最后根据乘数a和被乘数b的值来索引查找表,得到乘法的结果result。

这种方法可以大大减少乘法运算的计算量,提高运算的速度。

五、总结本文介绍了Verilog乘法运算的转换方法,并通过具体的代码示例进行了说明。

针对不同的情况,可以选择适合的乘法运算转换方法来实现乘法运算电路的设计。

希望本文对读者能够有所帮助,更好地理解和应用Verilog乘法运算的转换方法。

Verilog乘法运算转换一、概述Verilog是一种硬件描述语言,广泛应用于数字电路设计中。

在数字电路设计中,乘法运算是一种常见的运算操作,因为乘法运算需要消耗较多的硬件资源,设计一个高效的乘法运算电路对于数字电路设计而言至关重要。

本文将介绍Verilog乘法运算的转换方法,帮助读者更好地理解乘法运算电路的设计。

二、乘法运算原理乘法运算是一种基本的算术运算,其原理是将两个数相乘得到一个结果。

在数字电路中,乘法运算通常使用乘法器来实现。

乘法器的实现原理是将两个数分别拆分成多个部分,然后通过加法器和移位器等逻辑电路进行运算,最终得到乘法的结果。

三、乘法运算电路的转换针对Verilog中乘法运算的转换,可以采取以下几种方法来实现:1. 使用乘法器IP核现代的FPGA和ASIC芯片通常都内置了乘法器IP核,可以直接在Verilog代码中调用该IP核来进行乘法运算。

这种方法非常简单方便,但是需要注意IP核的资源占用情况。

2. 使用移位和加法如果没有乘法器IP核或者需要优化硬件资源的情况下,可以使用移位和加法来实现乘法运算。

这种方法需要将乘数和被乘数分别拆分成多个部分,然后通过移位和加法器来进行运算。

这种方法虽然相对复杂一些,但是可以更好地控制硬件资源的使用。

3. 使用查找表实现乘法器另一种常见的方法是使用查找表来实现乘法器。

通过预先计算乘法运算的结果并存储在查找表中,然后根据乘数和被乘数的值来索引查找表来获得乘法的结果。

这种方法可以大大减少乘法运算的计算量,提高运算的速度。

四、案例分析下面通过一个简单的Verilog代码示例来说明乘法运算的转换方法:```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法一:使用乘法器IP核assign result = a * b;endmodule```上述Verilog代码中,我们定义了一个模块mul,其中包含两个输入端口a和b,一个输出端口result。

在这个模块中,我们将乘法运算直接使用乘法器IP核来实现,通过assign语句来进行赋值操作。

这种方法非常简单直接,适用于对硬件资源占用要求不高的情况。

```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法二:使用移位和加法wire [15:0] temp;assign temp = a * b;always (*) beginresult = temp[7:0] + (temp << 8);endendmodule```在上面的Verilog代码中,我们采用了移位和加法的方法来实现乘法运算。

首先将乘数a和被乘数b相乘得到一个临时的变量temp,然后通过移位和加法来得到最终的乘法结果result。

这种方法相对于直接使用乘法器IP核来实现,可以更好地控制硬件资源的使用,适用于对硬件资源有较高要求的情况。

```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法三:使用查找表实现乘法器reg [15:0] lut [255:0];integer i, j;always * beginfor (i = 0; i < 256; i = i + 1) beginfor (j = 0; j < 256; j = j + 1) beginlut[i][j] = i * j;endendendalways * beginresult = lut[a][b];endendmodule```在上述Verilog代码中,我们采用了查找表的方法来实现乘法器。

首先定义了一个大小为256×256的二维数组lut,用于存储乘法运算的结果。

然后在两个循环中,根据乘数a和被乘数b的值进行乘法运算,并将结果存储在查找表中。

最后根据乘数a和被乘数b的值来索引查找表,得到乘法的结果result。

这种方法可以大大减少乘法运算的计算量,提高运算的速度。

五、总结本文介绍了Verilog乘法运算的转换方法,并通过具体的代码示例进行了说明。

针对不同的情况,可以选择适合的乘法运算转换方法来实现乘法运算电路的设计。

希望本文对读者能够有所帮助,更好地理解和应用Verilog乘法运算的转换方法。

Verilog乘法运算转换一、概述Verilog是一种硬件描述语言,广泛应用于数字电路设计中。

在数字电路设计中,乘法运算是一种常见的运算操作,因为乘法运算需要消耗较多的硬件资源,设计一个高效的乘法运算电路对于数字电路设计而言至关重要。

本文将介绍Verilog乘法运算的转换方法,帮助读者更好地理解乘法运算电路的设计。

二、乘法运算原理乘法运算是一种基本的算术运算,其原理是将两个数相乘得到一个结果。

在数字电路中,乘法运算通常使用乘法器来实现。

乘法器的实现原理是将两个数分别拆分成多个部分,然后通过加法器和移位器等逻辑电路进行运算,最终得到乘法的结果。

三、乘法运算电路的转换针对Verilog中乘法运算的转换,可以采取以下几种方法来实现:1. 使用乘法器IP核现代的FPGA和ASIC芯片通常都内置了乘法器IP核,可以直接在Verilog代码中调用该IP核来进行乘法运算。

这种方法非常简单方便,但是需要注意IP核的资源占用情况。

2. 使用移位和加法如果没有乘法器IP核或者需要优化硬件资源的情况下,可以使用移位和加法来实现乘法运算。

这种方法需要将乘数和被乘数分别拆分成多个部分,然后通过移位和加法器来进行运算。

这种方法虽然相对复杂一些,但是可以更好地控制硬件资源的使用。

3. 使用查找表实现乘法器另一种常见的方法是使用查找表来实现乘法器。

通过预先计算乘法运算的结果并存储在查找表中,然后根据乘数和被乘数的值来索引查找表来获得乘法的结果。