数字电路课程设计PPT课件

合集下载

《数字电路~》PPT课件

NOL

IOL IIL

1616 1

IOH=-7.5mA,但手册规定 |IOH|<0.4mA,故取|IOH|=0.4mA;

IIL IOL

每个负载门的输入电流为

IIHNO=H 40μAIIOIHH

0.4 10 0.04

综上所述,扇出系数NO=10

IOH IIH

例:为保证G1输出的高低电平 能正确传递到G2,要求vO1=VOH、 vI2≥VIH<min>;vO1=VOL、 vI2≤VIL<max>,试计算RP的最 大允许值.所有参数见前

0 Voff1 Vth 2Von 3 VI/V

③ 输出高、低电平的最小值

输出高电平最小值VOHmin 输出低电平最大值VOLmax

2.4V 0. 4V

VOH VO/V

4 AB

VoHmin

2

C

VOL

DE 0 Voff1 Vth 2Von 3 VI/V

④ 阈值电压<Vth>: 转折区中点对应的输入电压称阈值电压Vth.

A&

B

AB

00 01 10 11

Y

Y

0 0 0 1

Y=AB

A Y

B

继续

2、二极管或门

5V A

D1 0V B

D2

Y

R

3kΩ

uA uB

0V 0V 0V 5V 5V 0V 5V 5V

uY

0V 4.3V 4.3V 4.3V

D1 D2 截止 截止 截止 导通 导通 截止 导通 导通

A ≥1

Y B

AB Y

00 0 01 1 10 1 11 1

扇出系数=10

<2> 74S20为4输入与非门:

第章数字电路PPT课件

⑵对偶规则 如果两个函数式相等,则它们对应的对偶式也相等。 即 若 F1= F2 则F1′= F2′。 ⑶作用:使定理公式的证明减少一半。

湖南理工学院信息与通信工程学院电子信息教研室制作

2.1 逻辑代数

2.1.2 逻辑代数的基本规则

3. 对偶规则

⑴对偶式规则: “ · ”、 “ + ”互换; “0”、“1”互换;得到

常用的代数化简方法

例2.1.7 化简 L AD A D AB A C BD AB EF B EF 解: L AD A D AB A C BD AB EF B EF

A AB A C BD AB EF B EF

2 .逻辑代数与 硬件描述语言基础

2.1 逻辑代数 2.2 逻辑函数的卡诺图化简法 2.3 硬件描述语言Verilog HDL基础

湖南理工学院信息与通信工程学院电子信息教研室制作

教学要求 1、熟悉逻辑代数常用基本定律、恒等式和规则。 2、掌握逻辑代数的变换和卡诺图化简法; 3、了解硬件描述语言Verilog HDL

⑵作用:扩大基本公式的应用范围。

利用摩根定律

BC代替B

例如,根据反演律 A B A B

得: ABC A BC A B C

由此,摩根定律能推广到n个变量:

A1 • A2

•

A •

n

A1

A2

An

A1 A2 A n A1 A • 2 • A • n

2.1 逻辑代数

2.1.3 逻辑函数的代数法化简

1. 逻辑函数的最简与-或表达式

一个逻辑函数可以有多种不同的逻辑表达式,五种常用表达式为:

F(A、B、C) AB AC

湖南理工学院信息与通信工程学院电子信息教研室制作

2.1 逻辑代数

2.1.2 逻辑代数的基本规则

3. 对偶规则

⑴对偶式规则: “ · ”、 “ + ”互换; “0”、“1”互换;得到

常用的代数化简方法

例2.1.7 化简 L AD A D AB A C BD AB EF B EF 解: L AD A D AB A C BD AB EF B EF

A AB A C BD AB EF B EF

2 .逻辑代数与 硬件描述语言基础

2.1 逻辑代数 2.2 逻辑函数的卡诺图化简法 2.3 硬件描述语言Verilog HDL基础

湖南理工学院信息与通信工程学院电子信息教研室制作

教学要求 1、熟悉逻辑代数常用基本定律、恒等式和规则。 2、掌握逻辑代数的变换和卡诺图化简法; 3、了解硬件描述语言Verilog HDL

⑵作用:扩大基本公式的应用范围。

利用摩根定律

BC代替B

例如,根据反演律 A B A B

得: ABC A BC A B C

由此,摩根定律能推广到n个变量:

A1 • A2

•

A •

n

A1

A2

An

A1 A2 A n A1 A • 2 • A • n

2.1 逻辑代数

2.1.3 逻辑函数的代数法化简

1. 逻辑函数的最简与-或表达式

一个逻辑函数可以有多种不同的逻辑表达式,五种常用表达式为:

F(A、B、C) AB AC

数字电路与逻辑设计.pptx

补码的特点之一就

是零的表示唯一: [+0]补=00…0

N位

[-0]补=11…1+1

N位

⑵补码的运算规则

采用补码表示的另一个好处就是当数值信息参与 算术运算时,采用补码方式是最方便的。

分类:

数字逻辑电路

组合逻辑 时序逻辑

研究方法

同步逻辑电路 异步逻辑电路

二、数制

1、进位计数制 进位计数制的基本因素:基数和位权。

基数是指计数制中所有到的数字符号的个数。在基数 为R的计数制中,包含0、1、…、R-1共R个数字符号,进 位规律是“逢R进一、借一当R”,称为R进位计数制。

位权是指在一种进位计数制表示的数中,用来表明不 同数位上数值大小的一个固定常数。不同数位有不同的位

换而言之,逻辑电路的分析与设计具有较大的弹

如何学好数字逻辑?

重视课堂学习

认真听课:听课时要紧跟教师授课思路,认真 领会每一个知识要点,抓住书本上没有的内容, 琢磨重点与难点。

做好笔记:适当地记录某些关键内容,尤其是 那些重点、难点、疑点,以便课后复习、思考

主动思考:听课时围绕教师所述内容及提出的 问题,主动思考问题,寻找自己的见解。

计算机专业 基础课程

数字逻辑

(必修课)

课程性质

“数字逻辑”是计算机各专业必修的一门重要 技术基础课。

该课程在介绍有关数字系统基本知识、基本理 论、及常用数字集成电路的基础上,重点讨论 数字逻辑电路分析与设计的基本方法。 从计算机的层次结构上讲, “数字逻辑” 是深入了解计算机“内核” 的一门最关键

在进行

数字技术的由来

计算机器件的历史发展

数字的出现

数字在各个古代文明中都独立的存在 数字都采用十进制数 阿拉伯数字

数字电路设计完整 第10讲 数字电路中的时序问题ppt课件

14

Timing Issues

Impact of Jitter

CLK

TC LK

t j itter

-tji tte r

REGS

Combinat ional

In

Logi c

C LK tc-q , tc-q, cd

ts u, thold tjitter

t log ic t log ic, cd

最坏情况下,周期至周期抖动绝对值等

Sources of clock uncertainty

© DEEig1i4ta1l Integrated Circuits2nd

8

Timing Issues

一、偏差 Positive and Negative Skew

R1 In

DQ

Combinational Logic

ห้องสมุดไป่ตู้

R2 DQ

Combinational Logic

设计一个偏差小的时钟网络是非常重要的!!!

© DEEig1i4ta1l Integrated Circuits2nd

12

Timing Issues

估计该逻辑电路的污染延时和最大延时

© DEEig1i4ta1l Integrated Circuits2nd

13

Timing Issues

二、时钟抖动(clock jitter)

16

Timing Issues

偏差和抖动的共同影响

© DEEig1i4ta1l Integrated Circuits2nd

17

Timing Issues

Clock skew>0时的约束条件:

Clock skew >0时的维持时间约束条件:

《数字电路cha》PPT课件

精选课件ppt

3

存储器类别

半导体存储器

随机操作存储器(RAM)

SRAM

DRAM

只读存储器(ROM)

固定ROM

按存储器件分类

可编程ROM:PROM,EPROM,EEPROM,Flash-ROM

其它存储器

磁表面存储器

光学存储器

精选课件ppt

4

存储器类别

主存储器

半导体存储器

辅助存储器

38

SRAM读周期工作波形时序

精选课件ppt

39

SRAM写周期工作波形时序

精选课件ppt

40

SRAM的特点

(1) 非破坏性的读出 (2) 速度较快: 与CPU一样都是用门或触发器等逻辑器件构成 的,其延迟时间与CPU在同一数量级

(3) 功耗大: 构成它的触发器中的MOS管任何情况下总有一 个是导通的,那么电源和地之间总有电流流过,因此功耗大,妨 碍了集成度提高

(非易失性) 储存固定不变的数据和程序,

如开机程序

精选课件ppt

60

磁表面存储器

计算机的外存储器又称磁表面存储设备。所谓磁 表面存储,是用某些磁性材料薄薄地涂在金属铝 或塑料表面作载磁体来存储信息。磁盘存储器、 磁带存储器均属于磁表面存储器。

磁表面存储器由于存储容量大,位成本低,在计 算机系统中作为辅助大容量存储器使用,用以存 放系统软件、大型文件、数据库等大量程序与数 据信息EPROM。

精选课件ppt

21

位扩展

把所有的地址线,R/W,CS连接在一起,数据线并列使用, 每一片的I/O端作为整个存储器的一位。

精选课件ppt

22

例1:存储容量为512×4, 8K×8和256K×1的SRAM各有多少 根地址线和数据线?

数字电路基础门PPT课件

基

本

A• (B • C)=(A • B) • C

定 律

分配律 A(B+C)=A • B+A • C

普通代

A+B • C=(A+B)(A+C) 数不适

用!

26 精选ppt课件2021

吸收律

A+AB=A

证明: A+AB=A(1+B)=A•1=A 利用运算规则可以对逻辑式进行化简。 例如:

A B C D AD B (E F )A B CD

1

33

注意!

n个变量可以有2n个组合,一般 按二进制的顺序,输出与输入状态一 一对应,列出所有可能的状态。

34 精选ppt课件2021

3. 逻辑函数表示形式的变换 (1)由真值表转换到与或表达式

A BC F

0 00 0 0 01 0 0 10 0 0 11 1 1 00 0 1 01 1 1 10 1 1 11 1

VD

A

&F

A

1

F

B

VD

B

2

41 精选ppt课件2021

二极管或门

VD

A1

F

A

1 F

B

VD

B2

精选ppt课件2021

-12V

42

三极管非门

+12V +3V

1F

A

R1

A R2

VD

F

43 精选ppt课件2021

与非门

A B

&

F

+12V

+12V +3V

A VD1

R1 R2

VD F

B VD2

二极管与门

数字电路设计经典资料ppt课件

上行总线接口为两条,每条的信号完全一样:

输入:CLK19、SPE、C1J1V1 输出:ADD 、 DATA[7:0]、PAR

D3

Sel

Cnt[1..0]

Clk

Cnt

整理版课件

7

认清数字电路设计

利用移位寄存器完成电路功能

D0

D1

D2

Shift

Q

D3

Load

Carry

Clk

Cnt

整理版课件

8

电路设计的三个层次

完成功能

能够完成电路要求完成的功能

工作可靠

电路的工作对外围环境要求最低; 电路不受温度、工艺等因数的影响

从电路图设计入手

可以很清楚电路是如何实现的; 可以很清楚电路结构,或会有意识的对电路

的模块进行划分;

如果从语言入手

必须熟悉电路,能很容易的读懂电路; 对电路的不同描述方式,要清楚综合工具的

综合结果

整理版课件

34

正确的入门方法

规范设计是入门的基础

规范设计可以避免一些电路不可靠因素; 真正可重用的电路绝对是规范的; 电路的功能实现不是最有价值的东西,最有

如:

RdCnt1、RdCntl、RdCntI

整理版课件

45

命名规则(9)

当文件中只包含一个模块时,文件名和 模块名保持一致。

当文件中有多个相关模块且没有顶层模 块,模块名须与各模块的功能相关

当一个模块中的子模块在别的电路中不 会使用时,可以将子模块和顶层模块放 置在一起,文件名和顶层模块名相同。

同步数字电路设计

同步电路(时序电路):

TDelay

T0

T1

T2

T3

C0 DFF C1 DFF C2 DFF C3

输入:CLK19、SPE、C1J1V1 输出:ADD 、 DATA[7:0]、PAR

D3

Sel

Cnt[1..0]

Clk

Cnt

整理版课件

7

认清数字电路设计

利用移位寄存器完成电路功能

D0

D1

D2

Shift

Q

D3

Load

Carry

Clk

Cnt

整理版课件

8

电路设计的三个层次

完成功能

能够完成电路要求完成的功能

工作可靠

电路的工作对外围环境要求最低; 电路不受温度、工艺等因数的影响

从电路图设计入手

可以很清楚电路是如何实现的; 可以很清楚电路结构,或会有意识的对电路

的模块进行划分;

如果从语言入手

必须熟悉电路,能很容易的读懂电路; 对电路的不同描述方式,要清楚综合工具的

综合结果

整理版课件

34

正确的入门方法

规范设计是入门的基础

规范设计可以避免一些电路不可靠因素; 真正可重用的电路绝对是规范的; 电路的功能实现不是最有价值的东西,最有

如:

RdCnt1、RdCntl、RdCntI

整理版课件

45

命名规则(9)

当文件中只包含一个模块时,文件名和 模块名保持一致。

当文件中有多个相关模块且没有顶层模 块,模块名须与各模块的功能相关

当一个模块中的子模块在别的电路中不 会使用时,可以将子模块和顶层模块放 置在一起,文件名和顶层模块名相同。

同步数字电路设计

同步电路(时序电路):

TDelay

T0

T1

T2

T3

C0 DFF C1 DFF C2 DFF C3

数字电路与逻辑设计-演示文稿3精选PPT文档

Y

1 0 11

1 1 01

1 1 10

解答:

AB C L 0 0 01 0 0 11 0 1 01 0 1 10

1 0 01 1 0 11 1 1 01 1 1 10

BC A 00 01 11 10

01 1 0 1 11 1 0 1

Y= B+C =B+C

四、用74138集成译码器和逻辑门设计1位全减器。

C1

Q2

1K

FF2

C1

1K

Q1

FF1

C1

1K Q0 FF0

CP

解答: 1、驱动方程 2、状态方程

3、状态表 4、状态图

100

010

001

000

011

101

110 111

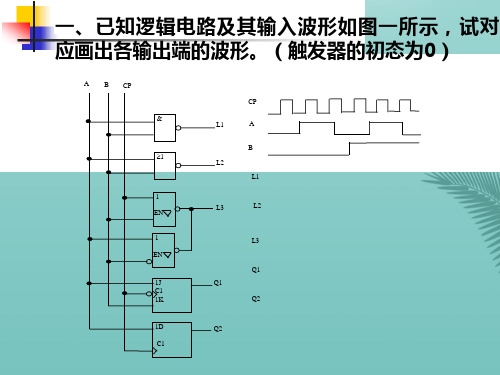

六、时序电路如下图所示,已知A、CP的波形,试对应画出 Q1 、Q0输出波形。

Q0

Q1

A

1J

1J

C1

C1

1 1K R

1 1K R

F2(ABCD) =ABD+ABC+BCD+ACD =Y1Y2 Y4 Y7

010

F2(ABCD) =ABD+ABC+BCD+ACD

3) 已知CP的频率fcp=1KHz,试确定vo的周期。

111 011 十一、集成移位寄存器74194和10位集成D/A转换器AD7520组成的电路如图六所示,已知CP和ST的波形:

2) 定量出画图中vo的波形; 3) 已知CP的频率fcp=1KHz,试确定vo的周期。

CP 1 1 1 0

1 S0 V D C B A DSL

ST &

S1

74194

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

验证方式

计算机语言主要关注于变量值的变化

VHDL要实现严格的时序逻辑关系

17

3 VHDL的基本语法-与计算机语言的区别

C、ASM… 程序

软件程序编译器 COMPILER

((aA))软件语言设计目标流程

CPU指令/数据代码: 010010 100010 1100

VHDL/VERILOG 程序

硬件描述语言综合器 SCYONMTPHEISLIEZRER

最高集成度已达到400万门

向低电压和低功耗方向发展

5V3.3V2.5V1.8V更低

内嵌多种功能模块

MacroFuction、Megafunction IP Core: RAM,ROM,FIFO,DSP,CPU SOPC

向数、模混合可编程方向发展

12

2 可编程逻辑器件-主要制造商

CPLD Product-term 内部EEPROM 组合电路资源丰富

低 完成控制逻辑

慢 - 可加密

FPGA Look-up Table SRAM,外挂EEPROM 触发器资源丰富

高 能完成比较复杂的算法

快 EAB,锁相环 一般不能保密

15

3 VHDL的基本语法

HDL

Hardware Description Language 硬件描述语言

X

状态方程

Z

组合电路

Y

Q

时序电路

CLK

8

1 概述-数字电路设计的基本方法

布尔函数-数字系统数学基础(卡诺图) 数字电路设计的基本方法

组合电路设计

问题逻辑关系真值表化简逻辑图

时序电路设计

列出原始状态转移图和表状态优化状态分配 触发器选型求解方程式逻辑图

使用中、小规模器件设计电路

9

2 可编程逻辑器件-基本概念

eqcomp4.vhd

库

--eqcomp4 is a four bit equality comparator Library IEEE;

包

use IEEE.std_logic_1164.all;

实体

entity eqcomp4 is port (a, b:in std_logic_vector(3 downto 0);

MAX +PlusII Quartus II

掌握一种硬件描述语言(方法)

VHDL Verilog

6

1 概述-考核

考核的形式

日常成绩+设计成绩+报告+考试

报告的要求

见实验中心网站的模板

/

7

1 概述-数字电路系统的基本构成

输出方程

激励方程

EDA技术与应用 江国强 电子工业出版社, 2010

EDA技术与VHDL设计 徐志军等,电子 工业出版社,2009

3

1 概述-参考资料

VHDL与数字电路设计.卢毅赖杰.科学出 版社,2001

EDA技术实验与课程设计.曹昕燕.清华大 学出版社,2006

EDA技术综合应用实例与分析.谭会生.西 安电子科技大学出版社,2004

((bB))硬件语言设计目标流程

DQ

JQ K

为ASIC设计提供的电路网表文件

18

3 VHDL的基本语法-基本结构

VHDL程序的基本结构

Library

库

Entity

实体

Architee

程序包

Configuration

配置

19

3 VHDL的基本语法-基本结构

数字电路课程设计 2011秋季

大连理工大学电信学部 赵权科 2011.09

1

1 概述-教学安排

学时:24 教材:见参考资料 上课教室:综-220 上课时间:第3周-第16周

选课

2

1 概述-参考资料

EDA技术实用教程 潘松黄继业.科学出版 社,2006

FPGA与SOPC设计教程-DE2实践 张志刚 西安电子科技大学出版社,2007

equal :out std_logic); end eqcomp4;

结构体

architecture dataflow of eqcomp4 is begin

最大的PLD供应商之一

FPGA的发明者,最大的PLD供应商之一

ISP技术的发明者

提供军品及宇航级产品

13

2 可编程逻辑器件-分类

按集成度高低

PROM、EPROM、EEPROM、PAL、PLA、GAL CPLD、FPGA

4

1 概述-教学目的

以《数字电子技术》为基础,学习数字 电路系统的基本设计方法

以可编程逻辑器件为基础,掌握硬件描 述语言VHDL设计数字电路系统的新方 法

面向工程应用,理论结合实践,提高电 路系统的设计水平

5

1 概述-课程内容

了解大规模可编程逻辑器件的结构及工作原 理(基础)

熟悉EDA软件的使用方法(工具)

按结构特点

与或阵列结构-PROM,EEPROM,PAL,GAL,CPLD 门阵列结构 -FPGA

按编程工艺

Fuse/Anti-Fuse

EEPROM-大多数CPLD

SRAM -大多数FPGA

14

2 可编程逻辑器件-CPLD与FPGA的区别

内部结构 程序存储 资源类型 集成度 使用场合 速度 其他资源 保密性

VHDL Verilog HDL System C System Verilog

16

3 VHDL的基本语法-与计算机语言的区别

运行的基础

计算机语言是在CPU+RAM构建的平台上运行

VHDL设计的结果是由具体的逻辑、触发器组成 的数字电路

执行方式

计算机语言基本上以串行的方式执行

VHDL在总体上是以并行方式工作

PLD

Programmable Logic Device 可编程逻辑器件

CPLD/FPGA

Complex Programmable Logic Device 复杂可编程逻辑器件

Field Programmable Gate Array 现场可编程门阵列

10

2 可编程逻辑器件-PLD的优点

集成度不断提高

可减小电路的面积,降低功耗,提高可靠性

具有先进的开发工具

提供语言、图形等设计方法,十分灵活 通过仿真工具来验证设计的正确性

可反复地编程,方便设计的修改和升级 可灵活地定义管脚功能,减轻设计工作

量,缩短系统开发时间 保密性好

11

2 可编程逻辑器件-PLD的发展趋势

向高集成度、高速度方向进一步发展