高精度3阶delta-sigma调制器的设计

【通俗易懂】浅谈Delta-Sigma之工作原理

浅谈Delta-Sigma之工作原理文/黄克强’95年初老朽准备「EAD-DSP系列之DSP演算法」(详见高传真227期)之前,蒲总编曾经向老朽提及Crystal公司的CS4328、CS4330……一系列的IC,希望我能写一系列的文章来谈这一系列广泛用途之Over Sampling之D/A Converter IC,其实这一系列的IC都是采用了所谓之「分段式Up Sample」的DSP架构搭配△-Σ之D/A Converter而成,由于老朽在『细说EAD-DSP系列之DSP演算法」一支中并末谈及△-Σ的工作原理,因此特别请我的好友黄克强博士来撰写△-Σ的部份。

——何志诚何老朽是我的挚友兼同事,他的办公桌就在笔者的左手边。

他是个发烧友,也是音响专家。

而笔者却是个音响白痴(编者:唉!唉!黄先生实在太谦虚了,如果您是白痴,那我们岂不……)。

他专精信号处理,尤其是Over Sampling。

而笔者擅长数位通讯及一点点适应性控制。

半年前,甚至更久之前,何老朽拿了一些CS4328之类的Data Sheet及他在高传真发表的文章给我,这时我才在他的调教之下初窥发烧音响之门径。

谁知黄鼠狼给鸡拜年不怀好意,何老朽半哄半骗的要我替他写一篇有关Delta-Sigma的介绍文章。

碍于多年交情,我勉强答应下来。

事后才发现这种文章真难写。

为了能在高传真杂志上「露脸」,必须避免学院派的数学推导,又必须把东西写得清清楚楚(要不然就变成低传真),真是难。

难!难!难!难!不过何老朽毕意没看走眼,笔者费了九牛二虎之力,终究把它写出来了。

但由于笔者笔法不够老练,写出来的文章可能还是生硬了些,尚请读老您多多包涵。

有任何批评指教,请找何老朽代转,包君满意!图零是CS4328的方块图,第一个方块8X Interpolation Filter已经在何老朽以前的一系列高传真文章中介绍过了。

第二个方块就是本文所要谈的Delta-Sigma(△Σ)。

sigmadeltaadc的工作原理

sigmadeltaadc的工作原理Sigma-Delta ADC,全称为Sigma-Delta Analog-to-Digital Converter,是一种高精度的模数转换器。

它的工作原理基于Sigma-Delta调制技术,通过对输入信号进行高速采样和数字化处理,实现对模拟信号的准确量化和转换。

Sigma-Delta ADC的核心部件是一个差分运算放大器和一个数字滤波器。

首先,输入信号经过差分运算放大器进行放大,并与一个参考电压进行比较。

差分运算放大器会将输入信号转换为差分信号,并将其与参考电压进行比较,产生一个差分输出信号。

这个差分输出信号包含了输入信号与参考电压之间的差异。

接下来,差分输出信号经过一个积分器,将其进行积分运算。

积分器的作用是将输入信号中的高频成分滤除,只保留低频成分。

积分后的信号再经过一个比较器,将其与一个数字信号进行比较。

比较器会产生一个数字输出信号,表示差分输出信号与数字信号之间的差异。

然后,数字输出信号通过一个反馈回路送回到差分运算放大器的输入端,起到调节放大器增益的作用。

通过不断调节放大器增益,使得差分输出信号与数字信号之间的差异尽可能小。

这个反馈回路的作用类似于一个控制系统,通过自动调节放大器增益,使系统的稳定性和精度得到保证。

Sigma-Delta ADC的工作原理可以用一个简单的例子来说明。

假设我们要将一个模拟信号转换为一个8位的数字信号。

首先,输入信号经过差分运算放大器进行放大,并与一个参考电压进行比较。

差分运算放大器会将输入信号转换为差分信号,并将其与参考电压进行比较,产生一个差分输出信号。

如果差分输出信号大于参考电压,则比较器输出1;如果差分输出信号小于参考电压,则比较器输出0。

接下来,差分输出信号经过积分器进行积分运算。

积分器会将差分输出信号进行积分,得到一个积分后的信号。

然后,积分后的信号再经过比较器进行比较,产生一个数字输出信号。

如果积分后的信号大于数字信号,则比较器输出1;如果积分后的信号小于数字信号,则比较器输出0。

Sigma-Delta ADC中抽取滤波器的设计与实现的开题报告

Sigma-Delta ADC中抽取滤波器的设计与实现的开题报告一、选题背景及研究意义Sigma-Delta ADC抽取滤波器是Sigma-Delta调制器中最为关键的一个组成部分,它对ADC整个系统性能的影响非常大。

抽取滤波器的作用是减小Sigma-Delta ADC的过采样率,缩小ADC转换器的宽带,从而减小数字滤波器的计算量,提高Sigma-Delta ADC抽取率和工作效率。

抽取滤波器设计精度要求高,设计难度大,对滤波器设计者的理论水平有着很高的要求。

因此,设计一种高效、高性能的Sigma-Delta ADC抽取滤波器是当前研究热点之一。

本篇开题报告旨在探索Sigma-Delta ADC抽取滤波器的设计与实现,为其优化提供理论参考和技术支持。

二、研究内容和方法本研究的内容主要包括:1. 研究Sigma-Delta ADC抽取滤波器的主要设计原理和特点,分析其难点和瓶颈;2. 探索Sigma-Delta ADC抽取滤波器设计的各种算法和方法,比较其优缺点,实现对各种算法的评估、验证和对比;3. 设计一种符合IFI6UHPC架构的Sigma-Delta ADC抽取滤波器电路,实现其关键算法和方法功能;4. 对设计的Sigma-Delta ADC抽取滤波器电路进行实验测试,验证其设计的正确性和性能优越性;5. 最后,对设计过程和实验结果进行详细分析和总结,并提出改进和优化方案。

本研究的方法主要包括:1. 文献资料研究法:查阅与Sigma-Delta ADC抽取滤波器相关的文献资料,了解其发展历程、设计思路和实现细节;2. 算法研究法:针对Sigma-Delta ADC抽取滤波器的各种算法和方法,比较其优缺点,实现对各种算法的评估、验证和对比;3. 仿真模拟法:利用计算机软件对设计的Sigma-Delta ADC抽取滤波器电路进行仿真模拟,进行性能分析和优化调试;4. 实验验证法:采用硬件电路搭建方式对设计的Sigma-Delta ADC抽取滤波器电路进行实验验证,验证其设计的正确性和性能优越性。

Sigma_deltaADC中数字滤波器设计

WANG H eng CHEN Y ong ( Schoo l o fM icroe lectronics and So lid-State E lectronics, Un iversity of E lectronic

C IC滤波器实现时每级必须保持一定的精度,

否则可能发生运算溢出。 C IC滤波器的增益为 DN, 因此该系统中它 的增益 为 324。输入 信号为 1 bit sigm a-delta信号, 因此系统中寄存器和组合逻辑的 字长均为 20 b i,t 可保证不会发生溢出。

图 2 C IC滤波器具体实现框图

坦, 约有 1 dB 的衰减, 而指标要求 0 ~ 20 kH z内通 设计在求平均值的方法上做出了改进: 假设连续三

带纹波在正负 0 05 dB范围内波动。因此必须由下 个 500 m s的周期分别为周期 A, 周期 B 和周期 C。

级滤波器补偿这 1 dB的衰减, 确保带内保持平坦。 A, B两个周期内分别计算出平均值 X, Y。在周期 C

抽取滤波器的多级实现可以显著地减少运算量

和存储量 [ 2] 。滤波器的阶数与过渡带宽度成反比。 前级滤波器的采样频率高, 但是过渡带很宽, 因此前 级的滤波器阶 数比较小。后 级滤波器的过 渡带较 小, 但此时采样频率同样很低, 因此后级滤波器的阶 数同样较小。一般多级分解每级滤波器的计算量和 存储量总和远小于未分解的滤波器。

图 4 ( a) CIC 滤 波器 幅频 特 性; ( b ) 音频 范围 ( 0~ 20 kH z) 内滤波器的幅频特性

( 1为 F IR, 2为 C IC, 3为 F IR 补偿 C IC 后 系统整 体的 幅 频响应 ) F ig. 4 ( a) T he frequency response o f CIC filter; ( b) T he

Sigma-DeltaADC讲稿

NTzF Y Ezz1z1

• 噪声传输函数表示一个离散时间微分器(高通滤 波器),这相当于引入了一个整形函数,量化噪 声的传输函数幅度为

|NfT | 2 F sif/ n fs

• 随着频率的降低,噪声传输函数的幅度也 逐步降低。经过噪声整形NTF(z)以后,在 信号带宽内的量化噪声功率和SNR为

OSR f s 2 fb

• 信号经过量化之后,y1(n)由H(f)滤波产生 了信号y2(n),如图所示。

• 滤波器滤除了频率比fb大的量化噪声部分

Se(f)

-fs/2

0

fs/2

f

-fb fb -fb fb

• 频率低于信号带宽fb时,y2(n)输入信号的功率 不变,而量化噪声功率减小到

E S fs/2 2 Q fs/2 e

fs

Se(f)

-fs/2

0

fs/2

f

量化噪声功率谱密度

SNR的计算

Δ为量化误差 Vp是输入满幅正弦信号的幅度

奈奎斯特采样的局限

• ADC的精度完全由量化器精度决定。 • ADC需要很陡的前置抗混叠低通滤波器。

过采样技术

• 如果采样频率fs比信号频率fb大很多,称这 种情况为过采样,定义过采样率为:

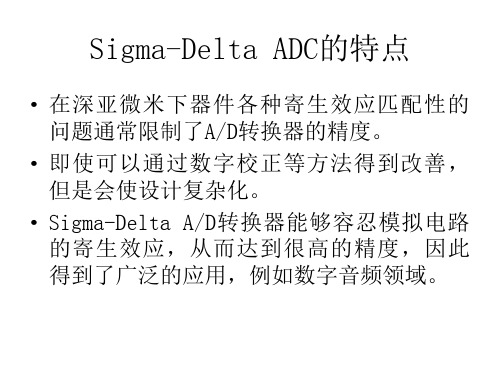

Sigma-Delta ADC的特点

• 在深亚微米下器件各种寄生效应匹配性的 问题通常限制了A/D转换器的精度。

• 即使可以通过数字校正等方法得到改善, 但是会使设计复杂化。

• Sigma-Delta A/D转换器能够容忍模拟电路 的寄生效应,从而达到很高的精度,因此 得到了广泛的应用,例如数字音频领域。

噪声整形技术

• 通用噪声整形Sigma-Delta调制器和它的线 性模型如图所示:

Sigma-Delta模数转换器中数字抽取滤波器的设计与ASIC实现的开题报告

Sigma-Delta模数转换器中数字抽取滤波器的设计与ASIC实现的开题报告一、选题背景随着现代通信和计算机技术的发展,模数转换器(ADC)的应用越来越广泛和重要。

Sigma-Delta模数转换器是一种常见的ADC,它可以在低位数、宽动态范围和高精度的应用中发挥优异的性能。

互补金属氧化物半导体(CMOS)技术广泛应用于集成电路(IC)的设计和制造中,ASIC实现在高性能和低功耗方面具有优势。

因此,设计和实现Sigma-Delta模数转换器中数字抽取滤波器的ASIC是一个非常有价值的课题,也是本文的选题背景。

二、研究目的和意义本项目的主要目的是研究Sigma-Delta模数转换器中数字抽取滤波器的设计和制造技术,并实现ASIC。

具体地,本课题研究了数字抽取滤波器的设计方法和实现过程,包括滤波器系数的计算、器件和电路设计、模拟仿真和ASIC实现等步骤。

该项研究对于拓展数字抽取滤波器的应用、提高数字信号处理技术的水平、推动Sigma-Delta模数转换器的发展等方面具有重要的意义和价值。

三、研究内容和关键技术本项目的研究内容主要包括:1. 数字抽取滤波器的设计方法和理论基础:了解数字抽取滤波器的基本原理,包括数字信号处理的基本概念和原理,数字滤波器的基础知识,数字抽取滤波器的设计流程等。

2. 数字抽取滤波器的器件和电路设计:研究数字抽取滤波器的具体器件和电路的设计方法和技术,包括模拟抽取级的设计、数字滤波器的结构和功能、数字滤波器的稳定性等。

3. 数字抽取滤波器的模拟仿真:使用电子设计自动化(EDA)仿真工具,对数字抽取滤波器进行仿真实验,验证滤波器参数是否符合设计要求,检测滤波器性能并优化滤波器。

4. ASIC实现:在德州仪器(TI)公司的CMOS工艺下,实现数字抽取滤波器的ASIC,包括电路的布局、布线和物理实现等。

本项目的关键技术包括:数字信号处理、数字滤波器的设计、仿真和验证技术,CMOS工艺的设计和制造技术等。

sigma-delta采样原理

sigma-delta采样原理

Sigma-Delta采样是一种高精度的ADC(模数转换器)技术,它的原理是通过高速的模拟信号采样和数字信号处理,实现对模拟信号的高精度数字化转换。

Sigma-Delta采样的基本原理是,将模拟信号通过一个高速的模拟信号采样器进行采样,然后将采样后的信号与一个数字信号进行比较,得到一个误差信号。

这个误差信号再经过一个积分器和一个比例放大器,得到一个反馈信号,这个反馈信号再通过一个数字信号处理器进行数字滤波和数字降噪,最终得到一个高精度的数字信号输出。

Sigma-Delta采样器的优点是,它可以实现高精度的数字信号转换,同时具有很高的抗干扰能力和低成本的优势。

它的缺点是,由于需要进行高速的模拟信号采样和数字信号处理,因此需要较高的计算能力和处理速度,同时也需要较高的电源噪声抑制能力。

Sigma-Delta采样技术广泛应用于音频、视频、通信、汽车电子、医疗设备等领域,成为了现代电子技术中不可或缺的一部分。

18位高精度音频Σ-ΔDAC设计

18位高精度音频Σ-ΔDAC设计徐双武1,白天蕊2,胡纯意2,陶而芳2,杨修3(1.西南交通大学微电子研究所,四川成都610031;2.中南大学物理科学与技术学院,湖南长沙410083; 3.登颠微电子公司,四川成都610041)2008-10-21摘要:采用基于过采样Σ-ΔDAC调制技术设计的音频D/A转换器,对量化噪声进行有效整形,提高了分辨率和带内信噪比(SNR)。

重点对Sigma-delta设计进行了详细分析,给出了有关电路结构和仿真结果。

芯片已在TSMC 0.18μm CMOS工艺上流片成功,在工作频率6.144MHz时动态范围达128.6dB,信噪比109.5dB,总谐波失真达-117.2dB。

关键词:过采样;Σ-ΔDAC;DEM;传递函数随着数字音频技术的迅速发展,高分辨率D/A转换器被大量使用,与传统D/A调制器相比,基于过采样技术的Sigma-delta modulate(SDM)DAC对噪声进行整形和对量化噪声进行有效抑制,且在提高信噪比(SNR)、后端模拟滤波器设计以及物理实现上具有很大的优势。

文章首先从系统的角度出发,根据音频DAC的总体性能要求,对Σ-ΔDAC的结构、性能、优缺点进行了分析,选择出合适的结构;在确定调制器结构以后,再分析结构对各个电路模块的影响,给出电路模块的设计指标;最后根据这些指标完成电路设计以及相应的版图设计。

1 Σ-ΔDAC的结构Σ-ΔDAC由插值滤波器(Interpolator)、Sigma-delta调制器(SDM)、动态匹配单元(DEM)、重构滤波器(SC Filte)组成,其原理框图如图1所示。

采样率为48kHz的18bit数据经过插值滤波器得到128倍的过采样数据,再经过三阶4bitΣ-Δ调制器得到15bit码流,进入三阶全差分模拟重构滤波器,从而完成数据的转换,得到所需信号。

1.1 插值滤波器的设计插值滤波器采用多级滤波器实现128倍过采样,若采用单个滤波器实现,则滤波器需要非常狭窄、陡峭的过渡带,物理实现有很大困难,故降低了后端滤波器的要求。

一种3阶Mash结构的Σ-△音频数模转换器

一种3阶Mash结构的Σ-△音频数模转换器来新泉;陈勇;叶强;龙燕【摘要】针对传统的Mash结构由于各级失配导致信噪比低的问题,本文采用一阶相位累加器来实现传统的sigma-delta(Σ-△)架构,并将其采用硬件描述语言来实现,这样整个系统均在数字域实现,从根本上解决了各级间的失配问题.在插值滤波器的设计上,使用优化了的半带滤波器结构和级联积分梳状滤波器,节省了硬件资源.电路采用的是Magnachip 180nm lP4M标准CMOS工艺,芯片面积只有0.2025mm2(0.45×0.45),实测芯片得到的信噪失真比(SNDR)达到90dB.【期刊名称】《电子学报》【年(卷),期】2018(046)005【总页数】6页(P1240-1245)【关键词】音频数模转换器;Mash Σ-△调制器;插值滤波器【作者】来新泉;陈勇;叶强;龙燕【作者单位】西安电子科技大学电路CAD研究所,陕西西安710071;西安电子科技大学电路CAD研究所,陕西西安710071;西安电子科技大学电路CAD研究所,陕西西安710071;西安电子科技大学电路CAD研究所,陕西西安710071【正文语种】中文【中图分类】TN4921 引言目前,传统的模拟音频处理已经逐步被数字音频处理所取代,而数字音频处理中的数模转换器直接影响了音频的质量.Σ-Δ数模转换器以其高分辨率、高精度、易于实现等优势成为目前的主流[1].如何设计出高精度、结构简单、稳定性高的Σ-Δ数模转换器成为研究的热点.Σ-Δ调制器是Σ-Δ数模转换器设计的核心,直接影响着整个系统的性能.一般来说,Σ-Δ调制器从结构上可以分为两种:单环高阶结构和Mash结构.单环高阶Σ-Δ调制器由于其零点过于集中,会导致高频处的增益过大,从而降低了系统的稳定性,也就限制了整个系统的输入输出动态范围.针对这一问题,文献[2]提出了一种自适应Σ-ΔA/D转换器,使得输出信号的信噪比和输入信号的信噪比没有关系。

浅谈Delta-Sigma之工作原理

浅谈Delta-Sigma之工作原理文/黄克强’95年初老朽准备「EAD-DSP系列之DSP演算法」(详见高传真227期)之前,蒲总编曾经向老朽提及Crystal公司的CS4328、CS4330……一系列的IC,希望我能写一系列的文章来谈这一系列广泛用途之Over Sampling之D/A Converter IC,其实这一系列的IC都是采用了所谓之「分段式Up Sample」的DSP架构搭配△-Σ之D/A Converter而成,由于老朽在『细说EAD-DSP 系列之DSP演算法」一支中并末谈及△-Σ的工作原理,因此特别请我的好友黄克强博士来撰写△-Σ的部份。

——何志诚何老朽是我的挚友兼同事,他的办公桌就在笔者的左手边。

他是个发烧友,也是音响专家。

而笔者却是个音响白痴(编者:唉!唉!黄先生实在太谦虚了,如果您是白痴,那我们岂不……)。

他专精信号处理,尤其是Over Sampling。

而笔者擅长数位通讯及一点点适应性控制。

半年前,甚至更久之前,何老朽拿了一些CS4328之类的Data Sheet及他在高传真发表的文章给我,这时我才在他的调教之下初窥发烧音响之门径。

谁知黄鼠狼给鸡拜年不怀好意,何老朽半哄半骗的要我替他写一篇有关Delta-Sigma的介绍文章。

碍于多年交情,我勉强答应下来。

事后才发现这种文章真难写。

为了能在高传真杂誌上「露脸」,必须避免学院派的数学推导,又必须把东西写得清清楚楚(要不然就变成低传真),真是难。

难!难!难!难!不过何老朽毕意没看走眼,笔者费了九牛二虎之力,终究把它写出来了。

但由于笔者笔法不够老练,写出来的文章可能还是生硬了些,尚请读老您多多包涵。

有任何批评指教,请找何老朽代转,包君满意!图零是CS4328的方块图,第一个方块8X Interpolation Filter已经在何老朽以前的一系列高传真文章中介绍过了。

第二个方块就是本文所要谈的Delta-Sigma(△Σ)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0 引言

模数转换器(ADC)在信号处理中起了一个非常重要的作用。在数字音

频、数字电视、图像编码及频率合成等领域需要大量的数据转换器。

由于超大规模集成电路的尺寸和偏压不断减小,模拟器件的精度和动

态范围也不断降低,对于实现高分辨率的ADC是一种挑战。高阶多位

Delta-sigma ADC由于不需要采样保持电路,电路规模小,可以实现

较高的分辨率,因此在实际中得到广泛的应用。Delta-sigma ADC采

用过采样技术和噪声整形技术相结合,对量化噪声双重抑制,从而实

现高精度模数转换。在实际的设计中需要根据设计指标稳定性和动态

范围等进行折衷。要实现大的动态范围,就需要较高的过采样率和多

位量化器。为了保持高阶DSM的稳定性就需要使用多位量化器,而多

位量化器会增加后续内部ADC的设计难度。因此,必须仔细选择过采

样率和量化器的位数,以实现预期的性能指标。本文提出一种三阶单

环局部反馈的Delta-sigma调制器结构,利用Richard Schreier的

Matlab Delta-sigma调制器设计工具包,推导调制器传输函数,并

对系数进行优化,使用Verilog硬件语言对调制器进行行为级建模。

调制器的信号带宽为32.8kHz,过采样率为128,工作时钟8.4MHZ,

精度16位,可以达到145dB以上的SNR。

1 Delta-sigma调制器的原理和结构

△-∑调制技术来自高分辨率的A/D、D/A变换器中的过取样△-∑

转换技术,利用经典自动控制理论中负反馈概念,通过反馈环来提高

量化器的有效分辨率并整形其量化噪声。在对信号进行过取样后,噪

声功率谱幅度降低,并通过一个对输入呈低通而对量化噪声呈现高通

的噪声整形器,将量化噪声功率的绝大部分移到信号频带之外,从而

可通过滤波有效地抑制噪声。

Delta-sigma调制器的仿真模型可以用图1来表示。该系统是一个双

端输入、单端输出的线性系统,系统的一个输入为外部输入信号U,

另一个输入为量化器的反馈V,输出则是量化器的输入Y。

由图1根据叠加原理,可知系统的输出可以表示为

其中,L0(z)和L1(z)分别是输入U(z)和V(z)到输出Y(z)的传递函数。

令调制器量化噪声为E(z),则调制器的输出为

由式(1)、(2)可得

其中G(z)是信号传递函数(STF),H(z)是NTF(NTF)。所以

这种仿真模型将不同结构的Delta-sigma调制器用同一种模型来描

述。因此,在设计调制器的NTF时不必考虑调制器具体的实现结构。

2 三阶单环DSM结构

2.1 高阶稳定的调制器函数的设计

高阶Delta-sigma的NTF具有一般形式(5)。从表达式可以看出,NTF

的n个零点都集中直流频率处。但是,文献指出,如果将NTF的零点

均匀地分布在信号基带中,而不是全都集中在直流频率处,将对量化

噪声有更好的整形效果。Delta-sigma调制器的不稳定状态主要与调

制器N-TF的带外增益有关,为了限制NTF的带外增益,将式(5)所示

的NTF的一般表达式改写成式(6)。

通过调整D(z)就可以有效地达到限制NTF带外增益的目的。

Delta-sigma调制器的设计重点就是设计出使系统稳定mSTF和NTF。。

在文献中指出,NTF的极点决定了它的带外增益,而带外增益又与系

统的噪声整形性能及稳定性密切相关,带外增益越高,噪声整形的效

果越好,但是带外增益过高系统将不能稳定,而且带外增益越高则输

入信号的稳定的范围越小。所以,对于3阶以上的Delta-sigma调制

器,随着输入信号幅度的增加,调制器的SNR线性增长,但是当输入

的幅度超过一定值后。调制器的SNR突然下降,这时的调制器就处于

不稳定的状态。NTF的带外增益决定了输入信号幅度和调制器输出

SNR之间的一对矛盾关系。

在调制器阶数、过采样率以及调制器位数确定的情况下,调制器NTF

设计的关键问题是,找出调制器能够稳定所对应的输入范围。最大

SNR所对应的输入范围就是调制器能够稳定所对应的输入范围。

2.2 改进的DSM结构图

实现传输函数的拓扑结构不是唯一的,是多种形式的,一般来说有四

种结构使用最为普遍CIFB(cascade-integrator-feedback)、

CRFB(cascade-resonator-feedback)、

CIFF(cascade-integrator-feedforward)、

CRFF(cascade-resonator-feedforward)。如果不需要经过零点优化,

可以采用CIFB和CIFF的结构,需要零点经过优化可采用CRFB和CRFF

结构。本文是高精度调制器的设计,而经过零点优化的可以得到更好

的噪声整形,实现更高的精度,而CRFF相对CRFB结构在电路设计方

面具有结构更为简单和电路规模更小的优势,所以采用CRFF结构,

如图2。

由图可以看出,输入信号在比较器前与前馈信号直接相加,实现了

STF为1,因此数字滤波器可以不需要考虑基带补偿;al-a3前馈方式

实现NTF的极点,降低了积分器输出的幅度;第三级积分器输出通过

g反馈给第二级积分器,即局部反馈(LFB),这在NTF中引入了共轭

零点,挺高了基带SNR。根据高阶稳定的调制器函数的设计方法,设

计一个过采样率为128和3位量化器的3阶调制器,图2中的系数值(a1、

a2、a3、a4、bl、b2、b3、b4、cl、c2、c3、g1),由Richard Schreier

提供的Matlab Delta-sigma调制器设计工具包可以得出,具体值在

表1中给出,表中的数值用于设计NTF和STF的Matlab模型。在实际

的数字电路实现时,为了减少芯片面积和设计难度避免使用乘法器,

所以这些系数均取2n的近似值,这样可以用移位相加来代替乘法。

利用Richard Schreier提供的Matlab Delta-sigma调制器设计工具

包得到带外增益为6.1,DSM的NTF为

2.3 Verilog语言行为级建模

图2所示的是一种单路差异积分器调制器,可用延迟积分器和非延迟

积分器,以及各种前馈和反馈路径组合而成。在Matlab结构中对应

的积分器转换成Verilog硬件描述框图的过程如图3所示

本文使用Verilog硬件语言来实现单回路差异积分调制器,由时钟控

制构成延迟积分器与非延迟积分器的相加动作。assign指令使等式

两边永远处于活动状态,而alwavs指令将会在时钟正好触发时将sum

的值存入寄存器delay_sum中,因此,所有的积分器将会在每一次时

钟完成时完成一次累加动作。同理,非延迟积分器是由相同的程序代

码组成。实现延迟积分器的程序部分代码如下表示:

3 模型的仿真结果

图3给出的是NTF的极点与零点图。很明显,NTF的零点均匀地分布

在信号基带中,而不是集中在直流频率处。图4给出了输入幅度范围

与SNR。图5给出了NTF和STF的幅频响应。可以看到,带内信号的

衰减几乎是0,而图6显示噪声的衰减小于-110dB,满足带内噪声的要

求。图7给出了调制器的频域特性图。图8给出的是在输入为42000,

时钟频率为8.4MHz的verilog硬件描述语言的仿真结果,可以看出

经过2μs后结果趋于稳定。

4 结论

本文提出一个用在ADC中的16位的3阶8级量化的三阶单环

Delta-sigma调制器。为了提高电路性能,实现较高的SNR和DR,减

少量化噪声的影响,在设计NTF时采用前馈方式和局部反馈的结构,

并进行零点优化,通过这些方法优化了输出SNR,提高DR,降低量化

噪声,使得电路对于量化噪声有较好的敏感度。根据仿真结果,这个

DSM的峰值SNR可以达到145dB以上,在3阶的系统和128的过采样率

下,达到相当高的SNR,之后用Verilog语言对调制器各电路模块进

行建模与仿真。

Richard Schreier提供的Matlab Delta-sigma调制器设计工具包