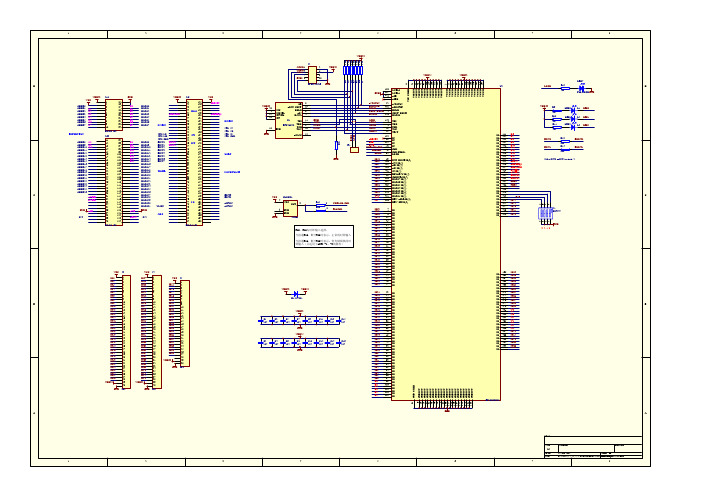

FPGA 原理图_设计必备

FPGA2410电路原理图

VDD33

VDD25 D1 1N4001

B

VDD33 C1 104 C3 104 C5 104 C7 104 GND VDD25 C2 104 C4 104 C6 104 C8 104 GND C10 104 C12 104 C14 104 C16 104 C9 104 C11 104 C13 104 C15 104

VDD33

R9 2K R10 2K R11 2K

LED0 LED1 LED2

L1 L2 L3

LED0 LED1 LED2

IIS BUS

TDI TDO EPC2LC20 TCK GND TMS nCASC

JP1 2 1

UART GND

TIMER

NAND FLASH

EINT9 EINT8 nXPON nYPON

1

2

3

பைடு நூலகம்

4

5

6

7

8

VDD33 J2 ATCK 1 ATDO 3 ATMS 5 7 ETDI 9 D 2 4 6 8 10 FPGA-JTAG VDD33 VDD25 R1 R2 R3 R4 R5 R6 R7 77 GND 21 33 48 72 91 106 124 130 152 185 201 VDD33 5 22 34 42 66 84 98 110 118 138 146 165 178 194 LED4 U2 GND VDD33 VCC ADDR0 ADDR1 ADDR2 ADDR3 ADDR4 ADDR5 ADDR6 ADDR7 EXPORT BUS J1B ADDR8 A8 ADDR9 A9 ADDR10 A10 ADDR11 ADDR12 ADDR13 ADDR14 ADDR15 ADDR16 ADDR17 ADDR18 ADDR19 ADDR20 ADDR21 ADDR22 ADDR23 ADDR24 ADDR25 ADDR26 C nWBE0 nWBE1 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 DIMM-168 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 D8 D9 D10 D11 D12 D13 D14 D15 DATA8 DATA9 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 DATA16 DATA17 DATA18 DATA19 DATA20 DATA21 DATA22 DATA23 DATA24 DATA25 DATA26 DATA27 DATA28 DATA29 DATA30 DATA31 GND ADC nGCS4 CS2 A1 A2 A3 A4 A5 A6 A7 J1A 1 2 3 4 5 6 7 8 9 10 DIMM-168 SPI0-MI SPI0-MO SPI0-CLK EINT0 EINT0 EINT1 EINT1 EINT2 EINT3 EINT4 EINT5 EINT6 EINT7 85 86 87 88 89 90 91 92 93 94 GND D0 D1 D2 D3 D4 D5 D6 D7 DATA0 DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 VDD33 J1C 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 125 126 127 128 DMA 129 130 131 132 133 134 135 136 SPI 137 138 139 INT 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 I/O 161 162 163 164 165 166 167 168 VCC nRESET VDD33 20 5 14 18 IIC BUS SPI1-SS SPI1-SO SPI1-SI SPI1-CLK 10 GND VCC VCCSEL VPPSEL VPP OE nINIT_CONF DCLK nCS DATA U1 8 13 4 9 2 11 1 3 19 12 R8 1K ETDI ATDI ATCK ATMS ETDI ATDI nSTATUS nCONFIG DCLK CONF_DONE DATA0 ATDI ATDO ATCK ATMS ATRST nRESET nOE nWE NORMAL CLK PLLCLK LOCK IO50 IO65 IO67 IO63 IO64 IO53 IO59 IO88 IO87 IO85 IO84 IO82 IO81 IO80 A10 A9 IO62 IO61 IO60 IO58 IO57 IO56 IO55 IO54 IO52 IO51 IO49 IO48 IO47 IO46 IO45 IO44 IO43 IO42 IO41 IO40 IO39 IO38 IO37 IO36 IO35 IO34 IO33 IO32 IO31 IO30 IO29 IO28 IO27 IO26 IO25 IO24 IO23 IO22 IO21 IO20 IO19 IO18 IO17 IO16 IO15 IO14 IO13 IO12 IO11 IO10 IO9 IO8 IO7 IO6 IO5 IO4 IO3 IO2 IO1 IO0 D0 D1 D2 D3 D4 D5 MSEL0 MSEL1 nCE nCEO VCC_CKLK 108 107 154 3 52 105 155 2 156 153 4 1 50 51 182 80 184 78 183 79 62 19 206 204 208 207 16 10 166 164 162 161 159 158 157 180 186 7 8 9 11 12 13 14 15 17 18 24 25 26 27 28 29 30 31 36 37 38 39 40 41 44 45 46 47 53 54 55 56 57 58 60 61 63 64 65 67 68 69 70 71 73 74 75 83 85 86 87 88 89 90 92 93 94 95 96 97 99 100 101 102 103 104 VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT LOCK R12 2K PLL LOCK GND D 1K 1K 1K 1K 1K 1K 1K

FPGA结构与工作原理新

概述

Altera的FLEX10K系列器件是一 款低成本高性价比的FPGA.

结构

●嵌入式阵列块(EAB) ●逻辑阵列块(LAB) ●快速通道(Fast Track)互联 ●I/O单元(IOE)

每个FPGA包含一个实现 存储和专用逻辑功能的嵌入 阵列和一个实现一般功能的 逻辑阵列.

逻辑单元(LE)

FPGA结构里最小的逻辑单元。

3.7 编程与配置

目前的PLD的编程工艺有3种:

1,基于电可擦除存储单元的EEPROM或Flash技术。 CPLD一般使用此技术进行编程(progam).cpld被编程后

改变了电可檫除存储单元的信息,掉电后可保持.

2,基于SRAM查找表的编程单元。 对于该类器件,编程信息是保 持在SRAM中的,掉电后信息

存储器功能:可构成RAM、ROM、FIFO RAM 和双端口 RAM。

图2-38 LAB阵列

FPGA 和 CPLD 的开发选择

主要是看开发项目本身的需要。 对于普通规模且产量不是很大的产品项目,使用CPLD较好。 对于大规模的逻辑设计如ASIC设计或单片系统设计,多采用FPGA。

CPLD 1,中小规模,CPLD价格较便宜,能直接用于系统。 2,开发CPLD的EDA软件容易得到。 3,CPLD的结构大多为EEPROM或FLASH ROM形式,编程后即 可固定下载的逻辑功能,使用方便,电路简单。 4,CPLD中有专门的布线区和许多块。Pin—to—pin信号延时几乎 固定,与设计无关。使得设计中毛刺现象易处理。

图3.8 实例图 A,B,C,D由FPGA芯片的管脚输入后进入可编程连线,然后作为地 址线连到LUT,LUT中已经事先写入了所有可能的逻辑结果,通 过地址查找到相应的数据然后输出,这样组合逻辑就实现了,该 电路中D触发器是直接利用LUT后面D触发器来实现。时钟信号 CLK由I/O脚输入后进入芯片内部的时钟专用通道,直接连接到触 发器的时钟端。触发器的输出与I/O脚相连,把结果输出到芯片管 脚。这样FPGA就完成了图3.8所示电路的功能。(以上这些步骤都 是由软件自动完成的,不需要人为干预)

【精品博文】基于FPGA的原理图PCB设计

【精品博文】基于FPGA的原理图PCB设计我的开发工具:Cadence 16.6,所用FPGA为Altera家的。

画FPGA原理图需准备以下资料:(1) 原理图库文件(2) 芯片手册(3) Pin out file原理图库文件可以从官网上下载,比如我用cadence画Altera家EP4CE115F29I7N原理图,就直接下载EP4CE115.OLB文件。

https:///support/support-resources/download/board-layout-test/pcb/pcb-cadence.html原理图中,这种大量管脚的芯片一般分为多个part,包括电源、地、各个bank、配置等。

芯片手册几乎给出了关于这个芯片设计(Cyclone IV Device Handbook)的所有需注意的问题,包括配置方式、全局时钟网络、专用时钟接口、lvds接口等。

pin out file中有每个管脚的详细说明。

(1)芯片配置配置方式主要有JTAG 或AS模式我只预留JTAG接口,有些板子上预留了两个下载接口,一个JTAG,用于下载程序,一个AS,用于固化程序,感觉这样很麻烦,我在固化时选择JIC(JTAG Indirect Configuration File)文件,尽管相对于AS模式会固化程序会慢一点,但毕业还是JTAG方式,这样就省去了烦琐的AS模式。

JTAG方式有用的信号其实就4个:TCK(测试时钟)、TDO(测试数据输出)、TMS(测试模式选择)、TDI (测试数据输入),再加上VCC和GND,共6根线,所以其实可以把标准10pin下载口简化为6pin,标准10pin下载口体积大,而6pin连接器可以自己选择,这样更方便。

nConfig、nStatus、CONF_DONE、TMS、TDI需要上拉,TCK需要下拉。

配置芯片一般为EPCS系列,如EPCS64,EPCS128,相应地,可以用ST公司的M25P64和M25P128代替,连接方式如下图所示。

CPLDFPGA 与ASIC原理与设计

绪论

现在,由于FPGA技术的快速发展, FPGA产品在逻辑密度、性能和功能上有 了极大的提高,同时器件成本也大幅下降, 可编程逻辑技术已经能与ASIC(专用集成 电路)和ASSP(专用标准产品)争夺市场, 并逐渐呈现出取代ASIC和ASSP的趋势。

返回

绪论

1.3 EDA技术的基本设计方法

1 .数字电路设计的基本方法

绪论

2. EWB仿真软件

EWB(Electronic Workbench)软件是Interactive ImageTechnologies Ltd 在20世纪90年代初推出的电路仿 真软件。目前普遍使用的是EWB5.2,相对于其它EDA 软件,它是较小巧的软件(只有16M)。但它对模数电 路的混合仿真功能却十分强大,几乎100%地仿真出真 实电路的结果,并且它在桌面上提供了万用表、示波器、 信号发生器、扫频仪、逻辑分析仪、数字信号发生器、 逻辑转换器和电压表、电流表等仪器仪表。它的界面直 观,易学易用。它的很多功能模仿了SPICE的设计,但 分析功能比PSPICE稍少一些。

系统分解 单元设计 功能模块划分 子系统设计 返回 系统集成

Top-down 行为设计 结构设计 逻辑设计 电路设计 版图设计

绪论

3. CPLD/FPGA设计流程

只要有数字电路的基础,还是能较容易 和快速地学会利用CPLD/FPGA设计数字系 统的。数字系统的基本部件比较简单,它们是 一些与门、或门、非门、触发器、多路选择 器等,宏器件也是一些加法器、乘法器等。

专家认为,IC发展的大趋势是高速、高集成度和低功耗的系统。

返回

绪论

集成片上系统的优点:

实现高速运作、缩短产品的上市时间、 降低功耗和减少所占的PCB空间、提高系统 的可靠性、它可使电子系统的尺寸更小、性 能更高和成本更低,同时整个系统的抗干扰 特性与可靠度将提高。

EP1C3T144FPGAdevelopboardmanual(开发板原理图)

EP1C3T144FPGAdevelopboardmanual(开发板原理图)FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led 可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

第三章 FPGA原理图输入设计法

3.1 原理图设计方法

2.编辑规则 引脚名称 :不区分大小写,不超过32个字符 节点名称:即给单条连线命名 总线名称:一条总线至少代表2个节点的组合,最 多为256个节点。命名时,必须在名称后加上 [m..n]表示其含有的节点变化 文件名称:扩展名.bdf,文件名最长32个字符 项目名称:项目包含所有的从设计文件编译后产 生的文件。项目名必须与顶层设计文件名相同

3.2 3-8译码器的设计

三个输入端,八个输出端。 当输入信号按二进制方式的表示值为十进 制数N时,标号为N的输出端输出高电平, 表示有信号产生,而其它输出端则为低电 平,表示无信号产生。 三个输入端能产生的组合状态有八种,所 以输出端在每种组合中仅有一位为高电平 的情况下,能表示所有的输入组合。

3.1 原理图设计方法

完全的编译:包括编译,网表输出, 综合,配置器件

--编译器除了完成以上的步骤,还要将 设计配置到ALTERA的器件中去 --编译器根据器件特性产生真正的延时 时间和给器件的配置文件

3.1 原理图设计方法

②引脚适配 在指配编辑器中进行指定 Assignments/Assignments Editor 编辑指配文件(.qsf——Quartus II Settings File)

3.1 原理图设计方法

③项目仿真 功能仿真 前仿真,对设计的逻辑功能进行仿真; 时序仿真 后仿真,对信号的时间延时进行仿真;

仿真前还要做的工作 • 输入信号的建立

3.1 原理图设计方法

④仿真波形文件的建立 Vector Waveform File (.vwf) --创建矢量波形文件; --设定时间轴参数; --选择需仿真的节点; --编辑输入节点的仿真波形;

3.1 原理图设计方法

教学课件第1章FPGA系统设计基础

1.1.2 可编程逻辑器件的编程器件工作原理

可编程逻辑器件按照编程工艺又可分为4 个种类:(l)熔丝(Fuse)或反熔丝 (Antifuse)编程器件;(2)UEPROM编程 器件;(3)EEPROM编程器件;(4) SRAM编程器件。前3类器件称为非易失 性器件,它们在编程后,配置数据保持 在器件上;第4类器件为易失性器件,每 次掉电后配置数据会丢失,因而在每次 上电时需要重新进行数据配置。

5. 随机存储器(RAM)

随机存储器也叫随机读/写存储器,简称RAM。 在RAM工作时可以随时从任何一个指定地址读 出数据,也可以随时将数据写入任何一个指定 的存储单元中去。它的优点是读、写方便,使 用灵活。缺点是一旦断电以后所存储的数据将 随之丢失,即存在数据易失性的问题。RAM电 路通常由存储矩阵、地址译码器和读/写控制 电路(也叫输入/输出电路)几部分组成,电 路结构框图如图所示。

1.可编程只读存储器(PROM)

熔丝(Fuse)或反熔丝(Antifuse)编程 器件采用PROM结构。PROM的总体结构 与掩模ROM相同,所不同的是在出厂时 已经在存储矩阵的所有交叉点上全部制 作了存储元件。存储元件通常有两种电 路形式:一种是由二极管组成的结破坏 型电路;另一种是由晶体三极管组成的 熔丝型电路,结构示意图如图所示。

最早研究成功并投入使用的EPROM是用 紫外线照射进行擦除的,并被称之为 EPROM。因此,现在一提到EPROM就是 指的这种用紫外线擦除的可编程 ROM (Ultra-Violet Erasable Programmable Read-Only Memory,简称 UVEPROM)。

EPROM采用MOS型电路结构,其存储单 元通常由叠栅型MOS管组成。叠栅型 MOS管通常采用增强型场效应管结构。 叠栅注入 MOS管(Stacked-gate Injection Metal-Oxide-Semiconductor, 简称SIMOS管)的结构原理图和符号如 图所示。

精品课件-Xilinx FPGA设计基础-第3章

实体中所有的端口信号都要在“port();”语句的括号内 声明。端口的声明包含三个部分:端口名称、端口模式和数据 类型。相同端口模式和数据类型的端口信号可以作为一组信号 联合声明,信号之间用逗号“,”隔开,不同组的信号声明之 间用分号“;”隔开,但是要注意声明最后一组信号后不需要 再加分号,端口声明的结构如下:

第3章 VHDL硬件描述语言

3.3.1 实体 设计一个模块,首先要给模块起一个名字作为这个模块的

标识,称为实体名称。这个名字通常与模块的功能有密切关系, 例如2.2节实验中的AND_OR。

模块命名后,就要确定这个模块的外部接口参数,即模块 有哪些输入信号,有哪些输出信号,信号的名称和类型是什么, 在确定了这些参数之后,我们就完成了对实体的描述。

第3章 VHDL硬件描述语言

1.端口名称 一般一个模块实体包含不止一个端口,为了区别不同的端 口,给端口命名时通常不会采用上面例子中的方式,而会将端 口的含义包含在名称中。例如,常用的端口名称“clk”表示 时钟信号等。 2.端口模式 端口模式用于定义模块端口的数据传输模式。VHDL的端 口模式有五种,如表3.1所示。

第3章 VHDL硬件描述语言

VHDL只是给工程师提供了一个描述规范,用这种规范进 行描述可以使众多工程师之间传递信息更加简洁、准确。学习 VHDL就是学习如何利用这些规范进行描述,因此,我们在学 习VHDL之前,要在思维中假想一个现成的芯片,学习的过程 中,对照芯片不断完善对芯片的描述。

VHDL不仅可以对芯片的接口和行为参数做详尽的描述, 而且可以作为一门编程语言对可编程逻辑器件进行编程配置。 目前,可编程逻辑器件的EDA工具都支持以VHDL代码作为工程 设计的输入。

FPGA应用板原理图的绘制过程

FPGA应用板原理图的绘制过程1. 概述原理图是FPGA应用板设计的核心部分之一,它展示了电路元件之间的连接和关系。

本文档将介绍FPGA应用板原理图的绘制过程,包括准备工作、元件选择、连线设计等内容。

2. 准备工作在开始绘制FPGA应用板原理图之前,我们需要进行一些准备工作。

2.1 确定设计目标首先,我们需要明确FPGA应用板的设计目标。

这包括板载元件的种类、数量、功耗要求等。

明确设计目标可以帮助我们合理选择元件和进行连线设计。

2.2 选定EDA工具绘制FPGA应用板原理图需要使用电子设计自动化(EDA)工具。

常用的EDA工具有Altium Designer、Cadence Allegro等。

根据自己的经验和需求选择合适的工具进行原理图绘制。

2.3 确定板子尺寸和层数FPGA应用板的尺寸和层数也需要提前确定。

这对于元件的布局和连线设计有很大影响。

根据设计目标和需求确定FPGA应用板的尺寸和层数。

3. 元件选择在绘制FPGA应用板原理图时,我们需要选择合适的元件进行设计。

以下是元件选择的一些建议:•FPGA芯片:选择合适的FPGA芯片,根据设计目标选择性能和功耗合适的芯片。

•时钟元件:根据电路的时钟需求选择合适的时钟元件。

•通信接口元件:根据应用板需要支持的通信接口选择合适的通信接口元件,如UART、SPI、I2C等。

•存储器元件:根据应用板的存储器需求选择合适的存储器元件,如SDRAM、FLASH等。

4. 连线设计连线设计是FPGA应用板原理图绘制的重要环节。

以下是连线设计的一般步骤:4.1 确定信号流向首先,需要明确信号的流向。

根据FPGA的电路原理和信号需求,确定信号是从哪个元件输出,到哪个元件输入。

4.2 连接引脚根据信号的流向,连接各个元件的引脚。

需要注意的是,引脚的连接应该符合元件的规格要求和电气特性。

4.3 划分电源和地线为了保证电路的可靠性和稳定性,需要划分电源和地线。

在绘制原理图时,可以使用特殊的符号来表示电源和地线。

STM F VET 开发板原理图

41 39

RX_ER/MDIX_EN

RX_DV/MII_MODE

38 RX_CLK

42 COL/PHYAD0

40 CRS/CRS_DV/LED_CFG

17

TD+

16

TD-

14

RD+

RD- 13

NC

12 11

NC

NC 10

9

NC

8

NC

5

4

6

3

7

2

8

1

RN3

R31 240

30 R32 240

3.3V

1 4 2

5 Vref

TJA1050

CAN2H 2 1

JP5 R43 120R

CAN2L

A

Title

Size C

Date: File:

Number

Revision

2-Jun-2016

Sheet of

E:\板子工程文件\STM32F407板子\电路图\SDTraMw3n2FB4y0:7\STM32F407.ddb

15 47

IOGND IOGND

35

C17

C18

C19

100nF 100nF 100nF

23

36

PFBOUT

DGND

HR911105A

DP83848

1

2

3

4

JP2 USB接口信号,即是DP与DM信号,分别对应于D+与D-

PA11-USB-DM R36

22

PA12-USB-DP R37

22

5V

J4

1 VBUS

RO

8 VCC

2 RE