实验三 序列信号发生器与检测器设计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三序列信号发生器与检测器设计

一、实验目的

1.学习一般有限状态机的设计;

2.实现串行序列的设计。

二、设计要求

1.先设计0111010011011010序列信号发生器;

2.再设计一个序列信号检测器,若系统检测到串行序列11010则输出为“1”,否则输出为“0”,并对其进行仿真和硬件测试。

三、实验设备

PC机,Quartu eⅱ软件,实验箱

四、实验原理

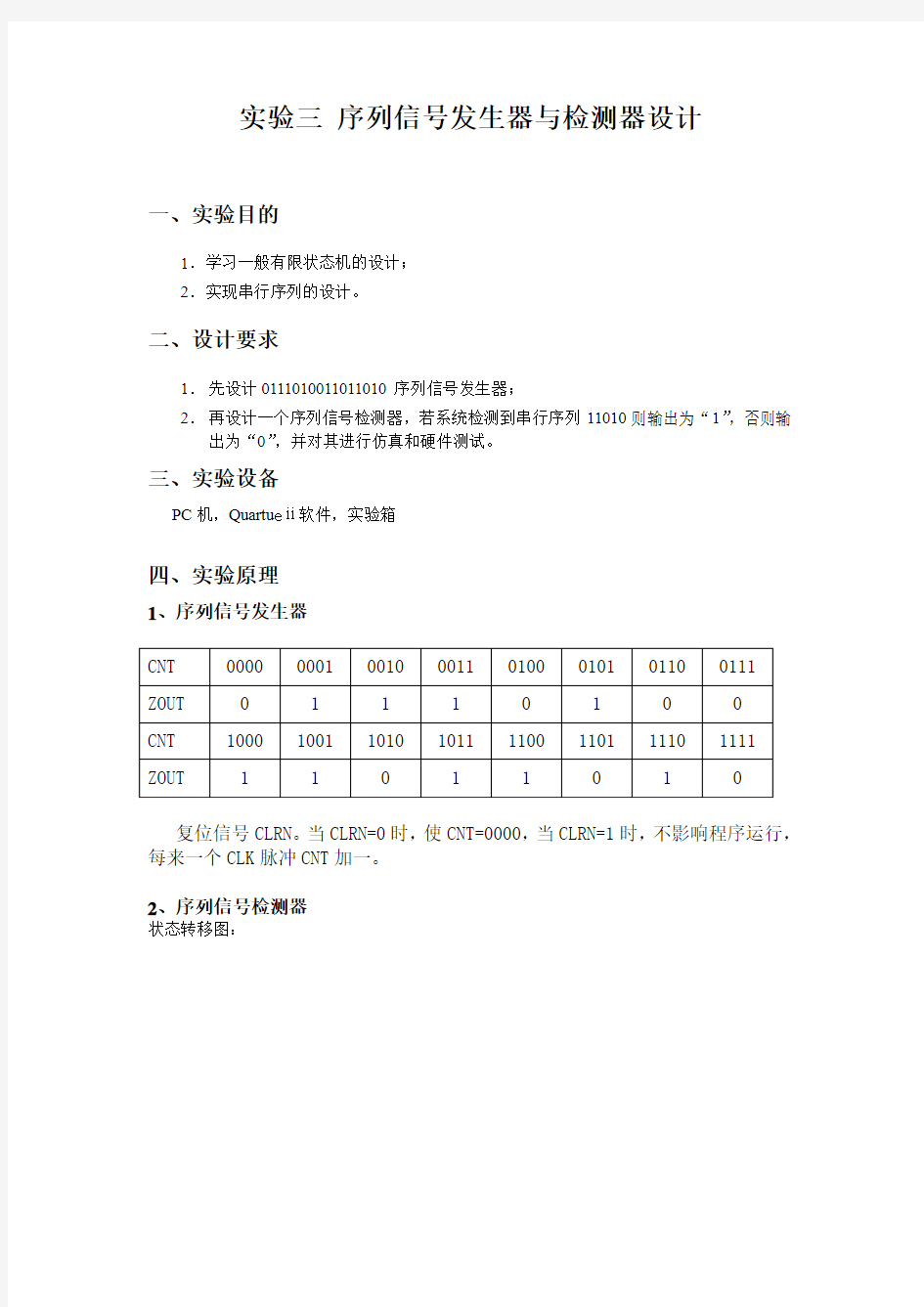

1、序列信号发生器

复位信号CLRN。当CLRN=0时,使CNT=0000,当CLRN=1时,不影响程序运行,每来一个CLK脉冲CNT加一。

2、序列信号检测器

状态转移图:

五、实验步骤

1、信号发生器

1)建立工作库文件夹,输入设计项目VHDL代码,如下:

L I B R A R Y I E E E;

U S E I E E E.S T D_L O G I C_1164.A L L;

U S E I E E E.S T D_L O G I C_A R I T H.A L L;

U S E I E E E.S T D_L O G I C_U N S I G N E D.A L L;

E N T I T Y X L S I G N A L16_1I S

P O R T(C L K,C L R N:I N S T D_L O G I C;

Z O U T:O U T S T D_L O G I C);

E N D X L S I G N A L16_1;

A R C H I T E C T U R E o n e O F X L S I G N A L16_1I S

S I G N A L C N T:S T D_L O G I C_V E C T O R(3D O W N T O0);

S I G N A L Z R E G:S T D_L O G I C;

B E G I N

P R O C E S S(C L K,C L R N)

B E G I N

I F(C L R N='0')T H E N C N T<="0000";E L S E

I F(C L K'E V E N T A N D C L K='1')T H E N

C N T<=C N T+'1';

E N D I F;

E N D I F;

E N D P R O C E S S;

P R O C E S S(C N T)

B E G I N

C A S E C N T I S

W H E N"0000"=>Z R E G<='1';

W H E N"0001"=>Z R E G<='1';

W H E N"0010"=>Z R E G<='1';

W H E N"0011"=>Z R E G<='0';

W H E N"0100"=>Z R E G<='0';

W H E N"0101"=>Z R E G<='1';

W H E N"0110"=>Z R E G<='0';

W H E N"0111"=>Z R E G<='1';

W H E N"1000"=>Z R E G<='0';

W H E N"1001"=>Z R E G<='1';

W H E N"1010"=>Z R E G<='0';

W H E N"1011"=>Z R E G<='0';

W H E N"1100"=>Z R E G<='1';

W H E N"1101"=>Z R E G<='0';

W H E N"1110"=>Z R E G<='1';

W H E N"1111"=>Z R E G<='1';

W H E N O T H E R S=>Z R E G<='0';

E N D C A S E;

E N D P R O C E S S;

Z O U T<=Z R E G;

E N D o n e;

2)对其进行波形仿真,如下图:

3)将其转换成可调用元件如图:

2、信号检测器

1)建立工作库文件夹,输入设计项目VHDL代码,如下:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT(DIN, CLK, CLR : IN STD_LOGIC;

ss : OUT STD_LOGIC_VECTOR

END SCHK;

ARCHITECTURE behav OF SCHK IS

SIGNAL Q : INTEGER RANGE 0 TO 5 ;

SIGNAL D : STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

D <= "10010" ;

PROCESS( CLK, CLR )

BEGIN

IF CLR = '1' THEN Q <= 0 ;

ELSIF CLK'EVENT AND CLK='1' THEN

CASE Q IS

WHEN 0=> IF DIN = D(4) THEN Q <= 1 ; ELSE Q <= 0 ; END IF ; WHEN 1=> IF DIN = D(3) THEN Q <= 2 ; ELSE Q <= 1 ; END IF ; WHEN 2=> IF DIN = D(2) THEN Q <= 3 ; ELSE Q <= 1 ; END IF ; WHEN 3=> IF DIN = D(1) THEN Q <= 4 ; ELSE Q <= 0 ; END IF ; WHEN 4=> IF DIN = D(0) THEN Q <= 5 ; ELSE Q <= 1 ; END IF ; WHEN OTHERS => Q <= 0 ;