74ls160组成n进制计数器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验7 74ls160组成n进制计数器

一、实验内容

1.掌握集成计数器的功能测试及应用

2.用异步清零端设计6进制计数器,显示选用数码管完成。

3.用同步置0设计7进制计数器,显示选用数码管完成。

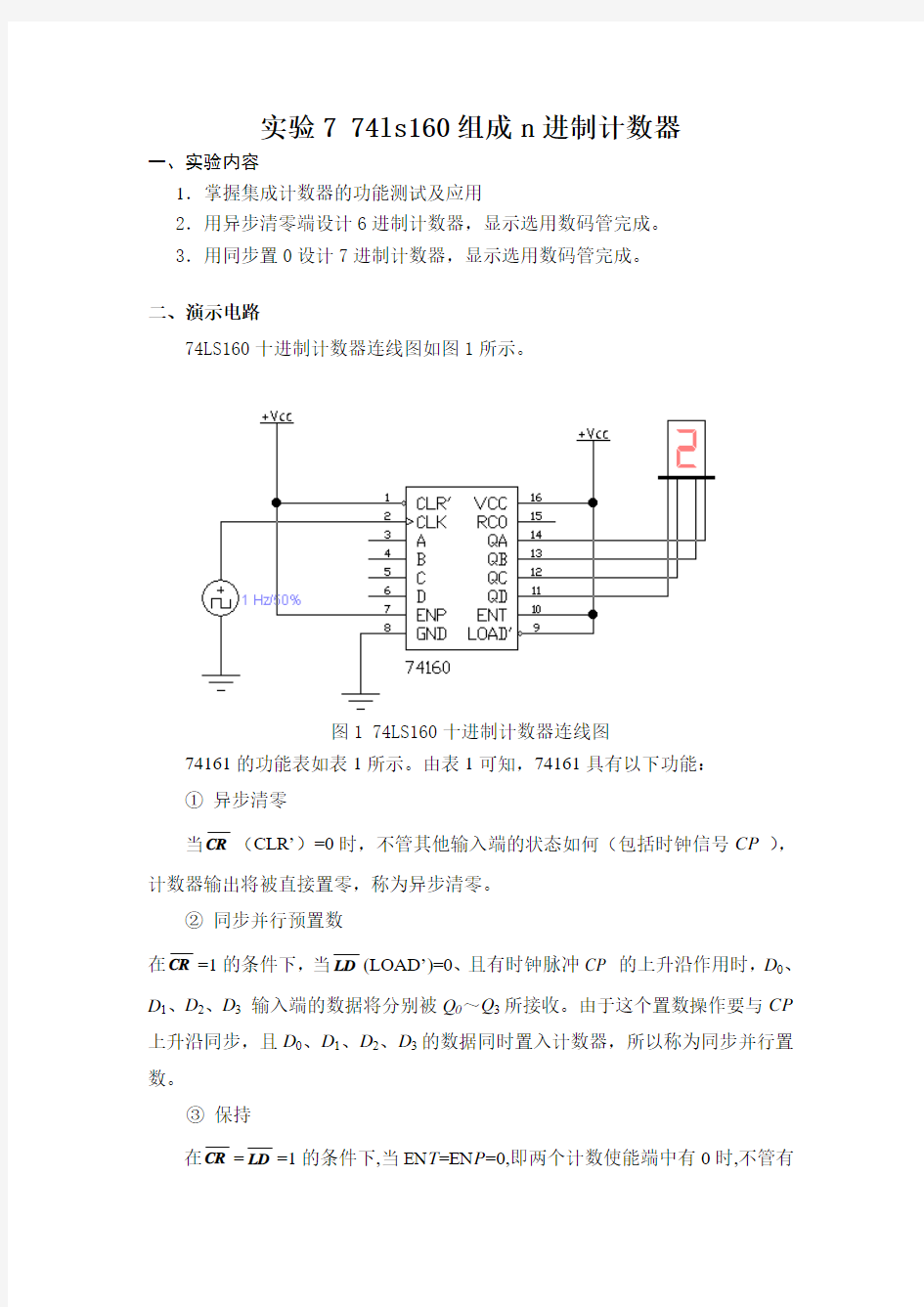

二、演示电路

74LS160十进制计数器连线图如图1所示。

图1 74LS160十进制计数器连线图

74161的功能表如表1所示。由表1可知,74161具有以下功能:

①异步清零

当CR(CLR’)=0时,不管其他输入端的状态如何(包括时钟信号CP),计数器输出将被直接置零,称为异步清零。

②同步并行预置数

在CR=1的条件下,当LD(LOAD’)=0、且有时钟脉冲CP 的上升沿作用时,D0、D1、D2、D3输入端的数据将分别被Q0~Q3所接收。由于这个置数操作要与CP 上升沿同步,且D0、D1、D2、D3的数据同时置入计数器,所以称为同步并行置数。

③保持

在CR=LD=1的条件下,当EN T=EN P=0,即两个计数使能端中有0时,不管有

无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当EN P =0, EN T =1时,进位输出C 也保持不变;而当ENT=0时,不管EN P 状态如何,进位输出RCO=0。 ④ 计数

当CR =LD =EN P =EN T =1时,74161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路将从1111状态返回到0000状态,R CO 端从高电平跳变至低电平。可以利用R CO 端输出的高电平或下降沿作为进位输出信号。

表1 74161的功能表

输入

输出

CP CR LD P T D 0 D 1 D 2 D 3

Q 0 Q 1 Q 2 Q 3 × 0 × × × × × × × 0 0 0 0

↑ 1 0 × × a b c d a b c d

× 1 1 0 1 × × × × 保持 × 1 1 × 0 × × × × 保持(C =0) ↑ 1 1 1 1 × × × ×

计数

连上十进制加法计数器160,电路如图1所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

三、用160和与非门组成6进制加法计数器-用异步清零端设计

74160从0000状态开始计数,当输入第6个CP 脉冲(上升沿)时,输出Q 3 Q 2 Q 1 Q 0=0110,此时=0,反03Q Q CR =馈给端CR 一个清零信号,立即使Q 3 Q 2 Q 1 Q 0返回0000状态,接着,CR 端的清零信号也随之消失,74160重新从0000状态开始新的计数周期。

反馈归零逻辑为代码中为1的Q 相与非。n n Q Q CR 12=

电路如图2所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

图2 用异步清零端设计

四、用160和与非门组成7进制加法计数器-用同步置零设计

计数器从Q 3Q 2Q 1Q 0=0000开始计数,当第6个CP 到达后,计到0110,此时

LD

=12Q Q =0。并不能立即清零,而是要等第7个脉冲上沿到来后,计数器被置

成0000。不会用异步清零端那样出现0110过渡状态,这是与用异步清零端的差别。用同步清零端设计计数器如图3所示,如n n Q Q LD 12 ,则为七进制计数器。

图3 同步清零端设计计数器

五、实验报告

1. 实验名称、内容和实验电路。

2. 画出用160和与非门组成6进制加法计数器的状态转换图。

3.画出同步清零端设计的七进制计数器的状态转换图。说明同步置0与异步清零的区别?

六、讨论与思考

如何用74ls162设计七进制计数器?