74ls160构成n进制计数器应用

74ls160做60进制计数器原理及实验步骤 -回复

74ls160做60进制计数器原理及实验步骤-回复74LS160是一种常见的集成电路,可以用来制作60进制计数器。

本文将详细介绍74LS160计数器的原理和实验步骤,并按步骤回答相关问题。

第一部分:74LS160计数器原理1. 什么是74LS160计数器?74LS160是一种同步4位可二进制或BCD(二进制编码十进制)计数器。

BCD是一种将十进制数字表示为4位二进制码的编码系统。

2. 工作原理是什么?74LS160计数器通过输入脉冲信号来实现计数,并将结果以二进制或BCD的形式输出。

它有一个异步复位输入和一个同步使能输入。

当复位输入为低电平时,计数器的值将被重置为0。

当使能输入为高电平时,计数器开始计数。

计数器的值可以通过输出引脚读取。

3. 如何将74LS160配置为60进制计数器?在将74LS160配置为60进制计数器之前,首先需要将它设置为BCD 计数器。

然后,在BCD计数器的基础上,添加逻辑电路来实现60进制计数。

4. 如何实现BCD计数?将74LS160配置为BCD计数器很简单。

首先,将使能输入(ENABLE)连接到高电平,以确保计数器始终处于计数状态。

然后,将复位输入(CLEAR)连接到低电平,以将计数器的初始值重置为0。

最后,将时钟输入(CLK)连接到外部时钟源。

5. 如何实现60进制计数?要实现60进制计数,我们需要添加一个逻辑电路来增加计数器的位数。

由于74LS160只是一个4位计数器,我们需要使用多个74LS160并联来扩展位数。

例如,如果我们想要一个6位的60进制计数器,我们可以使用两个74LS160,并将第二个计数器的CLK输入连接到第一个计数器的某个输出引脚。

第二部分:74LS160计数器实验步骤1. 准备材料- 1个或多个74LS160计数器芯片(取决于所需的位数)- 逻辑门IC(用于扩展位数)- 面包板- 连接线- 4个LED(用于将计数器结果显示出来)- 电源(通常为5V)2. 连接电路首先,将74LS160芯片插入面包板中。

74LS160中文资料

个高电平脉冲,其宽度为 Q0 的高电平部分。

m 在不外加门电路的情况下,可级联成 N 位同步计数器。

对于 54/74LS160,在 CP 出现前,即使 CEP、CET、/MR 发生变化,

/ 电路的功能也不受影响。

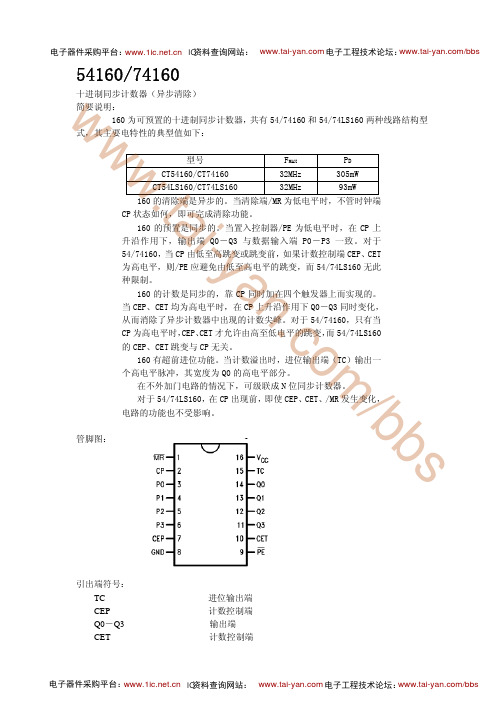

bbs 管脚图:

引出端符号: TC CEP Q0-Q3 CET

进位输出端 计数控制端 输出端 计数控制端

升沿作用下,输出端 Q0-Q3 与数据输入端 P0-P3 一致。对于

i- 54/74160,当 CP 由低至高跳变或跳变前,如果计数控制端 CEP、CET

y 为高电平,则/PE 应避免由低至高电平的跳变,而 54/74LS160 无此

种限制。

a 160 的计数是同步的,靠 CP 同时加在四个触发器上而实现的。

w 型号

FMAX

PD

w CT54160/CT74160

32MHz

305mW

CT54LS160/CT74LS160

32MHz

93mW

.160 的清除端是异步的。当清除端/MR 为低电平时,不管时钟端

tCP 状态如何,即可完成清除功能。

a 160 的预置是同步的。当置入控制器/PE 为低电平时,在 CP 上

80

40

40

40 μA

40

20

VIL 输 入 低电平电 流

CP,CET /PE

P0-P3,CEP,/MR

Vcc=最大

VIL=0.4V

-3.2

-0.8

-1.6

-0.8 mA

-1.6

-0.4

IOS 输出短路电流 IccH 输出高电平时电源电流

Vcc=最大

54 -20 -57 -20 -100 mA

74LS160-153的管脚图

1.74LS160逻辑功能测试74LS160是中规模集成同步十进制加法计数器,具有异步清零和同步预置数的功能。

使用74LS160通过置零法或置数法可以实现任意进制的计数器。

其引脚图见图4-9-1。

先对74LS160的基本功能进行测试,并将计数器的工作状态填入表4-9-1中。

①异步清零:当D R =0时,Q 0=Q 1=Q 2=Q 3=0。

②同步预置:当LD =0时,在时钟脉冲CP 上升沿作用下,Q 0=D 0,Q 1=D 1,Q 2=D 2,Q 3=D 3。

③锁存:当使能端0EP ET =时,计数器禁止计数,为锁存状态。

④计数:当使能端EP =ET =1时,为计数状态。

表4-9-1 74LS160的逻辑功能表2.74LS160的应用(1)用两片74LS160和门电路构成24进制计数器(用复位法),要求译码显示,并显示数字为00-23的循环。

1)接成并行进位型。

设计电路并用数码显示验证计数功能,记录数码显示情况。

2)接成串行进位型。

设计电路并用数码显示验证计数功能,记录数码显示情况。

(2)用74LS160和门电路设计一个计数译码显示电路,要求计数显示为1-7。

实验验证电路功能,并用“逻辑电平测试”中的发光二极管观察CP 脉冲、Q 0、Q 1、Q 2状态的变化过程,把波形记录下来。

图4-9-1 74LS160引脚图3.74LS192的应用74LS192是中规模集成同步十进制可逆计数器,具有加法计数和减法计数双功能,分别由加法计数脉冲和减法计数脉冲控制;具有异步清零和异步预置数功能。

其详细功能表及芯片引脚图请参阅附录C相关内容。

用74LS192和门电路设计一个倒计时秒表的计数译码显示电路。

要求显示60~00,精度为1秒,标准秒脉冲由实验台的“TTL信号”代替,或自行设计电路产生秒脉冲信号。

验证其功能。

74ls153管脚图逻辑功能图封装:。

74ls160做60进制计数器原理及实验步骤 -回复

74ls160做60进制计数器原理及实验步骤-回复74LS160是一种常见的计数器芯片,它能够实现60进制的计数功能。

本文将介绍74LS160的原理以及实验步骤,帮助读者更好地理解和运用这种计数器芯片。

一、74LS160的工作原理74LS160是一种可编程时序器件,它内部包含了一个由主计数器和辅助计数器组成的计数器链。

这两个计数器均可设定为0至59之间的任意数值。

主计数器负责进行60进制的计数,而辅助计数器负责对主计数器进行增加或减少操作。

在开始计数之前,我们首先需要对74LS160进行编程。

通过将不同的输入信号引脚接地或连接高电平,我们可以设置主计数器和辅助计数器的起始值。

此外,还需设置计数器处于增加或减少模式、复位或不复位模式以及使能或禁用计数器。

当所有设置完成后,就可以开始进行计数操作了。

每当计数器达到设定的最大值时,它会自动回到起始值重新开始计数(这里是59)。

可以使用一个外部的信号来触发计数器的复位操作,实现对计数器的控制。

在实际应用中,我们可以通过连接74LS160输出引脚到其他器件或电路,来实现对计数结果的产生和运用。

例如,可以将计数结果连接到显示器上,直接显示出当前的计数值。

或者将计数结果连接到其他逻辑电路中,实现更复杂的功能。

二、实验步骤下面将详细介绍使用74LS160实现60进制计数的实验步骤。

在进行实验之前,我们需要准备以下器材和元件:74LS160芯片、电路板、连接线、几个脉冲开关和一台数字显示器。

1. 将74LS160芯片插入电路板上相应的位置。

确保芯片的引脚正确插入到电路板上的插座中。

可以参考芯片的管脚图或者电路板说明来确定正确的插入方式。

2. 使用连接线将芯片与其他器件进行连接。

首先,将芯片的电源引脚与电源连接,确保芯片能够正常工作。

接下来,将芯片的计数引脚与脉冲开关连接,以接收外部的计数触发信号。

最后,将芯片的输出引脚连接到数字显示器的相应输入端口上。

3. 设置芯片的工作模式。

基于74LS160的可控多进制计数系统设计与仿真

基于74LS160的可控多进制计数系统设计与仿真

季丽琴

【期刊名称】《智能计算机与应用》

【年(卷),期】2017(007)005

【摘要】本文在普通计数器设计原理的基础上,利用集成同步加法计数器74LS160设计出一个可控的多进制计数系统.利用拨码控制电路,该系统可以分别实现7进制、9进制和79进制计数功能,从而体现出该系统的可控性、灵活性和实用性.本文借助Mul-tisim10平台进行了仿真测试,验证了该系统的可行性.

【总页数】5页(P133-136,139)

【作者】季丽琴

【作者单位】苏州健雄职业技术学院电气工程学院, 江苏太仓215400

【正文语种】中文

【中图分类】TP391

【相关文献】

1.74LS160实现N进制计数器的方法和EWB仿真 [J], 王小方

2.基于74LS160的N进制计数器仿真设计 [J], 乔琳君

3.基于74LS160的可控多进制计数系统设计与仿真 [J], 季丽琴;

4.基于74LS112的同步五进制加法计数器的设计与仿真 [J], 季丽琴

5.十进制集成计数器74LS160的应用 [J], 李志平

因版权原因,仅展示原文概要,查看原文内容请购买。

74ls160

十进制同步计数器(异步清除) 简要说明:

160 为可预置的十进制同步计数器,共有 54/74160 和 54/74LS160 两种线路结构型 式,其主要电特性的典型值如下:

型号

FMAX

PD

CT54160/CT74160

32MHz

305mW

CT54LS160/CT74LS160

32MHz

4.5 5 5.5

4.75 5 5.25 4.75 5 5.25

2

2

0.8

0.7

0.8

0.8

-800

-400

16

4

16

8

单位

V V V μA mA

0

25

0

25

MHz

25

25

ns

20

20

P0-P3、CEP

20

20

建立时间tset

ns

/PE

25

20

保持时间tH

0

0

ns

逻辑图

平,其余输入接低电平

74

101

【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

31

32 mA

32

动态特性(TA=25℃)

参数【2】

测试条件

fmax

tPLH

CP->TC

tPHL

tPLH

CP->Q

Vcc=5V

tPHL

(/PE=H)

CL=15pF

tPLH

CP->Q

RL=400Ω

tPHL

(/PE=L)

管脚图:

引出端符号: TC CEP Q0-Q3 CET

74ls160十进制计数器原理

74ls160十进制计数器原理

74LS160十进制计数器原理74LS160是一种常用的十进制计数器,它能够实现0至9的循环计数。

它的原理基于二进制计数和锁存器的结合。

该计数器由四个D触发器组成,每个触发器都能存储一个二进制位。

在计数过程中,每当一个触发器的输出从低电平变为高电平时,它会向高位触发器传递一个脉冲信号。

这样,当最低位的触发器计数到9时,它会向高位触发器传递一个脉冲信号,使得高位触发器加1,而最低位触发器归零。

为了实现循环计数,74LS160还包含一个复位功能。

当外部信号复位输入为低电平时,所有触发器的输出都会被清零,计数器重新从0开始计数。

除了计数功能,74LS160还具有一个使能输入。

当使能输入为低电平时,计数器将会被禁用,不再进行计数。

这个功能可以用于控制计数器的启动和停止。

总结起来,74LS160十进制计数器通过二进制计数和锁存器的结合,实现了0至9的循环计数。

它具有复位和使能功能,可以灵活控制计数器的启动和停止。

这使得它在很多应用中都有广泛的使用,如时钟、计时器、频率分析等。

用异步清零端反馈归零构成N进制计数器

1 00 0 1

0

1 00 1 1

0

产生序列脉冲 Z= Q2 = 00111010

0 01 1 1

1

1 11 1 0

1

0 11 0 1

1

0 10 1 0

0

1 01 0 0

1

1 10 0 1

0

例5-23 已知脉冲分配器的两种输出波形分别如图5-68a、b所示, 试用MSI同步4位二进制加法计数器CT74LS161和3线-8线译码器 CT74LS138设计脉冲分配器,并画出它们的逻辑电路图。

74LS161

CO 1

LD

CP

CR

D0 D1 D2 D3 (a) 用异步清零端 CR 归零

D0~D3可随意处理

例 160异步清零,163同步清零

&

1 CTP Q0 Q1 Q2 Q3。CO

CTP 74LS160 LD

1

CP

D0 D1 D2 D3 CR

Q0 Q1 Q2 Q3

1 CTT CTP

CP

74LS163

方法一:预置数端复位法。 1、用同步置数控制端复位法构成N进制计数器

(1)写出状态SN-1的二进制代码。 (2)求归零逻辑,即求同步置数控制端信号的逻 辑表达式。 (3)画连线图。

2、用异步置数端复位法构成N进制计数器

(1)写出状态SN的二进制代码。 (2)求归零逻辑,即求异步置数控制端信号的逻辑 表达式。 (3)画连线图。

级联法或者级联加反馈归零容量扩展的两计数器直接级联可构成模n1n2的计数器加上整体反馈归零可构成n1n2之内的n进制计数器异步计数器一般没有专门的进位信号输出端通常可以用本级的高位输出信号驱动下一级计数器计数即采用串行进位方式来扩展容量

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验74ls160组成n进制计数器

一、实验内容

1.掌握集成计数器的功能测试及应用

2.用异步清零端设计6进制计数器,显示选用数码管完成。

二、演示电路

74LS160十进制计数器连线图如图1所示。

图1 74LS160十进制计数器连线图

74161的功能表如表1所示。

由表1可知,74161具有以下功能:

①异步清零

当CR(CLR’)=0时,不管其他输入端的状态如何(包括时钟信号CP),计数器输出将被直接置零,称为异步清零。

②同步并行预置数

在CR=1的条件下,当LD(LOAD’)=0、且有时钟脉冲CP 的上升沿作用时,D0、D1、D2、D3输入端的数据将分别被Q0~Q3所接收。

由于这个置数操作要与CP 上升沿同步,且D0、D1、D2、D3的数据同时置入计数器,所以称为同步并行置数。

③保持

在CR=LD=1的条件下,当EN T=EN P=0,即两个计数使能端中有0时,不管有无CP脉冲作用,计数器都将保持原有状态不变(停止计数)。

需要说明的是,当EN P=0, EN T=1时,进位输出C也保持不变;而当ENT=0时,不管EN P状态如

何,进位输出RCO=0。

④ 计数

当CR =LD =EN P =EN T =1时,74161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路将从1111状态返回到0000状态,R CO 端从高电平跳变至低电平。

可以利用R CO 端输出的高电平或下降沿作为进位输出信号。

连上十进制加法计数器160,电路如图1所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

三、用160和与非门组成6进制加法计数器-用异步清零端设计

74160从0000状态开始计数,当输入第6个CP 脉冲(上升沿)时,输出Q 3 Q 2 Q 1 Q 0=0110,此时03Q Q CR ==0,反馈给CR 端一个清零信号,立即使Q 3 Q 2 Q 1 Q 0返回0000状态,接着,CR 端的清零信号也随之消失,74160重新从0000状态开始新的计数周期。

反馈归零逻辑为代码中为1的Q 相与非。

n n

Q Q CR 12=

电路如图2所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

图2 用异步清零端设计

四、用160和与非门组成7进制加法计数器-用同步置零设计

计数器从Q 3Q 2Q 1Q 0=0000开始计数,当第6个CP 到达后,计到0110,此时

LD =12Q Q =0。

并不能立即清零,而是要等第7个脉冲上沿到来后,计数器被置

成0000。

不会用异步清零端那样出现0110过渡状态,这是与用异步清零端的差

别。

用同步清零端设计计数器如图3所示,如n n

Q Q LD 12 ,则为七进制计数器。

图3 同步清零端设计计数器

五、实验报告

1. 实验名称、内容和实验电路。

2. 画出用160和与非门组成6进制加法计数器的状态转换图。

3.画出同步清零端设计的七进制计数器的状态转换图。

说明同步置0与异步清零的区别?。