cadence对pcb进行后仿真

cadence经典资料1

利用Cadence工具进行板级电路信号完整性仿真虞学犬余昌盛李军朱顺临陈克桂(网络事业部南京研究所南京 210012)Tel:025-******* E-mail:yuxuequan@摘要本文讲述利用SPECCTRAQuest进行板级电路仿真解决过冲、振荡、噪声余量、单调性以及时序等信号完整性问题,重点讲述信号的时序仿真。

关键词信号完整性仿真时序过冲振荡噪声容限单调性1.引言随着数字系统设计人员在计算机、通信系统、视频系统和网络系统中开发的时钟频率和数据速率越来越高,信号边沿不断变陡,印刷电路板的线迹互连和板层特性对系统电气性能的影响也越发重要,通常当频率超过50MHz或信号上升时间Tr小于6倍传输线延时时,互连关系必须以传输线考虑,而在评定系统性能时也必须考虑印刷电路板板材的电参数。

因此,高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。

信号完整性(Signal Integrity简称 SI)是指信号在电路中以正确的时序和电压作出响应的能力。

如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。

反之,当信号不能正常响应时,就出现了误触发、阻尼振荡、过冲、欠冲等造成时钟间歇振荡和数据出错信号完整性问题。

本文主要讲述利用 SPECCTRAQuest工具进行信号质量(过冲、振荡、噪声容限、单调性等)和时序仿真。

2.信号质量和时序仿真利用SPECCTRAQuest进行信号仿真主要是利用元器件的IBIS模型以及对传输线进行建模来分析信号质量与信号时序。

对不同的信号有不同的仿真要求:对时钟同步信号,需要仿真信号时序及信号质量,满足输入端信号的建立时间和保持时间、小的过冲与振荡以及大的噪声容限;对异步信号,通常只需要仿真信号质量,满足信号的单调性、小的过冲、大的噪声容限及小的振荡。

以下主要介绍利用 SPECCTRAQuest工具进行信号质量和信号时序仿真,包括过冲、振荡、噪声容限、单调性和时序。

(完整word版)cadence软件介绍

1.Allegro PCB Design CISAllegro PCB Design CISAllegro Designer Entry CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。

扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。

通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。

无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,Allegro Designer Entry CIS提供电路设计从构思到生产所需的一切。

Allegro Designer Entry CIS是全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。

优点1、提供快捷,直观的,具备完备功能的原理图编辑工具2、通过层次式和变体(基于同一原理图,不同机型导出)设计提高复杂原理图的设计效率3、具备强大功能的CIS,帮助加速设计进程,降低项目成本4、原理图提供的自动缩放/搜索/导航功能,结合Allegro PCB Editor之间的交互探测和交互摆放,和集成的AMS—Simulatuor帮助提供设计的可生产性5、减少重复搜寻元件信息的时间,接收来自MRP,ERP和PLM的数据和支持关系型数据库使智能选择元件成为可能6、通过直接访问ActiveParts和ActiveParts门户网站,提供给选择原理图设计所需要的元件和直接获取器件供应商元件数据更大的便利,ActiveParts提供了超过200万份的元器件数据7、通过FPGA输出/输入双向数据流程自动整合可编程门阵列(FPGA)和可编程逻辑器件(PLD),从而缩短设计时间功能特色全功能原理图编辑器Allegro Designer Entry CIS,带有拼接式和层次式的原理图页面编辑器,它具有快捷、直观的原理图编辑的特点。

Allegro_信号与电源完整性

• Cadence Allegro PCB SI L, XL, and GXL • Cadence OrCAD Signal Explorer

优点

•减少设计高速互联所需的时间 一次性成功的可能性 •缩短建立最优约束所需的时间 束驱动的PCB设计流程 •通过参数扫描分析提高产品性能 •通过使用Allegro PCB PI Option XL设计 PCB电源网络降低最终产品的单位成本 •通过高级仿真技术消除了MultiGigabit高速串行传输设计用物理原型进 行多次验证的过程 •使用S参数和单个或耦合过孔模型实现 快速的MGH信号分析 期 •提高产品质量 成本和性能 从而缩短设计周 实现约 并提高

宏模型

宏模型让工程师更快更精确地对MGH驱 动器和接收器进行建模和仿真 比起

道分析仿真结果

见图

系统设计用户可以迅速的为复杂的驱动 器或接收器建立实用设置 tap 设置

ห้องสมุดไป่ตู้

晶体管级仿真 其仿真速度可以提高0到 00倍 见图

设计师可以在几秒钟内得到特定拓扑的 最优设置 可以节约数周的仿真时间 用 户可以在激励中加入确定或随机抖动,临

Allegro PCB SI搭配基于SPICE的仿真器 包含了一种强大的宏模型功能 将传统的 基于SPICE的结构建模与行为建模的速度 优势结合 内嵌的场分析工具可以对趋肤 效应 邻近/拥挤效应 回路阻抗和频域介 电常数建模 强大的建模语言对I/O缓冲器 的建模提供了扩展IBIS模型的应用功能 并且支持有损耦合的频变传输线模型 可 以精确预测PCB网络的分布式行为 图2 模型 无源互连的任何一部分都可以通过拓扑管理器在SigWave中被绘制为S参数 S参数与其他互联拓扑模型互联结 见图 legro PCB SI可以通过源同步总线中不同 信号的用户定义的derating table为用户 提供计算建立和保持时间容限的方法 见图

CAdence16.6PSpice1,使用自带例程进行第一个仿真

CAdence16.6PSpice1,使⽤⾃带例程进⾏第⼀个仿真1、建⽴原理图选择如下

2、新建⼀个⼯程,如下:

3、上图点击OK,进⼊界⾯,界⾯有下拉框,以放⼤器为例

4

5、发现⼯程⾥边⾃带如下:

6、点击1处,弹出2的参数会话框

7、点击第⼀张图,开始运⾏

8、弹出新的,运⾏结果如下:

在7界⾯更改了参数以后,只需要在8的界⾯点击运⾏就能看到新的波形了

9、可以在红圈位置直接删除不想看到的,点击选中,delete

10、点击1,在2位置添加想看到的曲线

例如看功率如下

11、如何看功率最⼤值,打击1,2处选择函数,3处选中要看的

得到结果如下

12、点击如下按钮,让此界⾯永远处于最上,之后让界⾯像第⼆张图这样

13、我们此时可以移动原理图的探针,我们会发现,波形跟着实时改变

14、⽣成报告。

window--copy to clipboard,之后在word⾥边可以直接粘贴。

15、通过点击如下按钮,能看到直流静态⼯作点、直流静态电流,功耗。

cadence ic 基础仿真

在name区域给新工具库取名,你需要添加technology file至 你的新建工具库

创建好工具库之后,有数种方式来对你的设计进行仿真

实例 1 二极管的伏安特性曲线 分析

• 首先我们通过以下方式(File-> New -> Cellview)从为二极管创建一个cell view 开始

通过原理图输入模式,使用一个电压源,一个二极管,

一个电阻可以创建以下电路。

添加元件的方法:通过Add-> Instance ->,选择二极管 ,电压源,电阻

电压源

电阻

• 将选择的元件按之前的原理图方式放置好,之后就可 以开始准备仿真了。

• 选择Tools-> Analog Environment

• 为模型库建立路径

• 通过Analysis -> Choose ,选择dc直流分析模式

• Dc仿真进行的仿真波形曲线如下图所示:

实例7 差分对中的高频率响 应

• 为了估计以动态电流镜为负载的差分对的频率响应特征,绘制原 理图如下:

• 设置暂态分析模式 • 设置网线为输入网线和输出网线

• 仿真后获得的波形图如下

实例8 差分对的噪声分析 下图所示的为1/f 噪声和输入参考噪声的模型

• 可以得到如下图所示的一族伏安特性曲线

实例3 MOS 电容器件电容电压曲线的分析

• 按下图的方式进行分析模式,器件参数等的设置

• 点击Simulation -> Netlist and Run 运行仿真

•

• 选择参数分析

• 设置参数分析

• 通过Output -> Setup选择需要输出的参量

• 通过原理图可以选择需要绘制的测试参量

Allegro PCB SI - 一步一步学会前仿真

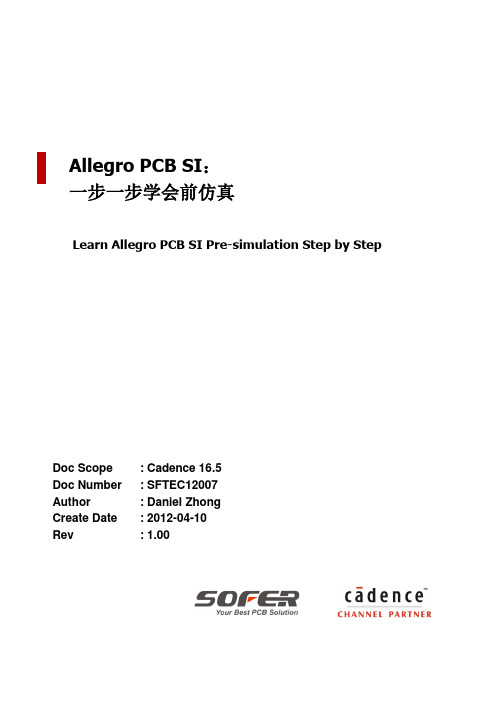

Allegro PCB SI:一步一步学会前仿真Learn Allegro PCB SI Pre-simulation Step by StepDoc Scope : Cadence 16.5Doc Number : SFTEC12007Author : Daniel ZhongCreate Date : 2012-04-10Rev : 1.00目录1Cadence Allegro PCB SI简介 (7)1.1高速PCB设计流程 (7)2Allegro PCB SI的前仿真 (8)2.1准备仿真模型和其他需求 (8)2.1.1获取所使用元器件的仿真模型 (9)2.1.2获取所使用连接器的仿真模型 (10)2.1.3获取所使用元器件和连接器的器件手册和用户指南等相关资料 (10)2.1.4获取所需的规范文档 (10)2.1.5了解相关电路和接口工作原理 (10)2.1.6提取与信号完整性相关的要求 (10)2.1.7预先创建拓扑样本 (11)2.1.8预先创建相对于不同阈值电压的眼图模板 (11)2.1.9预先创建自定义测量 (12)2.2仿真前的规划 (12)2.3关键器件预布局 (13)2.4模型加载和仿真配置 (13)2.4.1模型的转化 (14)2.4.2使用SI Design Setup配置 (15)2.4.3选择需要配置的信号线 (16)2.4.4设置仿真库 (18)2.4.5设置电源和地网络 (20)2.4.6设置叠层 (24)2.4.7设置元器件类别 (27)2.4.8为元器件分配和创建模型 (28)2.4.9设置差分对 (37)2.4.10设置仿真参数 (42)2.4.11SI Design Audit相关 (50)2.4.12提取拓扑 (52)2.4.13在SigXP中设置仿真库和仿真参数 (54)2.4.14在SigXP中绘制拓扑 (58)2.5方案空间分析 (68)2.5.1输出驱动力扫描分析 (71)2.5.2Stub长度扫描分析 (73)2.5.3线宽线间距扫描分析 (74)2.6方案到约束规则的转化 (76)2.6.1传输线延迟规则的设置 (77)2.6.2拓扑结构等传输线特性规则的设置 (80)2.6.3传输线耦合规则的设置 (80)2.6.4拓扑规则在约束管理器中的应用 (81)3Allegro PCB SI的后仿真 (84)表格表格 1:Routed Interconnect Models参数 (45)表格 2:Simulation栏眉仿真参数 (47)表格 3:IO Cell Stimulus Edit窗口中的选项 (68)图图 1:传统的PCB设计流程图 (7)图 2:Allegro PCB SI高速PCB设计流程图 (8)图 3:眼图模式下的眼图模板 (11)图 4:地址、命令和控制信号传输线拓扑 (12)图 5:RDIMM的布局示意图 (13)图 6:Model Integrity界面 (14)图 7:使用Model Integrity将IBIS文件转换至DML格式 (15)图 8:Cadence Product Choices产品选择器窗口 (16)图 9:Allegro PCB SI GXL界面 (17)图 10:Setup Category Selection窗口 (17)图 11:Setup Xnet Selection窗口 (17)图 12:Allegro PCB SI GXL关于网络设置的提醒框 (18)图 13:Setup Library Search Directories窗口 (19)图 14:Setup Library File Extensions窗口 (19)图 15:Setup Working Libraries窗口 (19)图 16:Setup Power and Ground Nets窗口 (20)图 17:Allegro PCB SI GXL电压赋值窗口 (21)图 18:选择“Edit Voltage On Any Net In Design” (21)图 19:Identify DC Nets窗口。

(完整版)HSPICE与CADENCE仿真规范与实例..

(完整版)HSPICE与CADENCE仿真规范与实例..电路模拟实验专题实验⽂档⼀、简介本实验专题基于SPICE(Simulation Program With Integrated Circuit)仿真模拟,讲授电路模拟的⽅法和spice仿真⼯具的使⽤。

SPICE仿真器有很多版本,⽐如商⽤的PSPICE、HSPICE、SPECTRE、ELDO,免费版本的WinSPICE,Spice OPUS等等,其中HSPICE和SPECTRE功能更为强⼤,在集成电路设计中使⽤得更为⼴泛。

因此本实验专题以HSPICE和SPECTRE 作为主要的仿真⼯具,进⾏电路模拟⽅法和技巧的训练。

参加本实验专题的⼈员应具备集成电路设计基础、器件模型等相关知识。

⼆、Spice基本知识(2)⽆论哪种spice仿真器,使⽤的spice语法或语句是⼀致的或相似的,差别只是在于形式上的不同⽽已,基本的原理和框架是⼀致的。

因此这⾥简单介绍⼀下spice的基本框架,详细的spice语法可参照相关的spice教材或相应仿真器的说明⽂档。

⾸先看⼀个简单的例⼦,采⽤spice模拟MOS管的输出特性,对⼀个NMOS管进⾏输⼊输出特性直流扫描。

V GS从1V变化到3V,步长为0.5V;V DS从0V变化到5V,步长为0.2V;输出以V GS为参量、I D与V DS之间关系波形图。

*Output Characteristics for NMOSM1 2 1 0 0 MNMOS w=5u l=1.0uVGS 1 0 1.0VDS 2 0 5.op.dc vds 0 5 .2 Vgs 1 3 0.5.plot dc -I(vds).probe*model.MODEL MNMOS NMOS VTO=0.7 KP=110U+LAMBDA=0.04 GAMMA=0.4 PHI=0.7.end描述的仿真电路如下图,图2-1 MOS管输⼊输⼊特性仿真电路图得到的仿真波形图如下图。

cadence仿真设置简介

下面是cadence里面设置calibre仿真的一些简单介绍,自己最近也在学习,现在告一段落,整理分享给大家。

有需要的可以看看。

疏漏不对之处还请见谅,欢迎互相讨论。

Calibre DRC设置:Rules:DRC rules file加入规则文件DRC run directory选择自己建的文件夹。

OK.Run DRCLVS设置:Rules:LVS rules file加入规则文件LVS run directory选择自己建的文件夹。

最好再新建一个存放Inputs:勾选hierarchical和layout vs netlistlayout和netlists下面的export from viewer全都勾选OK.Run LVS上面两个验证如果出现错误,就对照着列出来的错误仔细修改至通过。

PEX(提参)设置:Rules:PEX rules file加入规则文件PEX run directory选择自己建的文件夹。

最好再新建一个存放Inputs:layout和netlists下面的export from viewer全都勾选。

类似LVS那样Outputs:Netlists里面的format选择Calibreview。

其他默认。

OK.run PEX这里如果出现这个错误:解决办法:到calibre.rcx的1219行,加入同一个文件夹下的rules文件路径即可如下图。

Run PEX结束后会自动跳出下面的设置界面:除了calview.cellmap文件选用自己的对应的之外。

其他设置仿照这个设置。

然后点击OK。

这是提参的最后一步,时间可能有点长,耐心等待。

结束后会出现下图,点击close即可。

Warning不用管。

后仿:到这里版图提参就结束了。

需要进行后仿。

打开ADE环境,在setup->Environment,switch view list一栏的最前面加上calibre 这个单词,如下图,点击OK。

cadence仿真查开环增益

cadence仿真查开环增益

Cadence仿真是一种用于电子设计的仿真技术,它可以用

来检测系统的功能性,并根据设计的要求和需求来调整元件和电路参数。

Cadence仿真可以用来模拟开环增益,它是电路增

益的一个重要参数,可以用来衡量系统的性能。

开环增益定义为电路的输出号和输入号的比值,它可以指示电路的放大能力。

它的公式为:开环增益 = 输出号 / 输入号。

开环增益可以用来衡量电路的性能,它可以反映电路的噪声抑制能力。

使用Cadence仿真来检测开环增益,首先需要准备好模拟电路,并且把它放到Cadence中。

然后,在模拟器中设置输入号,并设置输出号参数。

接下来,在模拟器中运行仿真,并记录下输出号和输入号的比值。

最后,根据记录的比值,计算出开环增益的值。

用Cadence仿真来检测开环增益,可以让设计者在调整元件参数和电路参数之前,对系统的性能有一个清晰的认识。

另外,使用Cadence仿真来模拟开环增益,也可以让设计者更好地控制电路的放大能力和噪声抑制能力。

总之,Cadence仿真可以用来模拟开环增益,它可以更好

地控制电路放大能力和噪声抑制能力,让设计者更加了解系统性能,从而更加有效地进行调整设计参数。

cadence详细教程(模拟电路)

cadence详细教程(模拟电路)⽬录1.Cadence系统编辑环境 (2)实验1:Cadence系统编辑环境设置与基本操作 (2)2.电路图设计⼯具-Schematic (8)实验2:⼆与⾮门电路原理图设计 (8)实验3:数、模混合集成电路原理图设计 (14)3.电路仿真⼯具-ADE (18)实验4:ADE环境设置 (18)实验5:差分放⼤器电路仿真 (23)4.版图设计⼯具-Layout Editor (30)实验6:Layout Editor环境设置 (30)实验7:MOS管版图设计 (35)实验8:BJT管版图设计 (38)实验9:CMOS反相器版图设计 (42)实验10:Pcells版图设计 (46)实验11:pk44chip芯⽚版图综合设计 (53)5.版图验证⼯具-Diva (57)实验12:版图验证 (57)实验13:版图识别 (66)实验14:版图改错 (71)6.设计性实验 (73)实验15:RS触发器设计 (73)实验16:静态存储器设计 (76)实验17:三态与⾮门设计 (79)实验18:基准电压源设计 (81)实验19:CMOS放⼤器设计 (83)实验20:异或门设计 (84)Lab 1 Cadence系统环境设置与基本操作1.实验⽬的熟悉Cadence系统环境了解CIW窗⼝的功能掌握基本操作⽅法2.实验原理系统启动Cadence系统包含有许多⼯具(或模块),不同⼯具在启动时所需的License 不同,故⽽启动⽅法各异。

⼀般情况下涉及到的启动⽅式主要有以下⼏种,本实验系统所⽤到的有icms、icfb、layoutPlus等。

①前端启动命令:表1.1 前端启动命令命令规模功能icde s 基本数字模拟设计输⼊icds s icde以及数字设计环境icms s 前端模拟、混合、微波设计icca xl 前端设计加布局规划②版图⼯具启动命令表1.2 版图⼯具启动命令命令规模功能Layout s 基本版图设计(具有交互DRC功能)layoutPlus m 版图设计(具有⾃动化设计⼯具和交互验证功能)③系统级启动命令表1.3 系统级启动命令命令规模功能swb s PCB设计msfb l 混合型号IC设计icfb xl 前端到后端⼤多数⼯具CIW窗⼝Cadence系统启动后,⾃动弹出“what’s New…”窗⼝和命令解释窗⼝CIW (Command Interpreter Window)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、一般流程

1、 IBIS库转换层DML格式

2、 给器件加载模型并定义管脚

3、 定义电源、地网络等

4、 提取拓扑结构

5、 设置仿真参数

6、 仿真结果分析

具体步骤请参见一些cadence后仿真的相关pdf文档。

二、补充说明

在加载模型之后注意定义管脚,如果没有定义,仿真结果会有很大差异。

方法如下:

1、在上图给器件加载模型的窗口中,点击 fild model 为器件加载模型,然后点击edit model,

出现下图:

2、选择assign signal pins 然后在all pin中选择需要定义的管脚。被选择的管脚会出现在

selected pin方框中。

点击右侧的browse 出现下图:

3、在dml model browser中选择需要的Iocell 关闭窗口、确定、完成。

4、如需对差分信号进行仿真的话,需要对差分pin进行设置。

三、pcb中FPGA与DDR2之间一根数据线的仿真。

1、提取的信号线为下图中白色高亮。

1、提取的拓扑结构

包括走线和过孔的一些具体信息。

U17是DDR2,FPGA1是xilinx—c6v130tff784

2、层叠结构

所仿真的信号线走的是S1层,为达到50 ohm 匹配,s1上下介质厚度为6mil。

3、仿真参数

4、仿真结果

Ddr2发送 fpga接收时候的波形:

浅绿色和浅蓝色分别是ddr2的pin和pad处的波形。

黑色和蓝色分别是fpga的pin和pad处的波形。

Fpga发送,ddr2接收时候的波形:

5、以下是将走线拉直以后的仿真结果:

Ddr2 发送,fpga接收:

Fpga发送。Ddr2接收:

新手第一次做的仿真,希望与大家一起交流讨论。可以加Q: 5.1.9.