数字逻辑第四章课后答案

数电第四章参考答案

第四章 组合逻辑电路 作业 参考答案【题4-1】 分析图示组合逻辑电路,列出真值表,写出输出Y 1、Y 2与输入的逻辑函数式,说明整个电路所实现的逻辑功能(不是单个输出与输入的关系,而是把2个输出与3个输入综合起来看)。

解:该电路的逻辑功能为全加器,Y 1是和,Y 2是进位。

【题4-2】某汽车驾驶员培训班进行结业考试,有三名评判员,其中A 为主评判员,B 和C 为副评判员。

在评判时,按照少数服从多数的原则通过,但主评判员认为合格,方可通过。

请填写真值表,写出逻辑表达式,并用一片74LS00(内含四个2输入端与非门)或一片74LS02(内含四个2输入端或非门)这2种方法实现此评判规定。

解:设评判员评判合格为“1”,反之为“0”; 考试通过,F 为“1”,反之为“0”。

根据题意,列真值表如下。

据此可得:ABC12ABCC B A C B A C B A AC BC AB C B A ABC Y +++=+++++=)()(1AC BC AB Y ++=2ACAB AC AB F =+=CB AC B A F ++=+=)(FB CA FB CA【题4-3】设计一个“4输入1输出”的组合逻辑电路,实现“五舍六入”的功能:即当输入的四位8421BCD 码不大于5时,输出0;否则输出1。

要求: (1) 画出卡诺图、化简逻辑函数;(2) 用1片CD4001(内含四个2输入端或非门)实现该逻辑功能(标出管脚号)。

【题4-4】设计一个代码转换电路,输入为3位二进制代码、输出为3位格雷码(见下表),要求从CD4011、CD4001、CD4030中选用1个最合适的芯片实现逻辑功能。

解:CDAB Y 00X X 0X 011001X XXCA B A C A B A BC A Y +++=++=+=))((FB CA21313546121101000111XABC00011011YABC0010111ZABCAX =BA B A B A Y ⊕=+=CB C B C B Z ⊕=+=B CAYZX【题4-5】用一片74HC138(3-8译码器)辅以“4输入与非门”实现“1位全减”。

数字逻辑设计习题第4章

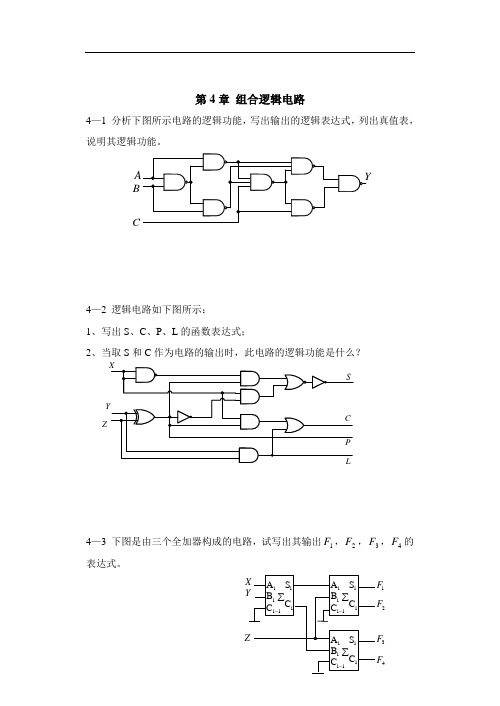

第4章 组合逻辑电路4—1 分析下图所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

4—2 逻辑电路如下图所示: 1、写出S 、C 、P 、L 的函数表达式;2、当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?4—3 下图是由三个全加器构成的电路,试写出其输出1F ,2F ,3F ,4F 的表达式。

123B CZP和4—4 下图是由3线/8线译码器74LS138和与非门构成的电路,试写出1P的表达式,列出真值表,说明其逻辑功能。

2 Array4—5使用74LS138 译码器及少量门电路对三台设备状态进行监控,由不同指示灯进行指示。

当设备正常工作时,指示灯绿灯亮;当有一台设备出故障时,指示灯红灯亮;当有两台设备出故障时,指示灯黄灯亮;当有三台设备出故障时,指示灯红灯和黄灯都亮。

4—6 下图4.6是由八选一数据选择器构成的电路,试写出当1G 0G 为各种不同的取值时的输出Y 的表达式。

4—7仿照全加器设计一个全减器,被减数为A ,减数为B ,低位来的借位为C ,差为D ,向上借一位为J 。

要求:1.写出真值表,写出D 与J 的表达式;2.用译码器74LS138和必要的基本门电路实现此电路;3.用双四选一数据选择器实现。

G A4—8 设计一组合逻辑电路,输入为四位二进制码3B 2B 1B 0B ,当3B 2B 1B 0B 是BCD8421码时输出1=Y ;否则0=Y 。

列出真值表,写出与或非表达式,用集电极开路门实现。

4—9 设计一个多功能组合数字电路,实现下表所示逻辑功能。

表中1C 0C 为功能选择输入信号;A ,B 为输入变量;F 为输出。

1.列出真值表,写出F 的表达式; 2.用八选一数据选择器和门电路实现。

4—10分析图4.10(a)所示电路:1.写出L,Q,G的表达式,列出真值表,说明它完成什么逻辑功能。

2.用图4.10(a)所示电路与集成四位数码比较器(如图4.10(b)所示)构成一个五位数码比较器。

阎石数电第六版课后习题答案详解第四章答案

阎石数电第六版课后习题答案详解第四章答案在《阎石数电第六版》教材第四章中,主要介绍了逻辑代数、逻辑函数和逻辑图的相关内容。

本文将对第四章的课后习题答案进行详细解析。

4.1 课后习题答案详解题目1已知 F = A·B+C 和 G = A+B·C,求 F+G 的简化结果。

答案解析首先,根据 F = A·B+C 和 G = A+B·C,可以得到 F+G 的表达式:F+G = (A·B+C) + (A+B·C)对 F+G 进行展开并合并项,得到:F+G = A·B+C+A+B·C再对表达式进行化简,得到简化结果:F+G = A+B+C所以,F+G 的简化结果为 A+B+C。

题目2已知 F = A·B+C 和 G = A+C,求 F · G 的简化结果。

答案解析首先,根据 F = A·B+C 和 G = A+C,可以得到 F · G 的表达式:F · G = (A·B+C) · (A+C)对 F · G 进行展开并合并项,得到:F ·G = A·B·A + A·B·C + C·A + C·C再对表达式进行化简,得到简化结果:F ·G = A·B·A + A·B·C + C由于 A·B·A 可以简化为 A·B,所以简化后的结果为:F ·G = A·B + A·B·C + C题目3已知 Z = X+Y+AB,求Z · (X′+AB′) 的简化结果。

答案解析首先,对Z · (X′+AB′) 进行展开,得到:Z · (X′+AB′) = (X+Y+AB) · (X′+AB′)将两个括号中的表达式进行展开,得到:Z · (X′+AB′) = X·X′ + X·AB′ + Y·X′ + Y·AB′ + AB·X′ + AB·AB′化简表达式,得到简化结果:Z · (X′+AB′) = 0 + AB′ + 0 + 0 + 0 + AB·AB′由于X·X′ = 0,Y·X′ = 0,AB·X′ = 0,所以简化后的结果为:Z · (X′+AB′) = AB′ + AB·AB′题目4已知Z = A · (X+Y)′+B·C,求Z · (X′+Y′) 的简化结果。

数字逻辑-第四章习题-759

4-1 试分析图题4-1中各电路的逻辑功能。

图题4 - 1

4-2 试分析图题4-2中各电路的逻辑功能。

图题4 - 2

4-3 分析图题4-3所示逻辑电路,写出其简化的逻辑表达 式,并用与非门改进设计。

图题4 - 3

4-4 分析图题4-4所示逻辑电路,写出其简化的逻辑表 达式。

图题4 - 4

4-5 分析图题4-5所示逻辑电路的逻辑功能,写出函数 的逻辑表达式,并用最简线路实现它。

4-16 举重比赛有3个裁判,一个是主裁判A,2个是辅 裁判B和C,杠铃完全举上的裁决由每个裁判按一下自己 面前的按钮来决定。只有2个基本点以上裁判(其中必须 有主裁判)判明成功时,表示成功的灯才亮。试设计此逻 辑电路。

4-17 试用与非门设计一个无反变量输入的最简三级 线路,以实现下列函数。

(1)F(A ,B,C)= Σ m(3,5,6) (2)F(A ,B,C,D)= Σm(1,4,5,8,12)+

Σd(3,6,9,15) (3)F(A ,B,C,D)= Σ m(0,6,10,11,14) (4)F(A ,B,C)= AB + AC + AB 4-18 试用8选1多路选择器组成64选1多路选择器。 4-19 试用中规模集成4位二进制比较器组成18位二 进制数字比较器。 4-20 试用中规模集成4位二进制比较器组成20位二 进制数字比较器。

4-10 设二进制补码[x]补= x0. x1 x2 x3 x4 ,分别写出下 列要求的判断条件:

(1)(1/2≤ x)或(x < - 1/2) (2)(1/4≤ x <1/2)或(- 1/2≤ x < - 1/4) (3)(1/8≤ x <1/4)或(- 1/4≤ x < - 1/8) (4)(0≤ x <1/8)或(- 1/8≤ x <0) 4-11 设输入ABCD是按余3码编码的二进制数码,其相 应的十进制数路如图题4-6 所示,其中A和B为输入变量 ,F为输出函数。试说明当S3 、S2 、S1 、S0 作为控制信 号时,F 与A、B 的逻辑关系。

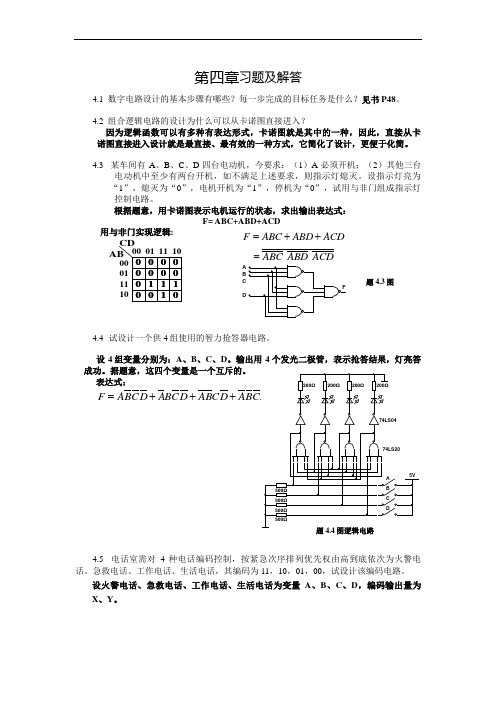

第四章习题及解答

第四章习题及解答4.1 数字电路设计的基本步骤有哪些?每一步完成的目标任务是什么?见书P48。

4.2 组合逻辑电路的设计为什么可以从卡诺图直接进入?因为逻辑函数可以有多种有表达形式,卡诺图就是其中的一种,因此,直接从卡诺图直接进入设计就是最直接、最有效的一种方式,它简化了设计,更便于化简。

4.3 某车间有A 、B 、C 、D 四台电动机,今要求:(1)A 必须开机;(2)其他三台电动机中至少有两台开机,如不满足上述要求,则指示灯熄灭。

设指示灯亮为“1”,熄灭为“0”,电机开机为“1”,停机为“0”,试用与非门组成指示灯控制电路。

根据题意,用卡诺图表示电机运行的状态,求出输出表达式:F= ABC+ABD+ACD用与非门实现逻辑:4.4 试设计一个供4组使用的智力抢答器电路。

设4组变量分别为:A 、B 、C 、D 。

输出用4个发光二极管,表示抢答结果,灯亮答表达式: F ABCD ABCD ABCD =+++4.5 电话室需对4种电话编码控制,按紧急次序排列优先权由高到底依次为火警电话、急救电话、工作电话、生活电话,其编码为11,10,01,00,试设计该编码电路。

设火警电话、急救电话、工作电话、生活电话为变量A 、B 、C 、D ,编码输出量为X 、Y 。

AB CD01001110000000000001111000 01 11 10 F ABC ABD ACDABC ABD ACD =++=AB C D题4.3图列出编码真值表:4.6 试用3线-8线译码器和门电路实现以下函数:4.7 试用四选一多路选择器实现函数Y ABC AC BC =++。

1. 求出最小项、及最小项反函数非表达式:2. 对比四选一多路选择器表达式:0123Y ABD ABD ABD ABD =+++我们发现用原函数无法用一个四选一选择器实现,但反函数只有三个最小项,因为实际的数据选择器,它们都有两个互补的变量输出,因此从反变量输出端(~W)就可以达到要求了。

数字逻辑电路与系统设计习题答案

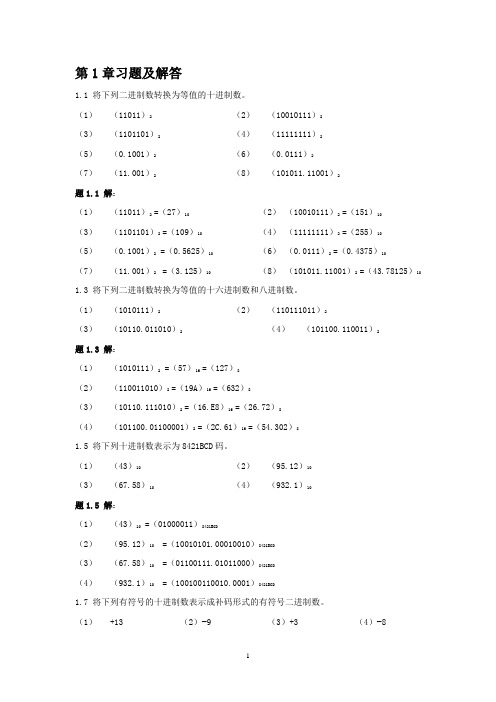

第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)(10010111)2(3)(1101101)2 (4)(11111111)2(5)(0.1001)2(6)(0.0111)2(7)(11.001)2(8)(101011.11001)2题1.1 解:(1)(11011)2 =(27)10 (2)(10010111)2 =(151)10(3)(1101101)2 =(109)10 (4)(11111111)2 =(255)10(5)(0.1001)2 =(0.5625)10(6)(0.0111)2 =(0.4375)10(7)(11.001)2=(3.125)10(8)(101011.11001)2 =(43.78125)10 1.3 将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(110111011)2(3)(10110.011010)2 (4)(101100.110011)2题1.3 解:(1)(1010111)2 =(57)16 =(127)8(2)(110011010)2 =(19A)16 =(632)8(3)(10110.111010)2 =(16.E8)16 =(26.72)8(4)(101100.01100001)2 =(2C.61)16 =(54.302)81.5 将下列十进制数表示为8421BCD码。

(1)(43)10 (2)(95.12)10(3)(67.58)10 (4)(932.1)10题1.5 解:(1)(43)10 =(01000011)8421BCD(2)(95.12)10 =(10010101.00010010)8421BCD(3)(67.58)10 =(01100111.01011000)8421BCD(4)(932.1)10 =(100100110010.0001)8421BCD1.7 将下列有符号的十进制数表示成补码形式的有符号二进制数。

数字电路第四章答案

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

在线网课《数字逻辑(山东联盟-烟台大学)》课后章节测试答案

绪论单元测试1【多选题】(5分)计算机的五大组成部分是()、()、()、输入设备和输出设备。

A.控制器B.运算器C.硬盘D.存储器2【判断题】(5分)数字逻辑课程是计算机专业的一门学习硬件电路的专业基础课。

A.错B.对3【判断题】(5分)计算机的运算器是能够完成算术和逻辑运算的部件,逻辑运算比如与运算。

A.错B.对第一章测试1【单选题】(10分)与二进制数1101011.011对应的十六进制数为()A.53.3B.73.3C.6B.3D.6B.62【单选题】(10分)与二进制数101.011等值的十进制数是()A.5.175B.5.375C.3.625D.5.6753【单选题】(10分)(17)10对应的二进制数是()A.10011B.101111C.10110D.100014【判断题】(10分)数字电路中用“1”和“0”分别表示两种状态,二者通常无大小之分A.错B.对5【判断题】(10分)格雷码具有任何相邻码只有一位码元不同的特性A.对B.错6【多选题】(20分)以下代码中为无权码的为()A.余三码B.格雷码C.5421BCD码D.8421BCD码7【单选题】(10分)十进制数25用8421BCD码表示为()A.00100101B.11010C.11001D.101018【单选题】(10分)BCD码1001对应的余3BCD码是()A.1011B.1100C.1000D.10109【单选题】(10分)8421BCD码001001010100转换成十进制数为()A.252B.1250C.1124D.254第二章测试1【单选题】(5分)在何种输入情况下,“或非”运算的结果是逻辑0A.任一输入为0,其他输入为1B.全部输入是0C.全部输入是1D.任一输入为12【单选题】(5分)一个两输入端的门电路,当输入为1和0时,输出不是1的门是()A.或门B.异或门C.与非门D.或非门3【多选题】(10分)求一个逻辑函数F的对偶式,可将F中的()。

习题册答案-《数字逻辑电路(第四版)》-A05-3096

第一章逻辑门电路§1-1 基本门电路一、填空题1.与逻辑;Y=A·B2.或逻辑;Y=A+B3.非逻辑;Y=4.与;或;非二、选择题1. A2. C3. D三、综合题1.2.真值表逻辑函数式Y=ABC§1-2 复合门电路一、填空题1.输入逻辑变量的各种可能取值;相应的函数值排列在一起2.两输入信号在它们;异或门电路3.并;外接电阻R;线与;线与;电平4.高电平;低电平;高阻态二、选择题1. C2. B3. C4. D5. B三、综合题1.2.真值表逻辑表达式Y1=ABY2=Y3==A+B 逻辑符号3.第二章组合逻辑电路§2-1 组合逻辑电路的分析和设计一、填空题1.代数;卡诺图2.n;n;原变量;反变量;一;一3.与或式;1;04.组合逻辑电路;组合电路;时序逻辑电路;时序电路5.该时刻的输入信号;先前的状态二、选择题1. D2. C3. C4. A5. A三、判断题1. ×2. √3. √4. √5. ×6. √四、综合题1.略2.(1)Y=A+B(2)Y=A B+A B(3) Y=ABC+A+B+C+D=A+B+C+D3. (1) Y=A B C+A B C+ A B C + ABC=A C+AC(2) Y=A CD+A B D+AB D+AC D(3) Y=C+A B+ A B4. (a)逻辑函数式Y= Y=AB+A B真值表逻辑功能:相同出1,不同出0 (b)逻辑函数式Y=AB+BC+AC真值表逻辑功能:三人表决器5.状态表逻辑功能:相同出1,不同出0逻辑图1. 6.Y=A ABC+B ABC+C ABC判不一致电路,输入不同,输出为1,;输入相同,输出为0。

§2-2 加法器一、填空题1.加数与被加数;低位产生的进位2.加数与被加数;低位产生的进位3.加法运算二、选择题1. A2. C三、综合题1.略2.略3.§2-3 编码器与比较器一、填空题1. 编码2. 101011;010000113. 十;二;八;十六4. 0;1;逢二进一;10;逢十进一5. 二进制编码器;二—十进制编码器6. 两个数大小或相等7. 高位二、选择题1. A2. B3. C4. B三、综合题1.略2.(1)10111;00100011(2)00011001;19(3)583. (1)三位二进制(2)1,1,0(3)1,1,14.§2-4 译码器与显示器一、填空题1. 编码器;特定含意的二进制代码按其原意;输出信号;电位;解码器2. 二进制译码器;二—十进制译码器;显示译码器3. LED数字显示器;液晶显示器;荧光数码管显示器4. 1.5~3;10mA/段左右5. 共阴极显示译码器;共阳极显示译码器;液晶显示译码器二、选择题1. A;D2. A三、判断题1.√2.×3.×4.√5.√四、综合题七段显示译码器真值表f=D C B A +D C B A +D C B A+D CB A +D C B A +D C B A =D+B A +C A +C B =DB AC AC B§2-5 数据选择器与分配器一、填空题1.多路调制器;一只单刀多掷选择开关;地址输入;数字信息;输出端2.从四路数据中,选择一路进行传输的数据选择器3.地址选择;输出端二、选择题1. D2. A;C三、判断题1. √2. ×四、综合题1.略2. Y=A B D0+A BD1+A B D2+ABD3第三章触发器§3-1 基本RS触发器与同步RS触发器一、填空题1.两个;已转换的稳定状态2.R S+RSQ n;R+S=13. R S Q n+ R S;RS=04.置0;置15.相同;低电平;高电平6.时钟信号CP7.D触发器8.空翻二、选择题1.D2.B3.A4.B5.B6.D三、判断题1. ×2. ×3. √4. ×5. ×6. ×四、综合题1.略2.3.4.5.略§3-2主从触发器与边沿触发器一、填空题1.空翻2.置0、置1、保持、翻转3.D、J Q n+K Q n4.保持、置1、清0、翻转5.电平、主从6.一次变化7.边沿触发器8.不同、做成9.置0、置1、时钟脉冲二、选择题1.A2.A3.D4.B5.A6.C7.D8.B9.A10.D三、判断题1. √2. ×3. ×4. ×5. √6. ×7. √8. √四、综合题1.2.3.4.略5.略6.§3-3触发器的分类与转换一、填空题1.T、T'2. T Q n+ T Q n、Q n3.1、04. Q n、Q n5. 16. T'7. T8. T'二、选择题1.D2.D3.D4.B5.B三、判断题1. ×2. ×3. ×4. ×四、分析解答题1.2.3.略4.略5.略第四章时序逻辑电路§4-1 寄存器一、填空题1.输入信号;锁存信号2.接收;暂存;传递;数码;移位二、选择题1. C2. B;A三、判断题1. √2. ×3. √四、综合题1.JK触发器构成D触发器,即Q n+1= D。

数字逻辑电路与系统设计习题答案

第1章习题及解答将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)()2(3)(1101101)2 (4)()2(5)()2(6)()2(7)()2(8)()2题解:(1)(11011)2 =(27)10 (2)()2 =(151)10(3)(1101101)2 =(109)10 (4)()2 =(255)10(5)()2 =()10(6)()2 =()10(7)()2=()10(8)()2 =()10将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(1)2(3)()2 (4)()2题解:(1)(1010111)2 =(57)16 =(127)8(2)(0)2 =(19A)16 =(632)8(3)()2 =()16 =()8(4)()2 =(2C.61)16 =()8将下列十进制数表示为8421BCD码。

(1)(43)10 (2)()10(3)()10 (4)()10题解:(1)(43)10 =(01000011)8421BCD(2)()10 =(.00010010)8421BCD(3)()10 =()8421BCD(4)()10 =(.0001)8421BCD将下列有符号的十进制数表示成补码形式的有符号二进制数。

(1) +13 (2)−9 (3)+3 (4)−8题解:(1) +13 =(01101)2(2)−9 =(10111)2(3) +3 =(00011)2(4)−8 =(11000)2用真值表证明下列各式相等。

(1)BA+=+B+BBAA(2)()()()=⊕A⊕CACABB(3)()C BA+=+BCA(4)CAB++A=AABC题解:(1)证明BA+=++BABBA(2)证明()()()ACABCBA⊕=⊕(3)证明()C BACBA+=+(4)证明CAB++=AACBA用逻辑代数公式将下列逻辑函数化成最简与或表达式。

(1)D++A=F+BCBCACA(2)()()D++=F+AACCDA(3)()()B++F+=B+DCDBDDA(4)()D++F+=ADCBCBA(5)()C A B C B AC F ⊕++= (6)()()C B B A F ⊕⊕= 题解:(1)BC A D C A BC C A B A F +=+++= (2)()()CD A D CD A C A A F +=+++=(3)()()C B B A D B D A C B D D D B F ++=++++= (4)()D C B A D C B AD C B A F +=+++= (5)()C B AC C A B C B AC F +=⊕++=(6)()()C A BC B A C B B A F ++=⊕⊕=或C A C B AB ++= 用卡诺图将下列逻辑函数化成最简与或表达式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑第四章课后答案盛建伦:《数字逻辑与VHDL逻辑设计》习题解答习题4解答4-1试用与非门设计实现函数F(A,B,C,D)=Σm(0,2,5,8,11,13,15)的组合逻辑电路。

解:首先用卡诺图对函数进行化简,然后变换成与非-与非表达式。

化简后的函数4-2CDAB00010010010111100110111000111000A&&BC&&&&&F&FBCDABDBCDACDBCDABDBCDACDBCDABDBCDACDD&试用逻辑门设计三变量的奇数判别电路。

若输入变量中1的个数为奇数时,输出为1,否则输出为0。

解:本题的函数不能化简,但可以变换成异或表达式,使电路实现最简。

真值表:逻辑函数表达式:ABC000001010011100101110111Y01101001=1ABC逻辑图=1YYABCABCABCABC(AB)C4-1盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-3用与非门设计四变量多数表决电路。

当输入变量A、B、C、D有三个或三个以上为1时输出为1,输入为其他状态时输出为0。

解:真值表:先用卡诺图化简,然后变换成与非-与非表达式:ABCD00000010001101000101011001111000101010111100110111101111 YABDABCBCDACDABDABCBCDACDABDABCBCDACDY00000010010111C&00010A B00011110CD00010000001011100111001010010逻辑图A&B&&Y逻辑函数表达式:D4-4&用门电路设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

解:首先根据所给问题列出真值表,然后用卡诺图化简逻辑函数,按照化简后的逻辑函数画逻辑图。

4-2盛建伦:《数字逻辑与VHDL逻辑设计》习题解答真值表:卡诺图化简:ABCDY1Y2Y3Y40000000000010001001000110011001001000110010101110110 0101011101001000110010011101101011111011111011001010110110111110 100111111000ABCD00011110000011011100111100100011Y3的卡诺图化简后的逻辑函数:Y1AY2ABABABY3BCBCBCY4CDCDCD4-3ABCD00011110000000010000111111101111Y1的卡诺图ABCD00011110000000011111110000101111Y2的卡诺图ABCD00011110000101010101110101100101Y4的卡诺图逻辑图Y1Y2Y3Y4=1=1=1ABCD盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-5图 4.48所示是一个由两台水泵向水池供水的系统。

水池中安置了A、B、C三个水位传感器。

当水池水位低于C点时,两台水泵同时供水。

当水池水位低于B点且高于C点时,由水泵M1单独供水。

当水池水位低于A点且高于B点时,由水泵M2单独供水。

当水池水位高于A点时,两台水泵都停止供水。

试设计一个水泵控制电路。

要求电路尽可能简单。

M1ABCM2图4.48习题4-5的示意图解:设水位低于传感器时,水位传感器的输出为1,水位高于传感器时,水位传感器的输出为0。

首先根据所给问题列出真值表。

其中有几种情况是不可能出现的,用约束项表示。

ABC000001010011100101110111如果利用约束项化简如果不利用约束项化简M1M200某某某某某某A01BC0001某某1110某某0011A01BC0001某某1110某某011001某某1011M1的卡诺图M2的卡诺图M1BM1AB逻辑图M2CABM1M2≥1M2ABCABCA(BC)M1&M2&=&1BACABC(a)用约束项化简(b)不用约束项化简4-4盛建伦:《数字逻辑与VHDL逻辑设计》习题解答习题4-5的逻辑图4-6试用3线-8线译码器74HC138和门电路实现如下多输出逻辑函数并画出逻辑图。

Y1ABCA(BC)Y2ACABY3(AB)(AC)Y4ABCABC解:先将逻辑函数变换成最小项之和的形式Y1ABCABACABCABCABCABCY2ABCABCABCABCYABACABCABCABCABC3再变换成与74HC138一致的形式Y1ABCABCABCABCmmmm53211逻辑图&&Y4YABCABCABCABC2m7m4m3m2Y3ABCABCABCABCm7m5m3m2Y4ABCABCm7m0ABCY0Y1S3Y2Y374HC138Y4Y5A2Y6A1Y7A0S1S2Y1&Y2&Y3令74HC138的A2=A,A1=B,A0=C,4-7试用3线-8线译码器74HC138和逻辑门设计一组合电路。

该电路输入某,输出Y均为3位二进制数。

二者之间关系如下:当2≤某<7时,Y=某-2某<2时,Y=1某=7时,Y=6解:首先根据所给问题列出真值表。

某2某1某0000001010011100101Y2Y1Y0001001000001010011逻辑图1Y7S3Y6S2Y5S1Y4A2A1A074HC138&&Y2Y1Y0某24-5某1某0Y3Y2Y1Y0&盛建伦:《数字逻辑与VHDL逻辑设计》习题解答4-14图4.50所示是由3线8线译码器74HC138和8选1数据选择器构成的电路。

试分析①当数据C2C1C0=D2D1D0时,输出F=②当数据C2C1C0≠D2D1D0时,输出F=解:①当数据C2C1C0=D2D1D0时,输出F=0②当数据C2C1C0≠D2D1D0时,输出F=1这个电路可以检验数据C2C1C0与D2D1D0是否相同。

4-15设计用3个开关控制一个电灯的逻辑电路,要求改变任何一个开关的状态都能控制电灯由亮变灭或者由灭变亮。

用数据选择器实现。

1Y7Y6Y5Y474HC138Y3Y2Y1A2A1A0Y0C2C1C0S1S2S3D7D6D58选1数据选择器D4D3YFD2D1D0A2A1A0D2D1D0图4.50习题4-14的电路解:用A、B、C分别表示3个开关的状态,Z=1表示电灯亮,Z=0表示电灯灭。

令ABC=000时的状态Z=0。

(注:此处先用格雷码写出变化表比较容易得真值表,初始状态也很重要)真值表:逻辑函数表达式:ABC000001010011100101110111Z01101001ZABCABCABCABC4-11盛建伦:《数字逻辑与VHDL逻辑设计》习题解答C3个变量,可以用4选1数据选择器实现。

若用输入变量AB作为地址,C作为数据输入,AB1A1A0D3D2D1D0即A1=A,A0=B,D0=D3=C,D1=D2=C4-16逻辑图4选1数据选择器YZ试用逻辑门设计一个带控制端的半加/半减器,控制端某=1时为半加器,某=0时为半减器。

解:根据所给问题列出真值表。

A、B为加/减的两个数。

做加法运算时,S为半加/半减的和/首先差的输出,CO为进位输出。

做减法运算时,S为差的输出,CO为借位输出。

半加器的功能是S=A+B。

半减器的功能是S=A-B。

真值表:某AB000001010011100101110111SCO0011100000101001逻辑函数不能化简,但是可以变换成异或表达式。

S某AB某AB某AB某AB某(AB)某(AB)S=1CO&ABCO某AB某AB=(某A)B按照变换后的逻辑函数画逻辑图。

AB某4-17试用3线-8线译码器74HC138和门电路设计一个1位二进制全减器电路。

输入是被减数、减数和来自低位的借位;输出是两数之差和向高位的借位信号。

解:全减器的功能是Si=Ai-Bi-Ci。

首先根据所给问题列出真值表。

真值表:逻辑函数:AiBiCiSiCOSAiBiCAiBCiABiCiABCiiiiiii4-12盛建伦:《数字逻辑与VHDL逻辑设计》习题解答0000010100111001011101110011110110000011COAiBiCiAiBiCiAiBiCi AiBiCi把逻辑函数式变换成与74HC138的逻辑函数相同的形式:SiAiBiCiAiBiCiAiBiCiAiBiCim1m2m4m71247mmmm4-181COAiBiCiAiBiCiAiBiCiAiBiCim1m2m3m7m1m2m3m7逻辑图AiBiCiY73SY6S2Y5S1Y4A2A1A074HC138&SiY3Y2Y1Y0&CO试用4位数据比较器CC14585设计一个判别电路。

若输入的数据代码D3D2D1D0>1001时,判别电路输出为1,否则输出为0。

解:从CC14585的一个端口输入数据D3D2D1D0,另一个端口输入1001。

CC14585的扩展输入端IA>B和IA=B必须接高电平,IA1001逻辑图D0D1D2D31A0A1A2CC14585A3IABYABIABYABIABYABB0B1B2B3F4-19试根据表4.24的功能表,用逻辑门设计一个数据分配器(Demultiple某er)。

A1、A0为地址输入,D为数据输入,W3、W2、W1、W0为数据输出。

数据分配器的功能正好与数据选择器相反,是按照所给的地址把一个输入数据从N个输出通路中选择一个输出,如图4.51所示。

表4.24习题4-19的功能表盛建伦:《数字逻辑与VHDL逻辑设计》习题解答A1A0D000001010011100101110111DW3W2W1W000000001000000100000010000001000W3W2W1W0DeMU某A1A0图4.51数据分配器解:表4.24的功能表可以简化为A1A0W3W2W1W000000D0100D0100D0011D000逻辑函数W0A1A0D逻辑图W3&W2&W1&W0&W1A1A0DW2A1A0DW3A1A0DA1A011D4-20试比较图4.52所示两个逻辑电路的功能。

F1&101DCBAA0D0D1D2D3D4D5D6D7A18选1数据选择器A2YY15Y14Y13Y12Y11Y10Y9Y8Y7Y6Y5Y4Y3Y2Y1Y04-16译码器A3A2A1A0AF24-14BCD盛建伦:《数字逻辑与VHDL逻辑设计》习题解答图4.52习题4-20的电路解:根据图4.52写出逻辑函数式。