基于FPGA的I/O控制器的设计和实现

基于FPGA的数字调制器设计与实现

语 言 编 程 来 实 现 。接 着 就 可 以 用 Qu a r t u s l I 来完成综合 、 仿真 、 适配 、 下载到器件 。

和

两 个 频 点 间 变

1 D S P B u i l d e r 方 法 实 现 数 字 调 制 器

1 . 1 DDS原 理

( 2 )

式中 g , 是 持续 时间 为 T 的 单个矩形 脉 冲 , 而/ 2 的取 值

f 0 概 率为 P

一

{ 1 概 率 为 l 一 声

。 ’

结构 中的数字部分 , 具有 数控频 率合成 的功能 。相位 累加

2 F S K 信号 的产生通常有两种方 式 : 一种采用模 拟调

1 . 2 F S K、 A S K、 P S K 调 制 原 理

设 信 息 源 发 出 的是 由二 进 制 符 号 0 , 1组 成 的序 列 , 且 假 定 0符 号 出现 的概 率 为 P, 1符 号 出 现 概 率 为 l — P, 它 们

彼 此 独 立 。那 么 , 一 个 二 进 制 的频 移 键 控 信 号 可 以表 示 成 载波 的频 率 随二 进 制 基 带 信 号 在

为:

字频率合成技术 , 该技术特点是 : 频率分辨率高 、 频率变化

速度快 、 相位可连续 性变化 等 ] , 被广泛 应用 在数字 通信

系统 中, 是 信 号 生 成 的最 佳 选 择 。 一 个 基 本 的 D D S结 构 如图 1 所示 , 主要 由相 位 累 加 器 、 相位 调制器 、 正弦 R O M 查找表 、 基准时钟源和 D / A转换器构成 , 前三部分是 D D S

e z u s  ̄ ( t ) 一{ A FS K 信 号 可 以 看 成 是 两 个 不 同载 频 的 2 AS K

乒乓球游戏机EDA课程设计完整版本

乒乓球游戏机EDA课程设计完整版本

本文主要介绍了一款基于FPGA可编程硬件的乒乓球游戏机的设计。

本文将重点介绍

如何利用FPGA技术来搭建可编程硬件电路,如何使用Verilog HDL语言来设计数字电路,如何使用Quartus II环境来实现复杂任务,以及如何利用FPGA来完成乒乓球游戏机的EDA课程设计。

首先,在设计乒乓球游戏机的FPGA可编程硬件系统时,最重要的是硬件架构设计,

选择固定板来作为FPGA控制器,能够有效地根据游戏需求控制其各个功能,保证游戏机

运行稳定性和可靠性。

为了满足乒乓球游戏机的需求,FPGA控制器引入Verilog HDL语言,用数字电路的方式进行设计,从而构建出模拟端口,使用I/O 端口对乒乓球系统进行控制,其内部控制器模块实现了所有的乒乓球游戏逻辑功能。

在设计主板的时候,FPGA

中实现的硬件电路会结合安装在主板上的器件,比如七段LED显示器、微型键盘、LED灯等,从而使乒乓球游戏机更加复杂,实现更多的功能。

接下来,使用Quartus II环境,实现乒乓球游戏机的EDA课程设计。

首先,在Quartus II中编写Verilog HDL语言编程,利用FPGA可编程硬件系统设计乒乓球游戏逻辑,构建出特定的模块,实现系统的功能。

其次,编写控制逻辑,运用Verilog HDL语言

编程,在FPGA硬件中得到设计的图像图案,以及搭建复杂的乒乓球游戏的系统结构,实

现乒乓球游戏的控制逻辑功能。

最后,完成了乒乓球游戏机的EDA课程设计。

基于FPGA的I2C控制器的实现

I mp l e me nt a t i o n o f 1 2 C Co n t r o l l e r Ba s e d o n FPGA

W ANG Lo n g-f e i , LANG Ba t—h ua

( S c h o o l o f E l e c t r o n i c I n f o r ma t i o n E n g i n e e r i n g , X i ’ a l l T e c h n o l o g i c a l U n i v e r s i t y , X i ’ a n 7 1 0 0 2 1 机 技 术 与 发 展

COMPU TER TEC HNOLOGY AND DEVEL 0P MENT

2 0 1 3年 3月

Vo1 . 2 3 No . 3 Ma r . 20l 3

基于 F P GA 的 1 2 C控 制器 的 实现

王龙飞 , 郎宝华

i n i t i l a i z a i t o n s t a t e r t ns a i t i o n d i a g r a m, i f n l a l y u s e t h e Qu a r t u s s o f t w re a f o r s i mu l a t i o n , he t e x p e r i me n t s s h o w t h a t d a t a r t ns a m i s s i o n c o mp l i e s

Ab s t r a c t : Th e p u r p o s e i s t o s t u d y t h e I 2C b u s , i t h a s he t i nt e r f a c e c a b l e a n d c o n ro t l s i mp l e d e v i c e s a r e pa c k a g e d i n s ma l l , h i g h e r c o ml n u- n i c a t i o n s p e  ̄ . . d。 e r e, s o s e l e c t t he S AA7 1 1 3 a s v i d e o d e c o d e r c h i p. I t g i ve s a矾 e f a c c o u n t o f he t d a t a t r a n s mi s s i o n t i mi n g o f t h e I 2 C b us p r o t o c o l 。 he t b a s i c f u n c t i o n s o f he t a n a l o g v i d e o d e c o d i n g c h i p S AA71 1 3 wo r k s a nd a s s o c i a t e d r e g i s t e r s e t , nd a p r e s e n t s a S AA7 1 1 3 i n i — t i li a z a t i o n a p p r o a c h ba s e d o n F P GA , o v e r v i e ws e a c h mo d u l e o f he t I 2 C b u s i n d e t a i l , nd a i s g i v e n i n he t r e g i s t e r c o n ig f u r a t i o n o f he t c h i p

基于FPGAIP核的FIR设计与实现

佳的频率特性和衰耗特性 , 无论通带还是阻带都

较 为平坦 , 过渡 带窄 , 好地接 近理 想滤波 器 的响 更

应。

须确 保 已 经 安 装 了 D P B i e 具 。进 入 I S ul r工 d P

( 方通 用 电子集 团有 限 公司微 电子部 苏州 256 ) 北 113 摘 要 随着数 字 电路技 术 的 高速 发展 和 高性 能 F G 的普及 , PA 为解 决二 频 机械 抖 动偏 频激 光 陀

螺 中的 因机械 抖动 带 来的信 号噪 声提 供 了新 的选择 和方 法 。FR滤 波 器可 以满足 系统对 幅度 和相 位特 I 性 的严 格要 求 , 免 模 拟 滤 波 器 的温 漂 和 随机 噪 声 等 问题 , 避 而且 具 有精 确 的线性 相 位 和稳 定 的 系统。

免费 I oe 同 时结 合 Ma w rs 司 的 MA . P C r, t ok 公 h T

数字低通滤波器是对高速采样 的数据进行滤

波, 滤除掉 机抖 陀螺 输 出信 号 中随机 抖 动 和其 他 因素 造成 的高频 噪声 。 由于二 频机抖 陀螺 的抖动 频 率一 般 在 30 z~ 0 H 左 右 , 速 采 样 频 率 0H 40 z 高 选 为 1H , 以满 足 采 样定 理 要 求 。1H k z可 k z的定 时采样信 号可 以在 F G 内对 时钟使 能 得到 。数 PA 字低通滤 波器 采用 FR中的等波纹 逼近法 进行设 I 计, 设计 指标 : 采样 频率 为 1H , k z通带下 限截止频 率为 10 z阻带 上 限截 止频 率 为 30 z且 通 带 0H, 0H , 内波 纹 小 于 0 00d 阻 带 内 幅 度 衰 减 大 于 . 0 1B,

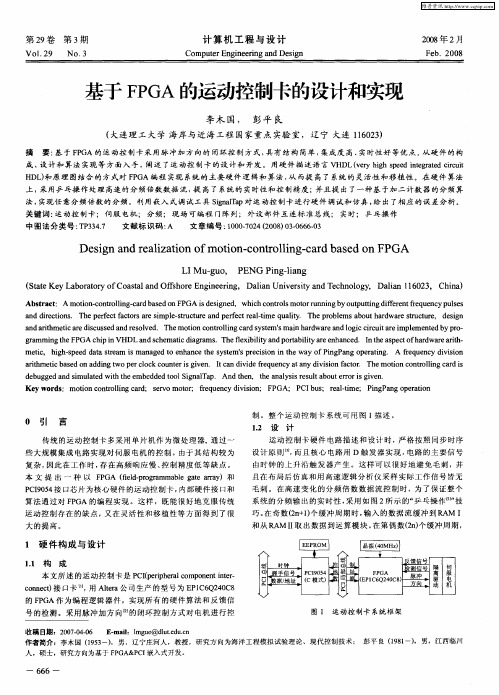

基于FPGA的运动控制卡的设计和实现

关键 词 : 动 控 制 卡 ; 伺 服 电机 ; 分 频 ; 现 场 可 编 程 门阵 列 ; 外 设 部 件 互 连 标 准 总 线 ; 实 时 ; 乒 乓 操 作 运

me i, h g -p e aa s e m n g d t n a c e s se Sp e iin i e wa f i g a g o e ai g A e u n y d vso t c i h s e d d t t a i ma a e e h n et y t m’ r cso t y o n P r s o h nh P n p rt . n r f q e c i ii n a i me i a e n a d n e l c o n e ie . I C i i efe u n ya y d v s n fco  ̄ Th t nc n r l n a di r h t b s do d ig t p r o k c u tr s v n t a dv d q e c t t c wo c ig n r n a i ii t r o a emo i o t l gc o o i r s d b g e n i ltd wi ee e d dt o i n l a . An e , t ea a y i r s l a o t ro ie . e u g da ds mu a e t t mb d e l g aT p hh o S d t n h l ss e u t b u r r s v n h n e ig Ke r s mo i nc n o l g c d s r o moo ; fe u n y d v s n F GA; P u ; r a— me P n P go e a in ywo d : t o t l n a ; e v t r r q e c i ii ; P o r i r o CI s e l i ; i g a p r t b t n o

基于FPGA的数字PID控制器设计

实 现 数 字 P D控 制 器 的设 计 ,提 高 系 统 的 运 算 速 I 度 、 少系统 的体 积 、 强其 可靠 性 。 减 增

2 各 功 能模 块 的 设计 1 P D 控 制 算 法 I

在此将 详 细描述 各模块 的具 体实 现过程 。使 用

完整 的 P D控 制表 达式 为 : I

式() 2 为增量 型 P D控 制算 法 。从式 ( ) I 2 可看 出增 量

分 、积分参数 的控制策 略来 达到 最佳 系统 响应 和控

制效 果 。但 是采 用 微处 理 器来 实 现 时 . 能完 全 避 不

型 控制算 法 只与前 三次 采样值 有关 ,不需 要大量 的

数据 存储 和 累加 . 因而不 易引起 误差 累积 , 计算量 小

馈 值 y 求偏 差 , ) 然后 把 所 得 的 偏差 值 传 给 后续 模 块进 行处 理 , 图 2所示 。复位 信号 rst 如 ee 为低 电平 时 复位 , 则 , 否 在输 入 时钟 的上 升沿 到 达 时 , 在使 能

收 稿 日期 :o 9 0 一 3 2 o — 9 l

作 者简 介 : 昭 明 (9 5 , , 陈 18 一)男 四川 人 , 国航 天 科技 集 团第 四研 究 院 4 1 硕 士研 究 生 , 究 方 向为 测 试 计 量技 术及 仪 器 。 中 0所 研

且实 时性 好 。其结构 原理 如 图 1 所示 。

免程序 跑 飞和计算 机误 动作 对整 个控制 系统 的破 坏

性 影 响 。现场 可编 程 门阵列 F G 的出现 为 P D控 PA I 制 器 的设 计提 供 了新 的实现手 段 。 P A集成度 高 、 FG 体 积小 、 功耗低 、 靠性 高 、 可 设计 方 法灵 活 , 仅具有 不 反 复编 程 、 复探 险 、 复使 用 等特 点 , 能 得 到实 反 反 更

基于FPGA的图像数据缓存控制器设计

3 S D R AM 初始化

系统 上 电复 位 后,必须要 有 S DR A M 初始 化 的过程 ,其 中 S D R AM 初始 化模块 如 图 1 示 :首 先要 有 2 0 0 u s

缓存控制器也就成为了系统设计的主要 内容¨ J . S D R A M 其全称叫同步动态随机访问存储器, 它是嵌入式系统

的重要 部件 ,因其 成本低 、 容 量 大、存取 速度 快和 功耗 低 等优 点被 广泛 应 用于缓 存模 块 . 但是 S DR A M 比普通 的

R A M 存储器操作要复杂很多,随着 E D A技术 的发展, 采用硬件描述语言在 F P G A 上实现高效简单的 S D R A M 控制器 已经成为现实 J . 这种控制器移植方便、代码简单容易理解, 更重要的是能够高效的完成任务. 为提高其 与外 界通 信 的速 度,该控 制器 采用 异步读 写 F I F O 作 为跨 度,通 过控 制 S D R AM 存 储器 的读 写,实现 对高 速 图像 数据 的实 时缓 存 .

指令, 只需要按照所定的 S D R A M 系统时钟把相应的参数配置好, 比如说突发长度、 行列延时等等. 待初始化模 块 完成 后, S DR AM 就可 以进 入正常 的工 作状 态 了.

’ ’  ̄ , I - 1 I 休 l 卜 l - I - . - v . , . j 司 I { j ‘

M … a 一 2 … O l 3

基于 F P G A 的图像数据缓 存控 制器设计

向强 , 蔡威, 姬 高 飞,庞 啸龙

( 西 南 民族 大 学 电 气信 息 工程 学 院,四川 成 都 6 1 0 0 4 1 )

《基于FPGA的现代数字系统设计》课件第1章

基于EDA技术的所谓“自顶向下”的设计方法正好相 反,它主要采用并行工程和“自顶向下”的设计方法,使开 发者从一开始就要考虑到产品生成周期的诸多方面,包括质 量、成本、开发时间及用户的需求等。该设计方法首先从系 统设计入手,在顶层进行功能划分和结构设计,由于采用高 级语言描述,因此能在系统级采用仿真手段验证设计的正确 性,然后再逐级设计底层的结构,用VHDL、Verilog HDL 等硬件描述语言对高层次的系统行为进行电路描述,最后再 用逻辑综合优化工具生成具体的门级逻辑电路的网表,其对 应的物理实现级可以是印刷电路板或专用集成电路。“自顶 向下”设计方法的特点表现在以下几个方面:

EDA技术融合电子技术、集成电路制造技术、计算机 技术和智能化技术等,以计算机为工作平台,以相关的 EDA软件为开发工具,以大规模可编程逻辑器件为设计载 体,以硬件描述语言(Hardware Description Language)为系统 逻辑描述的主要方式,自动完成系统算法和电路设计。 EDA技术已有30多年的发展历程,大致可分为20世纪70年 代的计算机辅助设计(CAD)阶段、80年代的计算机辅助工程 (CAE)阶段和90年代后的电子系统设计自动化(EDA)阶段。

3) 集设计、仿真和测试于一体 现代的EDA软件平台集设计、仿真、测试于一体,配 备了系统设计自动化的全部工具,这些工具包括:多种能兼 容和混合使用的逻辑描述输入工具以及高性能的逻辑综合、 优化和仿真测试工具。电子设计师可以从概念、算法、协议 等开始设计电子系统,将电子产品从电路设计、性能分析到 设计出IC版图或PCB版图的整个过程在计算机上自动处理完 成。

PLD从20世纪70年代发展到现在,已形成了许多类型的产品,其结 构、工艺、集成度、速度和性能都在不断地改进和提高。最早期的可编 程逻辑器件有可编程只读存储器(PROM)、紫外线可擦除只读存储器 (EPROM)和电可擦除只读存储器(E2PROM),其后出现了结构上稍复杂 的可编程芯片,它能够完成各种数字逻辑功能,这一阶段的产品主要有 可编程阵列逻辑(PAL)和通用阵列逻辑(GAL)。由于受到结构规模的限制, 以上这些PLD只能完成简单的数字逻辑功能,称为简单低密度PLD器件。 进入90年代后伴随着铜微处理器硅芯片技术的发展,可编程逻辑器件在 体积与性能上得到了更良好的体现,出现了复杂高密度PLD器件,如 1984年Xilinx公司发明的现场可编程门阵列FPGA (Filed Programmable Gate Array)以及随后出现的复杂可编程逻辑器件CPLD(Complex Programmable Logic Device),它们直接面向用户,具有极大的灵活性和 通用性、使用方便、开发效率高、成本低以及工作可靠性好等特点,因 而很快得到普及和应用,发展非常迅速。

基于FPGA的CAN控制器软核的设计与实现

验 收 B 波器

A F C

冲 器 、接 收 缓 冲 器 和验 收滤 波 器 7 功 能模 块 ,并 设 计 寄 存器 组 【 。 个 3 ]

总线 控制 系 统 的方法 ,为 基 于 C AN 总 线 的控 制 应用 提 供 了一个 较 好 的 思路 。 由于 软 核是 具有 特 定 电路 功 能 的硬 件 描 述语 言程 序 ,

介质 访 问控 制子 层 ( C) MA

数 据封 装 / 装 拆

支 持 可重 用 、可 裁剪 、可 移植 , 因此 可 增强 系 统 设 计 的效 率 和 灵

1

引言

S C 利用 可 编 程 逻辑 技 术 把 整 个 电子 系 统 包 括 处理 器 、存 储 器 、 总线 和 总 线 控 制器 、I 口、 OP / O

DS 、锁 相 环 等集 成 在 一 个 单 片上 ,是 一 种特 殊 的嵌 入 式 系 统芯 片 。S P 设 计 的实 质 是把 各 个 子 系 P OC 统 的 I 组 装 为 一个 大 的片 上系 统 。随着 高密 度 的 F G 的 出现 以及 S P 技术 的发 展 ,基 于 F GA P核 PA OC P 的嵌入 I P核 的片上 可 编 程 系统 的实 现方 法 也 得 到 了广 泛 的应用 。 C AN 总线 因具 有 可靠 性 好 、传 输 速 率 高 、传 输 距 离长 等 优 点而被 广泛 地 应 用 在工 业 现场 监 控 设 备 中 。C AN 总 线 设计 的关 键 是 C N 控 制 器 的 设计 和 使 用 ,通 常 的 方法 是 采 用 单 片机 加 专 用 C A AN 控 制 器 芯 片 ,或 选 择 内嵌 C N 控 制 器 并 带有 C A AN 接 口的单 片 机 【 ] 照现 代 电子 系 统 设计 理 念 ,上述 系 l 。按 , 2 统 集 成度 不 高 ,可靠 性 较 低 ,通 用 性 也不 好 。可将 C N 控 制 器 设计 成 I A P软核 ,通 过 S C技 术在 单 OP 片 F GA 中构 建 C P AN 总 线 系统 来 解 决 上述 不 足 。同时 ,还 可 在 实现 C N 控 制 器 的 F G 的剩 余 资源 A PA 上 集 成其 他 自行 设计 的数 字 电路 ,有 效地 减 少 外 围芯片 的数 量 。

基于FPGA的电梯控制器系统设计

第2期贺敬凯,王瑞春,万学元,潘晓宁,郑芙蓉,李晓堂:基于丌'GA的电梯控制器系统设计59SO:onfloorl,表示在楼层1;S1:dooropen_up,上升过程中,电梯开f]Ss;S2:doorclose_up,上升过程中,电梯关门;S3:up_lift,表示电梯上升一层;S4:dooropen_down,下降过程中,电梯开fq5s;s5:doorclosedown,下降过程中,电梯关门;56:down_lift,表示电梯下降一层。

各状态在满足一定的条件下转换,具体状态转换如图3所示。

图3电梯控制器状态转换图Fig.3Statechartofelevatorcontroller图3中的状态转换条件如表1所示。

表1电梯控制器状态转换条件Tab.1StatechangeconditionofelevatorcontroHer现态次态转换条件SOSI下一个时钟S1SIup[pos]=lstop[pos]=lSIS2Sl下一个状态不为Sl时S2Slup[pos]=lstop[posl=ls2s3S2下一状态不为Sl,-臣stop[pos+i]=lup[Ires+i]=1down[pos+i]=1(i>0.1Lpos+i<=N)S2s4S2T--.R..态,为Sl和S3,Jldown[pos]=1s2s5S2下一状态不为S1/¥3/¥4,且stop【pos—i】-lup[pos-i]=1down[pos-i]=l(i>0.Epos-i>=O)S252S2下一状态不为Sl,S3,S4,S5时S3S2完成pos=pos+l,下一个时钟S4s4down[posl=!orstop[posl=1s4S5S4下一个状态不为s4时S5S4down[pos]=lstop[pos]=lS5S6S5下一状态不为s4,_l王stop[pos—i】:lup[pos-i]=ldown[pos-i]=1(i>0.Epos-i>=0)S5S1S5下一状态不为s4和s6,.臣up[pos]=1S5s2S5下一状态不为¥4/¥6/S1,且stop【pos+i】=lum)os+i】=ldown[pos+i]=1(i>09pos+i<=N)S5S5S2下一状态不为Sd/S6/S1/¥2时s6s5完成pos=pos-I,下一个时钟上表中,pos表示当前楼层,up[pos】、down[pos】、stop[pos]分别表示当前楼层的向上、向下、和停止铵钮的状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

o n t h e F P GA p r o g r a mma b l e t e c h n o l o g y h a s b e e n d e s i g n e d a n d i mp l e me n t e d u s i n g P C I E x p r e s s b u s .T h i s p l a t f o r m h a s t h e c a p a b i l i t y o f g e n e r a t i n g a n y k i n d o f p a c k e t a t t h e t r a n s a c t i o n l a y e r o f P CI E x p r e s s , a n d i t p r o v i d e s a b a s i c p l a t f o r m f o r t h e r e s e a r c h e s o v e r t h e ma li c i o u s a c t i o n s b a s e d o n t h e I / O c o n t r o l l e r . KEYW ORDS: h fo r ma t i o n s y s t e m; P r o g r a mma b l e t e c h n o l o y; g A t t a c k

中图 分 类 号 : T P 3 9 3 . 0 8 文献标识码 : A

De s i g n a nd I mp l e me n t a t i o n o f FPG A - Ba s e d I /O Co nt r o l l e r

HUAI L i a n g -l i a n g , Fe r n a n d L o n e S a n : 1 0 0 6 — 9 3 4 8 ( 2 0 1 3 ) 叭一 0 2 5 4 — 0 5

计

算

机

仿

真

2 0 1 3 年1 月

基于 F P GA 的 I / O 控 制 器 的 设 计 和 实 现

怀靓 亮 , F e r n a n d L o n e S a n g

ABS TRACT : T h e a t t a c k s o n t h o s e c o mp u t e r i n f o r ma t i o n s y s t e ms c a n b e b a s i c a l l y c a t e g o r i z e d i n t o b a s e d o n t h e C P U a n d b a s e d o n t h e I / O c o n t r o l l e r .At t a c k s b a s e d o n t h e C P U h a v e b e e n we l l s t u d i e d ,a n d ma n y ma t u r e c o u n t e r me a s — u r e s h a v e b e e n l a r g e l y i mp l e me n t e d .Ho w e v e r ,a t t a c k s b a s e d o n t h e I / O c o n t r o l l e r h a v e b e e n l e s s s t u d i e d ,a n d f e w

( 1 .A V I C R a d a r a n d A v i o n i c s I n s t i t u t e , Wu x i J i a n g s u 2 1 4 0 6 3, C h i n a ; 2 .L A A S - C N R S , T o u l o u s e , 3 1 0 2 8 ,F r a n c e )

( 1 .中航工业 雷达与 电子设备研究院 , 江苏 无锡 2 1 4 0 6 3 ; 2 .L A A S — C N R S, 法国 图卢兹 3 1 0 2 8 ) 摘要 : 对 于计算机信息系统受到攻击基本 上可 以分为基于 C P U和 I / O控制器这两种。对 于 C P U的攻击 已经被深入研究 , 各 种成熟 的对策也被, 泛的应用。但 是对于 I / O控制器攻击的研究非 常缺乏有效的保护机制 。为 了研究关 于 I / O控制器 的 攻击 , 使用 F P G A 可编程技术设计 和实现 了一款 P C I E x p r e s s 总线的平台。平 台能产生任意种类的关于 P C I E x p r e s s 事务层 的 信息包 , 为研究各类 I / O控制器的攻击 提供了基础 。 关键词 : 信 息系统 ; 可编程技术 ; 攻击