利用msi设计组合逻辑电路

实验六 MSI组合逻辑电路的逻辑功能测试

实验六MSI 组合逻辑电路的逻辑功能测试一、实验目的熟悉中规模全加器、译码器、数据选择器组件的逻辑功能、外形及外引线排列。

二、实验仪器与器材1.XST-5B 数字电路实验装置、实验模板 2.集成电路:74LS283、74LS138、74LS153、74LS151 3.导线若干、+5V 电源 三、预习要求预习半加器、全加器、译码器、数据选择器的逻辑功能。

四、实验内容与步骤 1.全加器的逻辑功能测试表6-1是全加器的真值表,其中i A ,i B 表示两个加数,1i C -表示来自低位的进位,i S ,i C 表示相加后得到的和及进位。

1i i i i S A B C -=⊕⊕ 1()i i i i i i C A B C A B -=⊕+将全加器的输入端i A ,i B ,1i C -分别接逻辑电平,输出i S ,i C 接状态显示灯(LED ),按表6-1所列i A ,i B ,1i C -的状态,测试i S ,i C 的相应状态,将测试结果与表6-1进行比较。

2.译码器逻辑功能测试表6-2是3线/8线译码器74LS138的真值表。

按表中给定的输入状态。

测试输出,将测得的结果与表6-2进行比较。

表6-23.数据选择器逻辑功能测试①表6-3是4选1数据选择器74LS153的功能表,按表中给定的输入状态。

测试输出,将测得的结果与表6-3进行比较。

表6-3②八选一数据选择器74LS151功能测试(自己根据管脚排列和测试结果写出功能表及函数表达式)五、实验报告1、整理实验结果、图表,并对实验结果进行分析讨论。

2、写出各芯片的函数表达式。

3、总结本次实验体会。

高二物理竞赛课件电路中常用MSI组合逻辑器件及应用

E3 E2 E1 E0 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 ×××× ×××× ×××× ×××× ×××× ××××

Dn An Bn C n An BnCn An Bn C n An BnCn Cn1 Bn C n An C n An Bn 当用异或门实现电路时,写出相应的函数式为

Dn An Bn Cn Cn1 An BnCn AnBn Cn BnCn

An (Bn Cn ) BnCn An (Bn Cn ) BnCn

该电路输入为8421 BCD码,输出为余3码,因此它是 一个四输入、四输出的码制变换电路,其框图如图4-7(a) 所示。根据两种BCD码的编码关系,列出真值表,如表4-5 所示。由于8421 BCD码不会出现1010~1111这六种状态, 因此把它视为无关项。

② 选择器件,写出输出函数表达式。

题目没有具体指定用哪一种门电路,因此可以从门 电路的数量、种类、速度等方面综合折衷考虑,选择最 佳方案。该电路的化简过程如图4-7(b)所示,首先得出最 简与或式,然后进行函数式变换。变换时一方面应尽量 利用公共项以减少门的数量,另一方面减少门的级数, 以减少传输延迟时间,因而得到输出函数式为

10 1 (b)

1 ×× E0

③ 画逻辑电路。

该电路采用了三种门电路,速度较快,逻辑图如图4-8所示。

表 4 – 5 例4-4真值表

AB C D

00 0 0 00 0 1 00 1 0 00 1 1 01 0 0 01 0 1 01 1 0 01 1 1 10 0 0 10 0 1 10 1 0 10 1 1 11 0 0 11 0 1 11 1 0 11 1 1

其中 (Bn Cn ) 为Dn和Cn+1的公共项。

MSI组合电路的HDL设计

实验五MSI组合电路的HDL设计一、实验目的:继续熟悉实验箱的使用;掌握用HDL语言设计MSI组合电路的方法。

二、实验设备与元器件:1、数字电路与系统实验箱1台2、计算机1台3、Quartus II 软件1套三、实验任务:用HDL设计:3-8译码器、显示译码器、数据选择器。

四、实验要求:1.3-8译码器a)8个输出在实验箱上用8个LED发光二极管表示;b)3个输入连接实验箱上的3个按钮;c)附加一个片选使能端。

2.显示译码器a)输入为四位BCD码;b)输出驱动一个七段共阴极数码管;c)附加一个片选使能端。

3.四选一数据选择器a)四个数据输入端(D3,D2,D1,D0)和两个数据选择输入端(A1,A0),一个数据输出端(Y);b)附加一个片选使能端。

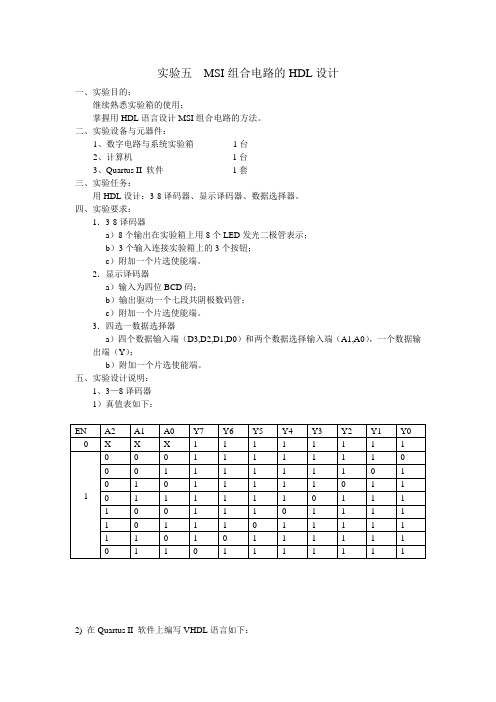

五、实验设计说明:1、3—8译码器1)真值表如下:EN A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 0 X X X 1 1 1 1 1 1 1 11 0 0 0 1 1 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 0 1 0 1 0 1 1 1 1 1 0 1 10 1 1 1 1 1 1 0 1 1 11 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 12) 在Quartus II 软件上编写VHDL语言如下:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY fab5_1 ISPORT(A2,A1,A0,en : IN bit;Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0: OUT bit);END fab5_1;ARCHITECTURE a OF fab5_1 ISsignal tin:bit_vector(2 downto 0);signal tout:bit_vector(7 downto 0);BEGINtin<=A2&A1&A0;PROCESS (tin,en)BEGINIF en = '0' THENtout<="11111111";ELSEIF tin="000" thentout<="11111110";elsif tin="001" thentout<="11111101";elsif tin="010" thentout<="11111011";elsif tin="011" thentout<="11110111";elsif tin="100" thentout<="11101111";elsif tin="101" thentout<="11011111";elsif tin="110" thentout<="10111111";elsif tin="111" thentout<="01111111";END IF;END IF;Y0<=tout(0);Y1<=tout(1);Y2<=tout(2);Y3<=tout(3);Y4<=tout(4);Y5<=tout(5);Y6<=tout(6);Y7<=tout(7);END PROCESS;END a;3)仿真图如下:4)设置引脚如下:5)再编译一遍。

MSI组合电路逻辑功能测试

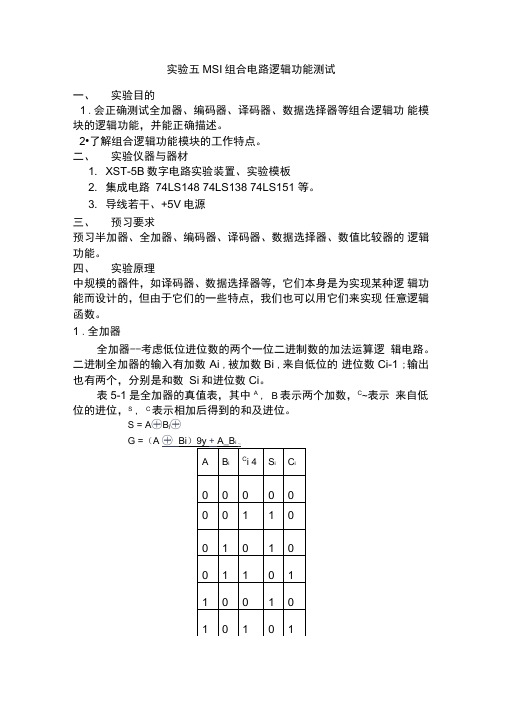

实验五MSI组合电路逻辑功能测试一、实验目的1 .会正确测试全加器、编码器、译码器、数据选择器等组合逻辑功能模块的逻辑功能,并能正确描述。

2•了解组合逻辑功能模块的工作特点。

二、实验仪器与器材1. XST-5B数字电路实验装置、实验模板2. 集成电路74LS148 74LS138 74LS151 等。

3. 导线若干、+5V电源三、预习要求预习半加器、全加器、编码器、译码器、数据选择器、数值比较器的逻辑功能。

四、实验原理中规模的器件,如译码器、数据选择器等,它们本身是为实现某种逻辑功能而设计的,但由于它们的一些特点,我们也可以用它们来实现任意逻辑函数。

1 .全加器全加器--考虑低位进位数的两个一位二进制数的加法运算逻辑电路。

二进制全加器的输入有加数Ai ,被加数Bi ,来自低位的进位数Ci-1 ;输出也有两个,分别是和数Si和进位数Ci。

表5-1是全加器的真值表,其中A, B表示两个加数,C~表示来自低位的进位,S, C表示相加后得到的和及进位。

S = A㊉B j㊉G =(表5-1全加器真值表2. 编码器编码器是一种常用的组合逻辑电路,用于实现编码操作。

编码操作就是将具体的事物或状态表示成所需代码的过程。

按照所需编码的不同特点和要求,编码器主要分成二类:普通编码器和优先编码器。

普通编码器:电路结构简单,一般用于产生二进制编码。

包括:a. 二进制编码器:如用门电路构成的4 —2线,8 —3线编码器等。

b. 二一^进制编码器:将十进制的0〜9编成BCD码,优先编码器:当有一个以上的输入端同时输入信号时,普通编码器的输出编码会造成混乱。

为解决这一问题,需采用优先编码器。

如8线一3线集成二进制优先编码器74LS148 10线一4线集成BCD码优先编码器74LS147等。

厶 A h A A h土亓ST I-61X X X X X X X X111110111111111111000X X X X X X X000Q1010X X X X X X001010110X X X X X010Q101110X X X X01101011110X X X100010111110X X1Q10101111110X1100101111111011101表5-2 8线3线编码器功能表3. 译码器译码器是一个多输入、多输出的组合逻辑电路。

msi组合功能件的应用实验原理

MSI组合功能件的应用实验原理介绍MSI(Medium-Scale Integration)是一种中等规模集成电路,一般包含多个逻辑门组合而成的功能件。

在本文中,我们将讨论MSI组合功能件的应用实验原理。

实验目的本实验旨在帮助学生了解和理解MSI组合功能件的工作原理,并通过实际操作学习如何使用MSI组合功能件来解决实际问题。

实验材料•实验板•MSI组合功能件(如:多路选择器、译码器等)•连接线•电源实验步骤1.准备实验材料和设备。

2.将实验板连接到电源。

3.根据实验需求,选择合适的MSI组合功能件,并将其连接到实验板上。

4.根据实验要求,在实验板上插入适当的连接线。

5.开始实验。

–根据实际问题,设置输入信号和连接线。

–使用适当的MSI组合功能件进行逻辑运算。

–观察输出结果,并进行实验记录。

–分析结果并得出结论。

6.关闭电源,整理实验材料和设备。

实验注意事项•在操作实验板和连接线时,务必小心谨慎,避免电路短路或其他安全问题的发生。

•根据实验要求,选择适当的MSI组合功能件,确保实验的准确性和有效性。

•在实验过程中,应注意观察和记录实验结果,并根据结果进行结论。

实验案例以下是一个实验案例,以进一步说明MSI组合功能件的应用原理。

问题:假设有一台控制系统,输入信号为A、B、C和D,输出信号为X。

根据以下逻辑表达式来设计一个控制电路,当A为1且B为0时,输出信号X为1,否则输出为0:X = A’BC’D + AB’CD + ABC’D + ABCD。

解决方案: 1. 根据逻辑表达式,我们可以使用多路选择器MSI组合功能件来实现控制电路。

2. 设计时,我们需要设置四个输入信号(A、B、C和D)和一个输出信号(X)。

3. 根据逻辑表达式,可以将A’BC’D、AB’CD、ABC’D和ABCD作为输入信号的组合,将其分别连接到多路选择器的不同输入口。

4. 设将控制线连接到多路选择器的控制引脚上,并根据逻辑表达式设置控制线的值,以实现所需的逻辑运算。

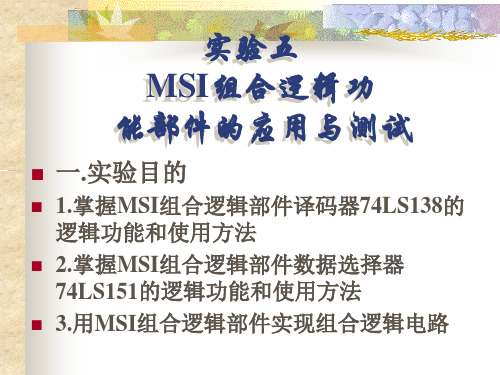

实验五MSI组合逻辑功能部件的应用与测试

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

74LS138

A0 A1 A2

S1 S2 S3

(a)

(2) 74LS138的功能

16 15 14 13 12 11 10 9

VCC Y0 Y1 Y2 Y3

Y4 Y5 Y6

3线—8线译码器

A0 A1 A2 S2 S3 S1 Y7 GND 12345678

(b)

3. 74LS151数据选择器逻辑功能测试

将74LS151地址端、数据端、使能端接逻辑开关,输出端 接逻辑电平显示器,逐项测试74LS151的逻辑功能。

4. 用74LS151设计三变量表决电路,连接电路并验证结果。

(b)

7ห้องสมุดไป่ตู้LS20

图中,A0、A1、A2为地址输入端,S1、S2、S3为使能端。当

S1=1, S2+S3=0时,译码器工作。地址码所指定的输出端有 有用信号(0)输出,其它所有输出端均为无用信号(1)输 出。74LS138实际上是一个最大项产生器。即:

Y0=A2+A1+A0 Y2=A2+A1+A0 Y4=A2+A1+A0 Y6=A2+A1+A0

74LS151可用做多通道传输,数码比较以及实现组合逻辑 函数等。

三.实验内容

1. 74LS138译码器逻辑功能测试

将74LS138使能端及地址端分别接至逻辑电平开关输出口, 8个输出端依次连接到逻辑电平显示器输入口上,然后拨动开 关,逐项测试74LS138的逻辑功能。

2. 用74LS138和适当的逻辑门设计一个全加器,连接电路 并验证结果。

2. 74LS151的功能与应用 (1)74LS138的逻辑符号及引脚排列如图(a)、(b)

数字电路与逻辑设计基础实验 MSI时序逻辑器件应用

cp A2B2C2D2E2F2G2数字电路与逻辑设计基础实验实 验 五:MSI 时序逻辑器件应用(一)实验目的1、掌握MSI 时序器件74LS160、74LS194的逻辑功能和使用方法2、掌掌握MSI 时序逻辑电路的分析方法(二)预习要求复习时序逻辑电路的分析和设计、常用集成时序逻辑器件及应用的相关知识(三)实验器材(1)直流稳压电源、数字逻辑电路实验箱、万用表、示波器(2)74LS00、74LS48、74LS160、74LS194(四)实验内容和步骤2、同步十进制计数器与74LS161类似,MSI 同步十进制计数器74LS160可以实现74LS161几乎所有的逻辑功能。

两者之间不同的仅在于:74LS161是二进制计数,而74LS160是十进制(BCD 码)计数。

其他诸如预置数、异步清零、计数保持等功能完全相同。

关于74LS161详细的逻辑功能请参与相关资料。

用74LS160和74LS48芯片建立如图所示的实验电路(74LS160引脚编号旁边标注的是对应引脚的逻辑名称之别名)。

计数器的时钟脉冲输入端CP 接单脉冲,进位输出端O c 、计数输出端Q 、D Q 、C Q B 、Q A 各接一个LED ,并且最好按照从左到右的顺序排列。

让74LS160从0000 A B C D Q Q Q Q (十进制数“0”)开始工作,按动单脉冲按钮逐个送入计数脉冲。

每送入一个脉冲就记下相应的时钟脉冲计数以及输出端A B C D C Q Q Q Q O 、、、、的状态变化和数码管显示出的数字。

送入第十个脉冲时,状态转移图:波形图:CPQ DQC Q BQ A。

multisim组合逻辑电路

Multisim是一款流行的电子设计自动化(EDA)工具,用于模拟和设计电子电路。

在Multisim中,组合逻辑电路是一种基本的数字电路,它不涉及存储元件(如触发器),只涉及逻辑门和逻辑操作。

在Multisim中设计组合逻辑电路的一般步骤如下:

1. 创建新的电路图:打开Multisim软件,创建一个新的电路图。

2. 添加元件:从元件库中选择所需的逻辑门(如AND、OR、NOT 等)并添加到电路图中。

3. 连接电路:使用导线将逻辑门连接起来,形成所需的逻辑电路。

4. 设置输入和输出:根据需要设置输入和输出端子,以便输入信号和输出结果。

5. 运行仿真:单击仿真按钮,观察电路的行为。

你可以改变输入信号的电压,观察输出信号的变化。

6. 分析和验证:分析仿真结果,验证电路是否符合预期的功能。

7. 保存和导出:保存电路图以供将来使用或导出为其他EDA工具或文档。

需要注意的是,组合逻辑电路的设计需要根据具体需求进行选择和组合逻辑门,以满足特定的功能和性能要求。

此外,组合逻辑电路的可靠性通常不如时序逻辑电路,因为它没有存储元件来保持状态。

因此,在设计复杂的数字系统时,通常会使用时序逻辑电路。

实验4 组合逻辑电路设计

实验四组合逻辑电路研究(设计性实验)一、实验目的1.掌握用SSI器件实现组合逻辑电路的方法。

2.熟悉各种MSI组合逻辑器件的工作原理和引脚功能。

3.掌握用MSI组合逻辑器件实现组合逻辑电路的方法。

4.进一步熟悉测试环境的构建和组合逻辑电路的测试方法。

二、实验所用仪器设备1.Multisim10中的虚拟仪器2.Quartus II中的功能仿真工具3.GW48-EDA实验开发系统三、实验说明1. 组合逻辑电路的设计一般可按以下步骤进行(1)逻辑抽象:将文字描述的逻辑命题转换成真值表。

(2)选择器件类型:根据命题的要求和器件的功能决定采用哪种器件。

(3)根据真值表和所选用的逻辑器件写出相应的逻辑表达式:当采用SSI集成门电路设计时,为了使电路最简,应将逻辑表达式化简,并变换成与门电路相对应的最简式;当采用MSI组合逻辑器件设计时,则不用化简,只需将由最小项构成的函数式变换成MSI器件所需要的函数形式。

(4)根据化简或变换后的逻辑表达式及选用的逻辑器件画出逻辑电路图。

2. 常见的SSI和MSI的型号(1)常见的SSI:四2输入异或门74LS86,四2输入与非门74LS00,六非门74LS04,二4输入与非门74LS20,四2输入或非门74LS02,四2输入与门74LS08等。

(2)常见的MSI:二2-4译码器74LS139,3-8译码74LS138,4-16译码器74LS154,8-3线优先编码器74LS148,七段字符译码器74LS248,四位全加器74LS283,四2选1数据选择器74LS157,双4选1数据选择器74LS153,8选1数据选择器74LS151,16选1数据选择器74LS150等。

四、实验内容(一)基本命题1.设计一个多输出的逻辑网络,它的输入是8421BCD码,它的输出定义为:(1)F1:检测到输入数字能被3整除。

(2)F2:检测到输入数字大于或等于4。

(3)F3:检测到输入数字小于7。

实验三 msi(中规模集成组合电路)应用

实验三 msi(中规模集成组合电路)应用

MSI(中规模集成组合电路)是一种集成度比较高的组合逻辑电路,通常由10个至100

个门电路组成。

它的应用范围很广,可以用于数字电子电路、计算机系统、通信系统等领域。

以下是关于MSI应用的一些相关内容。

1.数字电子电路

在数字电子电路中,MSI常用于实现数字解码器、选通器、多路复用器等。

例如,

74LS138是一个常用的1到8解码器,它可以把三个输入线的8种组合映射为8个输出线中的一根高电平。

这种解码器广泛应用于存储器、显示器、地址选择器等领域。

另一个例子是74153,它是一个四路二选一多路复用器。

它有两个输入端口和一个选

通控制端口,可以选择其中的一个输入并输出到一个单一的输出端口。

这种多路复用器可

以用于选择不同的输入源,例如在音频处理器中选择不同的音频信号。

2.计算机系统

另一个例子是74LS192,它是一个4位二进制计数器。

它可以用于计算机定时器、频

率计、序列器等领域,提供逐位递增或递减计数。

它还通常用于构造存储器地址寄存器和

位移寄存器等电路。

3.通信系统

另一个例子是74LS652,它是一个8位输入/输出扫描转换器。

它可用于处理不同时序下的数据输入/输出,从而扩展计算机系统的输入/输出接口。

总之,MSI在数字系统的设计中应用广泛,几乎所有的数字系统中都会用到MSI器件。

MSI运算器以卓越的性能、可靠性和经济性,被广泛应用于各种数字逻辑系统的设计和制

造中。

随着科技的不断发展和进步,MSI的应用将更加广泛,也将有更多的MSI器件出

现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第1页,共 9 页

一、实验目的:

1. 熟悉编码器、译码器、数据选择器等组合逻辑功能模块的功能与使用方法。

2. 掌握用MSI设计的组合逻辑电路的方法。

二、实验仪器及器件:

1. 数字电路实验箱、数字万用表、示波器。

2. 器件:74LS00X1,74LS197X1,74LS138X1,74LS151X1

三、实验预习:

1. 复习常用组合逻辑电路工作原理和设计方法,及与之相应的MSI功能表及其使用方法。

2. 复习采用中规模集成电路实现组合逻辑电路的方法,如使用译码器和数据选择器实现组合逻辑电路。

四.实验原理:

中规模的器件,如译码器、数据选择器等,它们本身是为实现某种逻辑功能而设计的,但由于它们的一些

特点,我们也可以用它们来实现任意逻辑函数。

1. 用译码器实现组合逻辑电路……

2. 用数据选择器实现组合逻辑电路……

五、实验内容

1、用八选一数据选择器151设计一个函数发生器电路它的功能如表(四)所示。待静态测试检查电路工作正常

后,进行动态测试。将74LS197连接成十六进制作为电路的输入信号源,用示波器观察并记录CP.、S1、 S0、 A、 B、

Y的波形。

表(四)函数发生器功能表

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第2页,共 9 页

六:设计过程:

实验1:

列出Y的真值表:

根据真值表设计电路,数据选择器151的输出Y′的表达式:

7012601250124012

3012201210120

012

7

0DAAADAAADAAADAAADAAADAAADAAADAAADmYiii

S1=A2,S0=A1,A=A0;由真值表得:D0=D7=0,D1=D2=D4=B,D3=D6=1,D5=非B;

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第3页,共 9 页

逻辑图:

模拟波形图(从上往下依次是CP,B,A,S0,S1,Y):

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第4页,共 9 页

实际波形图:

cp与S1比较,得出二者的波形图

B与S1比较,得出B的波形图

A与S1进行比较,得出A的波形图

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第5页,共 9 页

S0与S1比较,得出S0的波形图

Y与S1比较,得出Y的波形图:

所有的波形图为:

验证得知:实际波形图与模拟波形图吻合!

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第6页,共 9 页

实验2:

数据分配器与数据选择器功能相反。它是将一路信号送到地址选择信号指定的输出。如输入为D,地址信号为

A、 B、C,可将D按地址分配到八路输出F0、F1、F2、F3、F4、F5、F6 、F7。其真值表如表(五)所示。试用3线.8

线译码器74LS138实现该电路。将74LS197连接成八进制作为电路的输入信号源,将QDQCQB分别与A.、B、C连接,

D接模拟开关,静态检测正确后,用示波器观察并记录D=1时,CP、 A、 B、C及F0-F7的波形。(提示:将74LS138

附加控制端S1作为数据输入端,同时令S2=S3l=0,A2A1A0作为地址输入端,即可将S1送来的数据只能通过A2A1A

0

所指定的一根输出线反相后送出去。)

表(五) 数据分配器真值表

A B C F0 F1 F2 F3 F4 F5 F6 F7

0 0 0 D 1 1 1 1 1 1 1

0 0 1 1 D 1 1 1 1 1 1

0 1 0 1 1 D 1 1 1 1 1

0 1 1 1 1 1 D 1 1 1 1

1 0 0 1 1 1 1 D 1 1 1

1 0 1 1 1 1 1 1 D 1 1

1 1 0 1 1 1 1 1 1 D 1

1 1 1 1 1 1 1 1 1 1 D

逻辑图:

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第7页,共 9 页

模拟波形图(从上倒下依次是:CP-C-B-A-F0~F7):

实际波形图:CP与A做比较,得出二者的波形

C与A做比较,得出C的波形

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第8页,共 9 页

B与A比较,得出B的波形

F0~F7 分别与 A 比较:

实验报告

SUN YAT-SEN UNIVERSITY

院(系) 软件学院 学 号 1 2 3 3 0 0 8 5班级 教 务 一 班

专 业 软件 工 程 实验人 付 洋

实验题目: 利用msi设计组合逻辑电路 2013年11月5日

第9页,共 9 页

分析得波形图:

实际波形图与模拟波形图一致!

心得体会:

在示波器上做对比时一定要选择一个周期最大,频率最小的波形作为所有波形的比较波形,这样可以根据这个最大

周期波形的一个周期画出其他的波形。