北京工业大学集成电路期末复习资料2

北工大半导体物理期末习题

半导体物理2009-2010 学年一、简答题1. Si和GaAs半导体晶体的解理面分别是什么?为何?一种半导体资料导带底Ec(k)附近和价带顶Ev(k)邻近表达式为,判断该半导体是直接带隙仍是间接带隙。

2. 什么是浅能级杂质?什么是深能级杂质?在半导体中各主要起什么作用?对于Si半导体资料各举出两种元素。

什么是本征半导体?什么是杂质半导体?表示画出N型样品电子浓度n随T变化曲线。

温度急剧高升后杂质半导体特征剖析变化。

跟着温度高升杂质半导体的导电模式发生改变,特征会像本征半导体,但不过是在导电方面像。

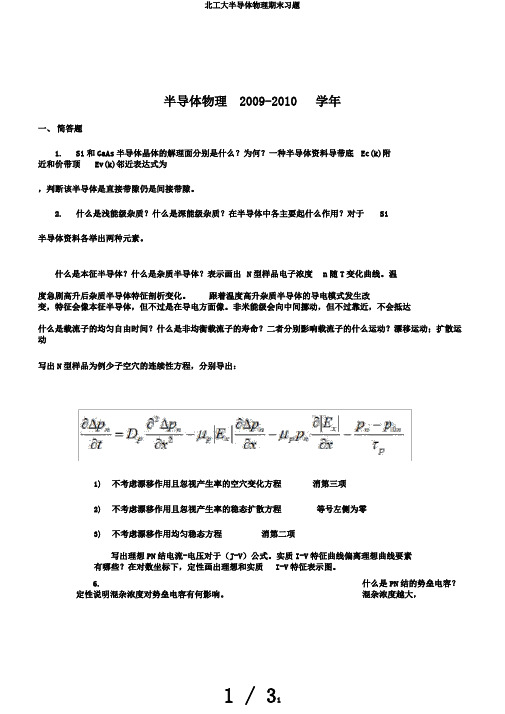

非米能级会向中间挪动,但不过靠近,不会抵达什么是载流子的均匀自由时间?什么是非均衡载流子的寿命?二者分别影响载流子的什么运动?漂移运动;扩散运动写出N型样品为例少子空穴的连续性方程,分别导出:1)不考虑漂移作用且忽视产生率的空穴变化方程消第三项2)不考虑漂移作用且忽视产生率的稳态扩散方程等号左侧为零3)不考虑漂移作用均匀稳态方程消第二项写出理想PN结电流-电压对于(J-V)公式。

实质I-V特征曲线偏离理想曲线要素有哪些?在对数坐标下,定性画出理想和实质I-V特征表示图。

6. 什么是PN结的势垒电容?定性说明混杂浓度对势垒电容有何影响。

混杂浓度越大,或许温度越高,势垒厚度就越小,则电容也就越大一个p-N异质结接触前能带图见图1。

画出均衡状态下能带图。

二、室温下,一个Si的N+P结,N区一侧混杂浓度为1017cm-3,P区为1015cm-3求该N+P结的接触电势差。

2)假如一个N+N结混杂浓度也分别为N+区一侧混杂浓度1017cm-3,N区为1015cm-3,求此时接触电势差。

三、一块N型半导体,组成理想的MOS构造1)当电压从正到负变化时,半导体一侧分别是什么状态?并画出电容C和电压V的C-V关系表示图。

怎样从该曲线得出氧化层的厚度和半导体一侧最大耗尽宽度?若氧化层中存在固定正电荷Qf,C-V曲线向哪边挪动?四、室温下,一块电阻率为Ω·cm的n型硅和一块电阻率为Ω·cm的p型硅。

芯片制造期末复习资料

芯片制造期末复习资料第一章(1)谁发明了集成电路? 德国青年工程师Jack Kilby(1959)(2)分立器件:每个芯片中只含有一个元件的器件。

分类:晶体管,二极管,电容器,电阻器等(3)集成电路:采用一定工艺,把一个电路中所需的晶体管,二极管,电阻,电容,电感等元件及布线连在一起的基片。

分类①功能结构:模拟集成电路数字集成电路数/模集成电路。

②按集成程度高低:小规模,中,大,超大,甚大。

③导电性:双极型,单极型。

(4)特征尺寸:特征尺寸即芯片表面电路和特征线宽。

特征尺寸越小,单位面积内的晶体管集成程度就越高,速度越快,性能越好,是衡量集成电路设计和制造水平的重要尺度。

第二章(1)半导体:常温下导电性介于导体和绝缘体之间的材料。

导体:容易导电的物体,即能够让电流通过的材料。

绝缘体:表现出核子对轨道电子的强大束缚,即对电子移动有很大阻碍的材料。

(2)常用半导体材料:锗,硅,硒。

(3)制造半导体过程中常用的化学品:酸,碱,溶剂,水第三章(1)晶体:原子在整个材料里重复排列成非常固定结构的材料。

非晶体:原子没有固定和周期性排列的材料。

(2)晶体生长的三种方法:直拉法,液体掩盖直拉法,区熔法。

第四章(1)晶圆生产工艺①薄膜工艺:是在晶圆表面形成薄膜的加工工艺。

薄膜可以是绝缘体,半导体,导体。

这些工艺技术是生长二氧化硅膜和沉淀不同材料薄膜。

通用的沉淀技术:物理气相沉积(PVD),化学气相沉积(CVD),蒸发和溅射。

②图形化工艺:通过一系列生产步骤将晶圆表面薄膜的特定部分除去的工艺,又可称为光掩膜,掩膜,光刻或微光刻。

是4个基本工艺中最关键的。

③掺杂:将特定量的杂质通过薄膜开口引入晶圆表层的工艺过程。

两种方法:热扩散和离子注入④热处理:简单地将晶圆加热和冷却来达到特定结果的过程。

第五章(1)洁净室的构成:①空调净化系统:空调机组空气过滤器系统②天花板系统③隔墙④地板:PVC地板,高架地板,防静电地板⑤照明系统。

电子技术基础期末复习资料(含答案)

11级电子技术基础期末复习资料一.概念填空:1.电路由电源负载中间环节三部分组成。

2.电路中电流数值的正或负与参考方向有关,参考方向设的不同,计算结果也不同。

3.理想电压源的端电压与流过它s的电流的方向和大小无关,流过它的电流由端电压与外电路所共同决定。

4.由电路中某点“走”至另一点,沿途各元件上电压代数和就是这两点之间的电压。

5.相互等效的两部分电路具有相同的伏安特性。

6.电阻并联分流与分流电阻值成反比,即电阻值大者分得的电流小,且消耗的功率也小。

7.串联电阻具有分压作用,大电阻分得的电压大,小电阻分得的电压小功率也小。

8.实际电压源与实际电流源的相互等效是对外电路而言。

9.在电路分析中,应用戴维南或诺顿定理求解,其等效是对外电路而言。

11 .常用的线性元件有电阻、电容、电感,常用的非线性元件有二极管和三极管。

12.二极管正向偏置,是指外接电源正极接二极管的阳(或正)极,外接电源负极接二极管的阴(或负)极。

13.P型半导体是在本征半导体中掺杂 3 价元素,其多数载流子是空穴,少数载流子是自由电子。

40. N型半导体是在本征半导体中掺杂 5 价元素,其多数载流子是自由电子,少数载流子是空穴。

14.若三极管工作在放大区,其发射结必须正偏、集电结必须反偏;三极管最重要的特性是具有电流放大作用。

15.根据换路定则,如果电路在t=0时刻发生换路,则电容的电压u c(0+)= uc(0-) ,电感电流i l (0+)= i l (0-) 。

16.三极管工作时,有三种可能的工作状态,它们分别是__放大状态_、___饱和状态、___截止状态_____。

38.3个输入的译码器,最多可译出__8____(2×2×2)____ 路的输出。

17.4个输入的译码器,最多可译出__16___(2×2×2×2)______ 路的输出。

18.根据逻辑功能的不同,可将数字电路分为___组合______逻辑电路和时序________逻辑电路两大类。

北京工业大学 电分复习2015

《电路分析基础》转专业试卷姓名___________ 学号___________ 日期2011、9(请考生注意:本试卷共 8 页)一、是非题(每题1分,共10分)1.单调型非线性电阻,随着电压升高,动态电阻也增加。

2.如二端网络的伏安特性为U= -20+5I,则图示支路与之等效。

3.工作在匹配状态下的负载可获得最大功率,显然这时电路的效率最高。

4.电压源与电阻串联电路短路时电流为2A,功率损耗为400W。

则此电路的最大输出功率为400W。

5.RLC串联电路接通直流电压源瞬间,除u C和i L之外,其余元件的电压或电流均能跃变。

6.线性动态电路微分方程的阶次与电路中的储能元件数恒等。

7.图示耦合电感电路中,互感电压u M为参考方向,当开关S断开瞬间,u M的真实方向与参考方向相反。

8.右上图示RLC串联电路,未并联C2时,谐振角频率与品质因数分别为ω0与Q,后,谐振角频率与品质因数为ω0'与Q',则ω0>ω0',Q >Q'。

并联C29.图示电路中,如,则有10.理想变压器初、次级的变比为5:1,已知次级所接电阻为3Ω,此时初级的输入电阻为75Ω。

二、单项选择题(每题2分,共20分)1.图示电路中的电流I为(A)7.5A (B)5A (C)0 (D)3A2.图示为电路的一部分,已知U ab=60V,则受控源发出的功率为(A)40W (B)60W (C)-40W (D)-160W3.关于一阶动态电路的零状态响应,以下概念中错误的是(A)零状态响应的绝对值均为逐渐增长(B)零状态响应就是零初始状态响应(C)零状态响应中电路的电磁储能逐渐增长(D)零状态响应一般认为在历时5 后已基本进入稳态4.图示电路中,4A为直流电流源,该电路处于稳态时储存有能量的元件是(A)电容C (B)电感L (C)电容C和电感L (D)电阻R15. RLC串联谐振电路,当只改变R时,则R越大(A)电路的选择性越差 (B)电路的选择性越好(C)电路的选择性不受R的影响6.常用电容器的两项主要数据是电容量和耐压值。

东南大学 专用集成电路(专集) 期末考试复习习题集

294

NMOS管和 PMOS管的等效电阻近似为: 2VDD 2VDD Rn 50 25 K, R p K 2 n (VDD Vtn ) p (VDD Vtp ) 2 计算的时延均由最坏情 况确定: 与非门: Rdown 2 Rn 50 K,Rup R p / 2 25 K t f Rdown C L 50 K 13.5 fF 0.675ns t r Rup C L 25 K 13.5 fF 0.3375ns t av tr t f 4 0.253ns

2 Wn pF m 3m 4 8 n Cox n 9.85 10 ( 2 ) 500 10 m Ln V s 1m

0 ox

1.47 10 pF / V s

8

286

(2)

Wn n n p p Lp Ln let

Wp

(3)

295

或非门: Rdown Rn / 2 12.5 K , Rup 2 R p 100 K t f Rdown C L 12.5 K 13.5 fF 0.17 ns t r Rup C L 100 K 13.5 fF 1.35ns,t av 反相器: Rdown Rn 25 K , Rup R p 50 K t f Rdown C L 25 K 13.5 fF 0.3375ns t r Rup C L 50 K 13.5 fF 0.675.35ns,t av tr t f 4 0.253ns

292

上拉电阻为: Rup R p / 2

Lp

或非门: 最坏情况下 : 下拉电阻为: Rdown Rn / 2, 上拉电阻为: Rup 2 R p 要求具有对称的驱动能 力,有 Rdown Rup, Rn / 2 2 R p, R p Rn / 4, 1 Ln ,取 L p Ln L , 则 Wp 8Wn pW p 4 nWn S nor 2 S n 2 S p 2 L (Wn W p ) 2 L (Wn 8Wn ) 18 LW n 令 Wn Wmin , 则 S nor 18 LW min S nor 18 LW min 3 6 LW min S nand

北京工业大学自动控制原理期末复习共49页PPT

46、法律有权打破平静。——马·格林 47、在一千磅法律里,没有一盎司仁 爱。以惩罚相补偿;只有处 罚才能 使犯罪 得到偿 还。— —达雷 尔

50、弱者比强者更能得到法律的保护 。—— 威·厄尔

谢谢

11、越是没有本领的就越加自命不凡。——邓拓 12、越是无能的人,越喜欢挑剔别人的错儿。——爱尔兰 13、知人者智,自知者明。胜人者有力,自胜者强。——老子 14、意志坚强的人能把世界放在手中像泥块一样任意揉捏。——歌德 15、最具挑战性的挑战莫过于提升自我。——迈克尔·F·斯特利

集成电路设计(王志功)第三版第二章复习材料

集成电路设计(王志功)第三版第二章复习材料1、电子系统特别是微电子系统应用的材料有哪几类?三类:导体,半导体,绝缘体。

2、集成电路制造常用的半导体材料有哪些?硅,锗,砷化镓,磷化铟等。

3、为什么说半导体材料在集成电路制造中起着根本性的作用?首先,集成电路通常是制作在半导体衬底材料之上的;同时,集成电路中的基本元件是根据半导体的特性构成的。

4、半导体材料得到广泛应用的原因是什么?①通过掺入杂质可以明显改变半导体的电导率;②当半导体受到外界热的刺激时,其导电能力将发生显著变化(热敏效应);③光照也可改变半导体的电导率(光敏效应);④多种由半导体构成的结构中,当注入电流时会发射出光。

5、Si、GaAs、InP三种基本半导体材料中,电子迁移率最高的是哪种?最低的是哪种?最高:GaAs 最低:Si6、在过去40年中,基于硅材料的多种成熟工艺技术有哪些?双极型晶体管(BJT)结型场效应管(J-FET)P型场效应管(PMOS)N型场效应管(NMOS)互补型金属-氧化物-半导体场效应管(CMOS)双极型管CMOS(BiCMOS)等。

7、硅基最先进的工艺线晶圆直径已达到多少?0.13umCMOS工艺制成的CPU运行速度已达多少?300mm(12英寸);超过2GHz。

8、为什么市场上90%的IC产品都是基于Si工艺的?因为原材料来源丰富,技术成熟,硅基产品保持价格低廉。

9、与Si材料相比,GaAs具有哪些优点?①砷化镓中非平衡少子饱和漂移速率为4×1072cm/(V.s),大约是硅9×1062cm/(V.s)的4倍,因此可制成更快的器件和IC;②砷化镓导带极小值和价带最大值都出现在布里渊区波矢为0处,而硅的导带最小值在X点,所以在砷化镓中,电子和空穴可直接复合,而硅则不行;③砷化镓中价带与导带之间的禁带为1.43eV,大于硅的1.11eV。

所以稳态时,在300K室温下,砷化镓本征激发中载流子密度(106cm3-)远小于硅(1010cm3-)。

北工大单片机期末复习题

第10章串行接口技术1. 8051有一个全双工的串行口,下列功能中该串行口不能完成的是( D )。

(A)网络通信;(B)异步串行通信;(C)作为同步移位寄存器;(D)位地址寄存器。

2.判断下列说法是否正确:答:(A)串行口通讯的第9数据位的功能可由用户定义。

(对)(B)发送数据的第9数据位的内容在SCON寄存器的TB8位中预先准备好的。

(对)(C)串行通讯帧发送时,指令把TB8位的状态送入发送SBUF中。

(错)(D)串行通讯接收到的第9位数据送SCON寄存器的RB8中保存。

(对)(E)串行口方式1的波特率是可变的,通过定时器/计数器T1的溢出率设定。

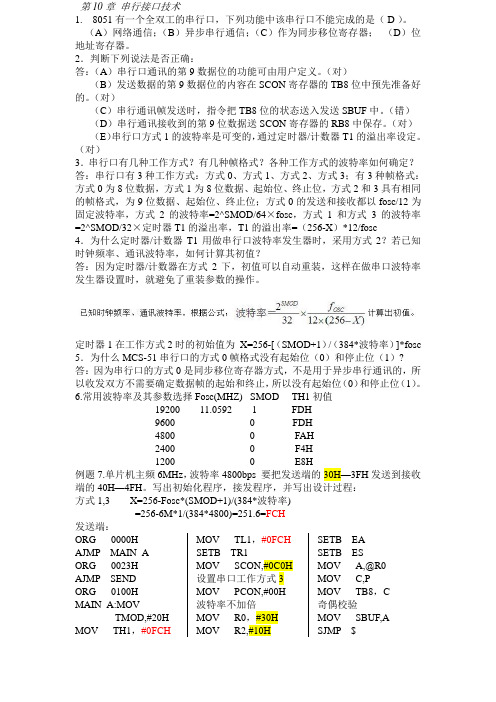

(对)3.串行口有几种工作方式?有几种帧格式?各种工作方式的波特率如何确定?答:串行口有3种工作方式:方式0、方式1、方式2、方式3;有3种帧格式:方式0为8位数据,方式1为8位数据、起始位、终止位,方式2和3具有相同的帧格式,为9位数据、起始位、终止位;方式0的发送和接收都以fosc/12为固定波特率,方式2的波特率=2^SMOD/64×fosc,方式1和方式3的波特率=2^SMOD/32×定时器T1的溢出率,T1的溢出率=(256-X)*12/fosc4.为什么定时器/计数器T1用做串行口波特率发生器时,采用方式2?若已知时钟频率、通讯波特率,如何计算其初值?答:因为定时器/计数器在方式2下,初值可以自动重装,这样在做串口波特率发生器设置时,就避免了重装参数的操作。

定时器1在工作方式2时的初始值为X=256-[(SMOD+1)/(384*波特率)]*fosc 5.为什么MCS-51串行口的方式0帧格式没有起始位(0)和停止位(1)? 答:因为串行口的方式0是同步移位寄存器方式,不是用于异步串行通讯的,所以收发双方不需要确定数据帧的起始和终止,所以没有起始位(0)和停止位(1)。

6.常用波特率及其参数选择 Fosc(MHZ) SMOD TH1初值19200 11.0592 1 FDH9600 0 FDH4800 0 FAH2400 0 F4H1200 0 E8H例题7.单片机主频6MHz,波特率4800bps 要把发送端的30H—3FH发送到接收端的40H—4FH。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章:填空:1.等比例缩小理论包括恒定电场(CE)等比例缩小定律、恒定电压(CV)等比例缩小定律、准恒定电场(QCE)等比例缩小定律。

名词解释:1.摩尔定律:Intel公司创始人之一Moore预测集成电路的集成度大约是每18个月翻一番,称为摩尔定律。

2.CMOS集成电路要把NMOS和PMOS两种器件做在一个芯片里。

3.CMOS集成电路是利用NMOS 和PMOS的互补性来改善电路性能的,因此叫做CMOS集成电路。

在P型衬底上用N阱工艺制作CMOS集成电路。

第二章:填空:集成电路加工的三个基本操作为:1形成某种材料的薄膜,2在各种材料的薄膜上形成需要的图形,3通过掺杂改变材料的电阻率或杂质类型。

名词解释:闩锁效应:在n阱CMOS中PMOS管的源、漏区通过n阱到衬底形成了寄生的纵向PNP晶体管,而NMOS的源、漏区与P型衬底和n阱形成寄生的横向NPN晶体管。

PNP晶体管的集电极和NPN晶体管的基极通过衬底连接,同时NPN晶体管的集电极通过阱和PNP晶体管的基极相连,从而构成交叉耦合形成的正反馈回路,一旦其中有一个晶体管导通,电流将在两支晶体管之间循环放大,使电流不断加大,最终导致电源和地之间形成极大的电流,并使电源和地之间锁定在一个很低的电压,这就是闩锁效应CMOS版图设计规则:为了保证制作的集成电路合格并保证一定的成品率,不仅要严格控制各种工艺参数,而且要有设计正确合理的版图,在设计版图时必须严格遵守的某些限制称为版图设计规则。

浅沟槽隔离工艺:浅沟槽隔离是采用现代刻蚀技术实现很大的纵横比沟槽,然后采用CVD 方法淀积SiO2从而形成用于隔离的沟槽。

所示为MOS晶体管结构图,请写出图中字母A至F所对应部位的中文名称,并以NMOS 为例简述MOS晶体管的工作原理。

(5分)图 11. 请画出电路图并解释N 阱CMOS 结构中的闩锁效应。

(6分)由于N 阱CMO S 结构中的横向寄生NPN 晶体管和纵向寄生PNP 晶体管形成正反馈电路结构,在特定的外部条件下,将发生N 阱CMOS 电路电源和地线之间的低电阻状态,即发生闩锁效应。

填空题作为集成电路制作的基本工艺流程之一,掺杂方法主要有高温扩散和离子注入。

2. 淀积的作用是把另一种物质淀积在硅片表面,目前普遍采用的是化学气相淀积方法。

3. 对于硅栅工艺是先做栅极,再做源、漏区掺杂,实现源-栅-漏自动对准,故硅栅工艺又叫做自对准工艺。

4. 集成电路的互连线存在寄生效应,这些效应包括寄生电容,寄生电阻,寄生电感。

5. 目前先进的CMOS 工艺是采用沟槽隔离的外延双阱技术,这种技术可以有效的防止体硅CMOS 出现闩锁效应效应。

1. 试说明MOS 晶体管的阈值电压有哪些部分组成?2. 什么是MOS 晶体管的本征阈值?3. 试说明体效应如何影响阈值电压?4. MOS 晶体管的三个工作区是什么?5. 区分MOS 晶体管工作在线性区和饱和区的条件是什么?6. 什么是MOS 晶体管的导电因子?7. 试说明MOS 晶体管的亚阈值电流。

8. 什么是MOS 晶体管的瞬态响应?9.试解释短沟道效应。

A :源极,B :栅极,C :漏极,D :源区,E :漏区,F :p 型硅衬底。

N 沟MOS 晶体管工作原理:V GS 增加时,吸引到P 衬底表面层的电子就增多,当V GS 达到某一数值时,这些电子在栅极附近的P 衬底表面便形成一个N 型薄层,且与两个N +区相连通,在漏——源极间形成N 型导电沟道,其导电类型与P 衬底相反,称为反型层。

V GS 越大,作用于半导体表面的电场就越强,吸引到P 衬底表面的电子就越多,导电沟道越厚,沟道电阻越小。

10.试解释饱和区沟道调制效应。

kjl11.什么是迁移率退化和速度饱和?12.什么是热电子效应?13.试说明SPICE中MOS晶体管的各级模型Level=1、Level=2、Level=3、Level=4的特点。

14.试说明薄层电阻或方块电阻的含义。

15.什么是互连线的RC延迟?第四章一、填空题3. CMOS逻辑电路的功耗由三部分组成:动态功耗P d、开关过程中的短路功耗P SC、静态功耗P s。

4. 用CMOS电路设计静态数字逻辑电路,如果设计与非逻辑下拉支路应该是串联,如果设计或非逻辑下拉支路应该是并联。

5. CMOS数字集成电路中,对于NMOS下拉网络的构成规律是:NMOS管串联实现与操作;NMOS管并联实现或操作。

对于PMOS上拉网络则是按对偶原则构成,即PMOS管串联实现或操作;PMOS管并联实现与操作。

*6.富NMOS动态电路与富NMOS动态电路不能直接级联,但可以与富PMOS动态电路直接级联。

填空:1. 电路的最高工作频率是指因此最高工作频率的公式为2. 上升时间的定义下降时间的定义3. 噪声容限的三个定义:4. 画图说明导电因子和阈值电压对反向器电压传输特性的影响5. 什么叫无比电路什么叫有比电路(用CMOS,E/E, E/D,E/R,反向器讨论)6. 反向器的延时时间是如何定义的有何作用7.画图解释NMOS传输们传高电平和低电平的过程8. 画图解释PMOS传输们传高电平和低电平的过程9. 画图解释CMOS传输们传高电平和低电平的过程10. 如何得到传输门的导通电阻11. 衬偏效应对CMOS传输门性能的影响二、名词解释*1. 传输门阵列逻辑:答:用传输门串并联可以构成一个比较规则的电路形式,这种电路形式可以叫做传输门阵列。

*2. 多米诺(Domino)CMOS电路:答:多米诺(Domino)CMOS电路由一级预充-求值的动态逻辑门加一级静态CMOS反相器构成。

3.可恢复逻辑电路:答:当输入逻辑电平偏离理想电平时,能使偏离理想电平的信号经过几级电路逐渐收敛到理想工作点,最终达到合格的逻辑电平的电路。

4. CMOS 反相器的输出上升时间答:对CMOS 反相器V L =V DD ,上升时间是输出从0.1V DD 上升到0.9V DD 所需要的时间。

5. CMOS 反相器的输出下降时间答:对CMOS 反相器V L =V DD ,下降时间是输出从0.9V DD 下降到0.1V DD 所需要的时间。

简答题1. 描述如何得到一个反向器的稳态工作点2. 0.18um 工艺下 Kn=3Kp, 设计一个反向器,说明器件尺寸3. 画出CMOS 反向器的电路图,版图,电压传输特性曲线,并指出NMOS,PMOS 工作区4. 讨论CMOS 反向器直流设计和瞬态设计的矛盾,并举例说明如何折衷。

三、画图题根据管级电路图写出逻辑表达式 1.C i V P 0P 1P 2P 3四:根据逻辑表达式补齐版图,根据版图写出管级电路图 1. 逻辑为C AB Y +=,在版图上? ● 标出输入信号 ● 补齐版图● 再画出管级原理图多晶硅铝线n+p+n阱接触孔2.逻辑为BABAY+=,在版图上补齐版图?多晶硅金属1n+p+n阱接触孔A B金属2通孔3.画出如下棍图的管级原理图AY金属BCGNDVDD多晶硅n+p+接触孔根据逻辑表达式画出管级电路图和棍图 1.|)(C B A Y += 2.D C B A Y +=3.D ABC Y +=1. 请画出用CMOS 电路实现Y=A(B+C)DE +逻辑功能的电路图。

(6分)2. 请画出用CMOS 电路实现DE BC A Y ++=逻辑功能的晶体管级电路图。

(5分) 图例:3. 请画出CMOS 反相器的直流电压传输特性曲线,标出5个工作区域,并写出两管在相应区域的工作状态。

(5分)4. 请绘出NMOS I-V 特性曲线,说明其工作状态及不同状态的界线。

(5分)5.请画出用CMOS 电路实现DE C AB Y ++=逻辑功能的晶体管级电路图。

(5分) 图例:1:0≤V in ≤V outNMOS 截止,PMOS 线性。

输出高电平区 2:V TN <V in <V out +V TPNMOS 饱和,PMOS 线性。

转变区 3:V out +V TP ≤V in ≤V out + V TNNMOS 饱和,PMOS 饱和。

转变区 4:V out + V TN <V in < V DD +V TPNMOS 线性,PMOS 饱和。

转变区 5:V DD ≥V in ≥V DD +V TPNMOS 线性,PMOS 截止。

输出低电平区 V DS <(VGS-Vt ) 线性区V DS >(VGS-Vt ) 饱和区 V GS <V T 截止区1.写出对称设计的CMOS反相器逻辑阈值电平和由其定义的最大噪声容限?2.为什么CMOS反相器是可恢复逻辑电路?什么是动态CMOS电路的预充-求值?3.什么是多米诺CMOS电路?4.什么是动态CMOS电路的电荷分享6. 已知某CMOS反相器的输出上升时间和下降时间分别为15ns和25ns,试确定该反相器工作频率的上限。

(5分)解:f m=1/(2max(t r,t f))=1/(2×25ns)=1/50ns=2×10^7s答:该反相器工作频率的上限是2×10^7s7. 请画出CMOS反相器的电路图和版图(5分)图例:*8.请画出一个静态CMOS二输入或非门的晶体管级电路图及其版图(5分)图例:四、电路分析题2. 假设有两个逻辑信号A 、B ,其中A 先于B 到达如图所示电路;为了使电路得到最好的瞬态特性,请在图中标注出A 、B 接入方法,并解释为什么。

五、综合题1. *请画出实现二输入与非逻辑功能Y A B =⋅的富NMOS (仅用NMOS 晶体管实现逻辑求值功能,而用PMOS 晶体管实现高电平预充功能)预充-求值动态逻辑电路图。

简要说明电路中的电荷分享问题是如何形成的。

(10分) 预充:Φ =“0”,M P 导通对C L 充电,输出V O =V DD求值:Φ =“1”,OL O V V ===”,则“若1B A ; DD O V V ===”,则“”“若0B 1A ,但此时, C L 对C 1进行电荷分享会出现输出高电平下降。

AB答:将先到达的逻辑信号A 接于靠近地线的NMOS 管M N1的栅极上,将有利于使先到达的信号A 对串联支路的中间结点寄生电容放电,其原因是只有中间结点的电容放电后,才能使输出结点寄生电容放电,这样有利于提高电路的响应速度。

第五章填空:1.CMOS逻辑门的特点(带非逻辑,NMOS串与或并,n个输入需要2n个MOS管,无比电路)2.电路的总延迟时间与(每个逻辑门的具体结构和器件参数)有密切关系3.减少每个逻辑门的输入端数有利于(减小面积和改善速度)4.在CVSL电路中交叉耦合的PMOS负载管有(锁存)作用,使输出状态不易(翻转)5.CPL最有吸引力的优点是(简单而规则的电路形式)6.DPL比较适合于在(低电源电压的VLSI)中采用简答题1.如何设计CMOS与非门或非门 106页2.用静态CMOS和类NMOS逻辑门实现Y=AB+CD的非图5.5.13.类NMOS电路的特点 118页4.用传输门阵列实现4选一多路器图5.7.2第六章简答题:1、请举例加以说明预充-求值动态电路的级联问题及电荷分享问题;答案:见书P142-1442、请画出准静态D触发器的电路图,并说出D触发器和D锁存器的区别;答案:准静态D触发器的电路图见书P163 图6.6.9,D触发器和D锁存器的区别:P165 触发器只在时钟的上升边或下降边翻转,无论输入信号如何变化,在一个时钟周期内输出状态只能变化一次,因此没有空翻的问题。