数字电子技术(山东联盟-临沂大学)智慧树知到答案章节测试2023年

模拟电子技术基础(山东联盟)智慧树知到答案章节测试2023年青岛科技大学

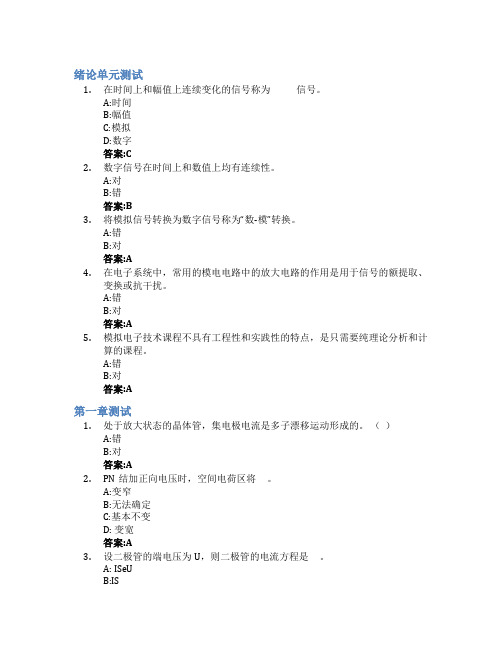

绪论单元测试1.在时间上和幅值上连续变化的信号称为信号。

A:时间B:幅值C:模拟D:数字答案:C2.数字信号在时间上和数值上均有连续性。

A:对B:错答案:B3.将模拟信号转换为数字信号称为“数-模”转换。

A:错B:对答案:A4.在电子系统中,常用的模电电路中的放大电路的作用是用于信号的额提取、变换或抗干扰。

A:错B:对答案:A5.模拟电子技术课程不具有工程性和实践性的特点,是只需要纯理论分析和计算的课程。

A:错B:对答案:A第一章测试1.处于放大状态的晶体管,集电极电流是多子漂移运动形成的。

()A:错B:对答案:A2.PN结加正向电压时,空间电荷区将。

A:变窄B:无法确定C:基本不变D: 变宽答案:A3.设二极管的端电压为U,则二极管的电流方程是。

A: ISeUB:ISC:ISeU/UT -1D: ISeU/UT答案:C4.因为N型半导体的多子是自由电子,所以它带负电。

()A:对B:错答案:B5.PN结又被称为空间电荷区,耗尽层。

A:错B:对答案:B第二章测试1.射极输出器是()组态的放大电路。

A:共源B:共基C:共集D:共射答案:C2.放大电路中的上限截止频率fH和下限截止频率fL决定于电容所在回路的时间常数τ,通频带等于()A:fH-fLB:fLC:fHD:fL-fH答案:A3.以下基本单管放大电路中,电压放大倍数小于1的是()A:共集电路B:共基电路C:共漏电路D:共射电路E:共源电路答案:A4.NPN型单管共射放大电路顶部出现了削波失真,该类型的失真称为()。

A:交越失真B:饱和失真C:截止失真答案:C5.一个NPN型晶体三极管构成的单管基本放大电路,输入信号从基极输入,信号从发射极输出,则可以判断该电路的接法是()A:共源B:共基C:共射D:共集答案:D6.以下几种接法的电路中,不具有电压放大作用的是()。

A:共基放大电路B:共集放大电路C:共源放大电路D:共射放大电路答案:B第三章测试1.用恒流源取代长尾式差分放大电路中的发射极电阻Re,将使电路的________。

EDA技术(山东联盟)智慧树知到答案章节测试2023年泰山学院

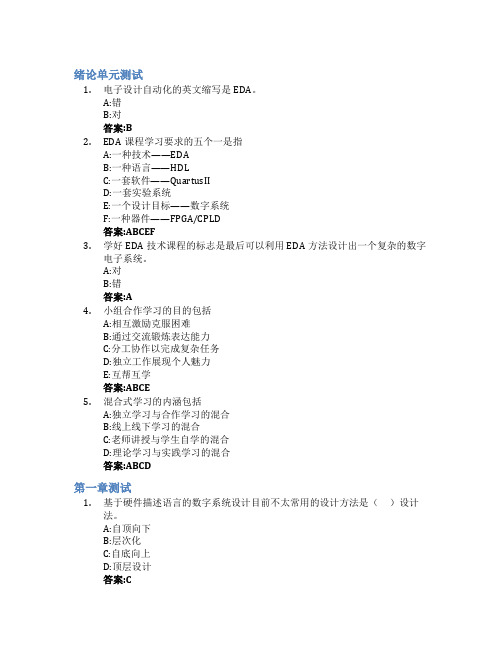

绪论单元测试1.电子设计自动化的英文缩写是EDA。

A:错B:对答案:B2.EDA课程学习要求的五个一是指A:一种技术——EDAB:一种语言——HDLC:一套软件——QuartusIID:一套实验系统E:一个设计目标——数字系统F:一种器件——FPGA/CPLD答案:ABCEF3.学好EDA技术课程的标志是最后可以利用EDA方法设计出一个复杂的数字电子系统。

A:对B:错答案:A4.小组合作学习的目的包括A:相互激励克服困难B:通过交流锻炼表达能力C:分工协作以完成复杂任务D:独立工作展现个人魅力E:互帮互学答案:ABCE5.混合式学习的内涵包括A:独立学习与合作学习的混合B:线上线下学习的混合C:老师讲授与学生自学的混合D:理论学习与实践学习的混合答案:ABCD第一章测试1.基于硬件描述语言的数字系统设计目前不太常用的设计方法是()设计法。

A:自顶向下B:层次化C:自底向上D:顶层设计答案:C2.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

下面关于综合的描述错误的是A:综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;B:为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;C:综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是不唯一的。

D:综合是纯软件的转换过程,与器件硬件结构无关。

答案:D3.所列哪个流程是基于EDA软件的正确的FPGA / CPLD设计流程A:原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试B:原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试C:原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试D:原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试答案:C4.IP核在EDA技术和开发中具有十分重要的地位,以版图文件方式提供的IP被称为()。

智慧树知道网课《数字电子技术(山东联盟—中国石油大学(华东))》课后章节测试满分答案1

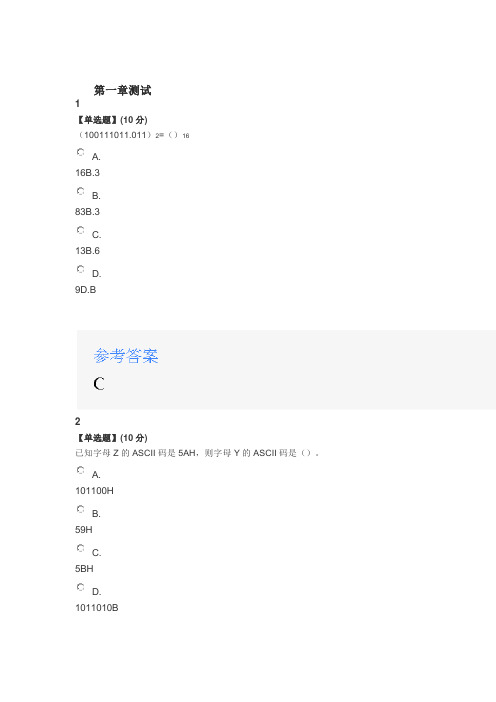

第一章测试1【单选题】(10分)(100111011.011)2=()16A.16B.3B.83B.3C.13B.6D.9D.B2【单选题】(10分)已知字母Z的ASCII码是5AH,则字母Y的ASCII码是()。

A.101100HB.59HC.5BHD.1011010B3【单选题】(10分)二进制数110000转换为十六进制数等于()。

A.30B.77C.D7D.74【单选题】(10分)二进制数1010.101对应的十进制数是()。

A.16.75B.10.625C.12.75D.11.335【单选题】(10分)十六进制数1A2对应的十进制数是()。

A.578B.308C.208D.4186【单选题】(10分)有一个数是123,它与十六进制数53相等,则该数是()进制。

A.2B.8C.5D.107【单选题】(10分)下列4个无符号十进制整数中,能用8个二进制位表示的是()。

A.296B.313C.257D.2018【多选题】(10分)(2004)10+(32)16的结果是()。

A.(806)16B.(4006)8C.(111000000110)2D.(2054)109【判断题】(10分)十进制25对应的8421BCD码为(100101)8421BCD。

A.错B.对10【单选题】(10分)(01110010)格雷码=()余3BCDA.01010011B.10000110C.01000010D.01100100第二章测试1【判断题】(10分)在逻辑运算中,如果F+G=1,则F=1-G。

A.错B.对2【单选题】(10分)A,B,C是输入变量,Y是输出变量,请写出Y的最简或与表达式。

A.Y=A'BC+ABC'+AB'CB.Y=A'B'+A'C'+B'C'+ABCC.Y=(A+B'+C')(A'+B'+C)(A'+B+C')D.Y=(A+B)(A+C)(B+C)(A'+B'+C')3【多选题】(10分)假设一个逻辑函数的卡诺图如下图所示,请写出其对应的约束条件。

模拟电子技术实验——轻松开启模拟电子技术之门(山东联盟)智慧树知到答案章节测试2023年青岛大学

第一章测试1.信号的三要素是幅值、周期和初相位。

A:对B:错答案:A2.以下仪器设备中,可用于提供输入信号的是A:示波器B:函数信号发生器C:DC信号源D:交流毫伏表答案:BC3.总体来说,函数信号发生器的功能有A:频率设置B:幅值设置C:波形设置D:自检设置答案:ABC4.以下是交流有效值的单位是A:VrmsB:VppC:mVppD:dBm答案:A5.通常,示波器在使用前都需要进行自检。

示波器GDS820C的自检信号波形是A:1kHz1Vpp的方波信号B:1kHz2Vpp的正弦波信号C:1kHz2Vpp的方波信号D:1kHz1Vpp的正弦波信号答案:C6.调整示波器垂直系统的POSITION旋钮时,改变的是坐标轴横轴的位置,观测的信号也会随之变化。

A:对B:错答案:B7.若要使示波器观测的波形在垂直方向上压缩显示,则需要将VOLTS/DIVA:左旋至底B:右旋至底C:调大D:调小答案:C8.调整示波器水平系统的POSITION旋钮时,可以A:改变坐标轴纵轴的位置B:改变坐标轴横轴的位置C:改变水平方向每格所代表的时间D:改变波形的完整性答案:B9.若要使示波器观测的波形稳定显示,触发电平A:位于最大值上面位于最小值下面B:位于最大值上面C:位于最大值和最小值之间答案:C10.通常,示波器屏幕上显示波形周期数A:5个B:2-3个C:1个D:越多越好答案:B11.直流稳压电源GPS-3303A的CH3为5V3A的固定输出端。

A:错B:对答案:B第二章测试1.信号放大的前提是不失真,不失真的放大,在实验中是通过调试合适的静态工作点来保证的。

A:对B:错答案:A2.基本放大电路实验中给放大电路提供输入信号的设备是A:交流毫伏表B:直流稳压电源C:DC信号源D:函数信号发生器答案:D3.在测量放大电路的输入电阻时,需要在信号源和放大电路之间串联一个电阻Rs,其数量级应与放大电路的输入电阻在同一个数量级上。

数字电子技术智慧树知到答案章节测试2023年中国农业大学

绪论单元测试1.保密性好是数字电子技术的特点A:对B:错答案:A2.数电的抗干扰能力弱A:错B:对答案:A第一章测试1.一位十六进制数的最大数是几?A:15B:2C:9D:7答案:A2.一位二进制有几个数?A:0B:2C:16D:1答案:B3.一位二进制有几个数?A:1B:4C:8D:2答案:B4.8位二进制,一共可以表示多少个数?A:64B:256C:8D:16答案:B5.以下各个物理量是数字信号的是:A:用0和1 表示的高低电平B:电压C:电阻阻值D:电流答案:A6.某班共有30位同学,现在要给每位同学分配一组二进制代码。

请问最少需要多少位的二进制代码?A:10B:3C:16D:5答案:D7.学生的学号是码制,代表不同的学生。

A:错B:对答案:B8.余3 码是一种BCD码A:对B:错答案:A9.二进制数运算中,补码的作用是将减法运算变为加法运算。

A:对B:错答案:A10.ASCII码是一组7位二进制代码,用来表示数字、字母、各种符号和控制码等。

A:对B:错答案:A第二章测试1.逻辑代数中一共有多少种逻辑运算?A:8B:3C:5D:6答案:A2.逻辑函数的常用表示方法有A:逻辑电路图B:卡诺图C:真值表D:逻辑表达式答案:ABCD3.逻辑函数的最小项之和形式是什么样的表达式?A:与或非表达式B:与非-与非表达式C:与或表达式D: 或与表达式答案:C4.卡诺图主要用于化简多少个变量的逻辑表达式?A:3变量或4变量B:大于5变量C:5变量D:2变量答案:A5.与或表达式的最简标准是:A:项数最少,且每项中的因字数最少B:项数最少C:每项中的因字数最少D:逻辑运算种类最少答案:A6.任何一个逻辑函数都可以化成最小项之和的形式。

A:对B:错答案:A7.用卡诺图化简逻辑函数,可以一步得出最简结果。

A:错B:对答案:B8.化简多输出逻辑函数时,寻找并合理地利用共用项,有时可以得到更简单的化简结果。

A:对B:错答案:A9.逻辑函数中的无关项是指:在实际中不可能出现的项,或者无论取0还是取1对逻辑函数值没有影响的项。

Digital Logic Circuits 数字逻辑电路智慧树知到课后章节答案2023年

Digital Logic Circuits 数字逻辑电路智慧树知到课后章节答案2023年下南京理工大学南京理工大学第一章测试1.The number of values that can be assigned to a bit are ( )答案:twopared to analog systems, digital systems ( )答案:are less prone to noise3.The term bit means ( )答案:both answers (b) and (c)4. A quantity has continuous value is ( )答案:an analog quantity5.Verilog HDL is a ( )答案:computer language6. A category of digital integrated circuits having functions that can be altered isknown as fixed-function logic.答案:错7.Data are information only in numeric.答案:错8.Two broad types of digital integrated circuits are fixed-function andprogrammble.答案:对9.The nonrecurring engineering (NRE) cost for an ASIC design is normally low.答案:错10.There is an “invalid” region between the input ranges for logic 0 and logic 1答案:对第二章测试1.For the binary number 10000, the weight of the column with the 1 is ( )答案:162.The 2’s complement of 1000 is ( )答案:10003.The fractional binary number 0.11 has a decimal value of ( )答案:¾4.The number 1100 in BCD is ( )答案:invalid5.An example of an unweighted code is ( )答案:Gray code6.An example of an alphanumeric code is ( )答案:ASCII7.The overflow occurs when adding the following 8-bit two’s complementnumber:01011101+00110001答案:对8.The overflow does NOT occur when adding the following 8-bit two’scomplement number:10111111+11011111答案:对9.In general, we need at most bits to express the product when multiplying ann-bit number by an m-bit number.答案:错10.An addition overflows if the addends’ signs are the same but the sum’s sign isdifferent from the addends’.答案:对第三章测试1.The Boolean expression A. 1 is equal to ( ).答案:A2.The Boolean expression A + 1 is equal to ( ).答案:13.The Boolean equation AB + AC = A(B+ C) illustrates ( )答案:the distribution law4.The associative law for addition is normally written as ( )答案:(A + B) + C = A + (B + C)5. A Boolean expression that is in standard SOP form is ( )答案:has every variable in the domain in every term6.Adjacent cells on a Karnaugh map differ from each other by答案:one variable7.SOP standard form is useful for constructing truth tables or for implementinglogic in PLDs.答案:对8.Logic simplification is still useful in nowadays FPGA designs.答案:错9.In synthesis, a netlist will be generated to describe the circuit completely.答案:对10.In FPGA design, the step that “maps” the design from the netlist to fit it to atarget device is known as "programming".答案:错第四章测试1.The 74138 decoder can also be used as ( ).答案:a DEMUX2.Assume you want to decode the binary number 0011 with an active-LOWdecoder. The missing gate should be ( ).答案:a NAND gate3.To expand a 2-bit parallel adder to a 4-bit parallel adder, you must ( ).答案:use two 2-bit adders with the carry output of one connected to the carry input of the other4.If an hex-to-binary priority encoder has its 0, 3, 6, and 14 inputs at the activelevel, the active-HIGH binary output is ( ).答案:11105.The continuous assignmentassign OUT = select ? A : B;specifies the condition that OUT = ( )if select = 1, else OUT = ( )if select = 0.答案:A, B6.Consider the initial block in the following:initialbeginA = 0;B = 0;#10 A = 1;#20 A = 0; B = 1;EndThen at t = 30, A is changed to ( ) and B to ( ).答案:0,17.The initial statement executes only once, starting from simulation time 0,and may continue with any operations that are delayed by a given number of time units.答案:对8.In Verilog HDL, the definitions of modules are allowed to be nested.答案:错9.The value z represents an unknown logic value in Verilog HDL.答案:错10.In Verilog HDL, ~(1010) is (0101), and !(1010) is 0.答案:对第五章测试1. The output of a D latch will not change if ( ).答案:Enable is not active2.The D flip-flop shown will ( ).答案:toggle on the next clock pulse3.For the J-K flip-flop shown, the number of inputs that are asynchronous is( ).答案:24.Assume the output is initially HIGH on a leading edge triggered J-K flip flop.For the inputs shown, the output will go from HIGH to LOW on which clock pulse?答案:35.The time interval illustrated is called ( ).答案:t PLH6.The advantage of dynamic RAM over static RAM is that ( ).答案:it is simpler and cheaper7.An asynchronous reset signal will override the clock on a FF.答案:对8.In Verilog HDL, an initial behavioral statement executes only once.答案:对9.In a Moore model, the outputs of the sequential circuit are not synchronizedwith the clock.答案:错10.The output of the Mealy machine is the value that is present immediatelybefore the active edge of the clock.答案:对第六章测试1.To cause a D flip-flop to toggle, connect the ( ).答案:2. A 4-bit binary counter has a terminal count of ( ).答案:153.Assume the clock for a 4-bit binary counter is 80 kHz. The output frequencyof the fourth stage (Q3) is ( ).答案:5 kHz4. A 4-bit parallel-in/parallel-out shift register will store data for ( ).答案:1 clock period5.An advantage of a ring counter over a Johnson counter is that the ringcounter ( ).答案:is self-decoding6. A possible sequence for a 4-bit ring counter is ( ).答案:… 1000, 0100, 0010 …7. A divide‐by‐N-counter is a counter that goes through a repeated sequence ofN states, and it is also known as a modulo‐N counter.答案:对8.For counters with unused states, it is necessary to ensure that the circuiteventually goes into one of the valid states so that it can resume normaloperation.答案:对9.For transmission, data from a UART is sent in synchronous parallel form.答案:错10.The maximum modulus of a counter is , where n is the number of stages (flip-flops) in the counter.答案:错第七章测试1.Static RAM is ( ).答案:volatile read/write memory2. A nonvolatile memory is one that ( )答案:retains data without power applied3.The advantage of dynamic RAM over static RAM is that ( ).答案:it is simpler and cheaper4. A 4-bit parallel-in/parallel-out shift register will store data for ( ).答案:1 clock period5.When data is read from RAM, the memory location is ( ).答案:unchanged6.The first step in a read or write operation for a random access memory is to( ).答案:place a valid address on the address bus7.Address multiplexing can reduce the number of pins in the IC package.答案:对8.One of the major applications of SRAMs is in cache memories in computers.答案:对9.RAM is used in a computer to store the BIOS (Basic Input/Output System.答案:错10.Memory expansion is accomplished by adding an appropriate number ofmemory chips to the address, data, and control buses.答案:对第八章测试1.The number of comparators required in a 10-bit flash ADC is ( ).答案:10232.If an anti-aliasing filter is not used in digitizing a signal the recovery process( )答案:may include alias signals3.An anti-aliasing filter should have ( )答案:4. A reconstruction filter ( ).答案:all of the above5.The ( ) of the A/D converter determines how close the actual digital outputis to the theoretically expected digital output for a given analog input.答案:accuracy6.The ( ) of ADC is determined by the number of bits it uses to digitize an inputsignal.答案:resolution7.An ADC is an analog data component答案:错8. A higher sampling rate is more accurate than a lower sampling rate for agiven analog signal.答案:对9.Two types of DAC are the binary-weighted input and the R/2R ladder.答案:对10.The Integral Nonlinearity of an ADC defines the maximum deviation of theADC transfer function from the best-fit line.答案:对。

遥感数字图像处理(山东联盟)智慧树知到答案章节测试2023年山东科技大学

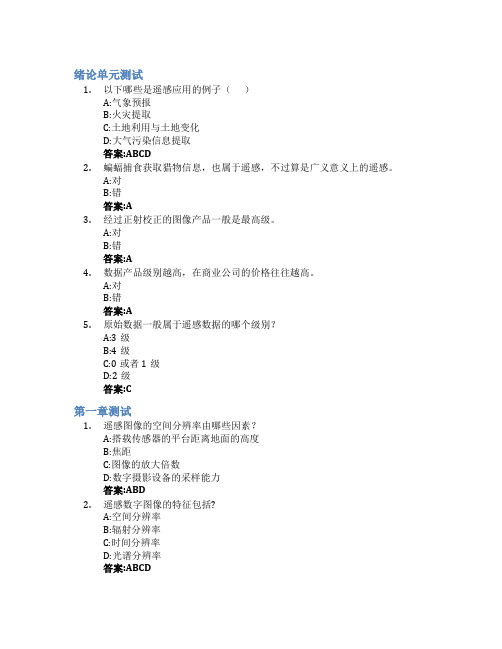

绪论单元测试1.以下哪些是遥感应用的例子()A:气象预报B:火灾提取C:土地利用与土地变化D:大气污染信息提取答案:ABCD2.蝙蝠捕食获取猎物信息,也属于遥感,不过算是广义意义上的遥感。

A:对B:错答案:A3.经过正射校正的图像产品一般是最高级。

A:对B:错答案:A4.数据产品级别越高,在商业公司的价格往往越高。

A:对B:错答案:A5.原始数据一般属于遥感数据的哪个级别?A:3级B:4级C:0或者1级D:2级答案:C第一章测试1.遥感图像的空间分辨率由哪些因素?A:搭载传感器的平台距离地面的高度B:焦距C:图像的放大倍数D:数字摄影设备的采样能力答案:ABD2.遥感数字图像的特征包括?A:空间分辨率B:辐射分辨率C:时间分辨率D:光谱分辨率答案:ABCD3.图像模数转换过程中的采样就是将电磁辐射能量离散化。

A:错B:对答案:A4.模拟图像与数字图像最大的区别在于:模拟图像中物理量的变化是连续的,而数字图像中物理量的变化是离散的。

A:错B:对答案:B5.图像的灰度直方图,其横坐标为像元的位置,纵坐标为像元的数量。

A:对B:错答案:B6.图像空间分辨率小于显示分辨率时,原图的显示质量得到了增强。

A:对B:错答案:B第二章测试1.数字图像在计算机上是以()方式存储的A:十六进制B:八进制C:二进制D:十进制答案:C2.比特序中的小端是指将高比特位(即逻辑上的高数据位)存储在低比特地址(即物理上的存储地址)。

A:对B:错答案:B3.ENVI软件标准格式的图像文件是_____存储格式A:封装式B:开放式答案:B4.假设有一幅2列、2行、3波段的遥感数字图像,各波段的数字值如下:25 1 2 4 34 3 3 4 2 1请选出该图像正确的BSQ存储方式:A:2,5,1,2,4,3,4,3,3,4,2,1B:2,5,4,3,1,2,3,4,4,3,2,1C:2,5,4,3,4,3,2,1,1,2,3,4D:2,1,4,5,2,3,4,3,2,3,4,1答案:B5.假设有一幅2列、2行、3波段的遥感数字图像,各波段的数字值如下:25 1 2 4 34 3 3 4 2 1请选出该图像正确的BIP存储方式:A:2,5,4,3,4,3,2,1,1,2,3,4B:2,5,1,2,4,3,4,3,3,4,2,1C:2,1,4,5,2,3,4,3,2,3,4,1D:2,5,4,3,1,2,3,4,4,3,2,1答案:C第三章测试1.数字图像处理的()过程中,输出图像每个像元的灰度值仅由对应的输入像元点的灰度值决定,它不会改变图像内像元之间的空间关系。

数字电子技术(怀化学院)知到章节答案智慧树2023年

数字电子技术(怀化学院)知到章节测试答案智慧树2023年最新绪论单元测试1.1、数字电路的特点有哪些?参考答案:便于集成,成本低廉。

;高速度,低功耗。

; 稳定性高,抗干扰能力强。

;易于设计,可编程性。

2.数字电路的BJT工作在放大区。

参考答案:错3.数字电路从结构上可分为组合逻辑电路和时序逻辑电路。

参考答案:对4.数字信号的特点是()。

参考答案:时间和幅值都是离散的。

5.数字电路的逻辑关系必须用1表示高电平,用0表示低电平。

参考答案:错第一章测试1.[+56]的补码是()。

参考答案:00111000B2.数字电路中,机器识别和常用的数制是:()。

参考答案:二进制3.十进制数127转换为二进制数得到()。

参考答案:11111114.逻辑变量的取值,1比0大。

参考答案:错5.“相同为1,不同为0”,它的逻辑关系是()。

参考答案:同或6.相同为0,不同为1,它的逻辑关系是()。

参考答案:异或逻辑第二章测试1.参考答案:12.逻辑代数的反演律和反演规则都是用来求反函数的。

参考答案:错3.因为逻辑表达式A+B+AB=A+B,所以AB=0.参考答案:错4.下列逻辑等式哪些是正确的。

()参考答案:;;;A+AB=A5.下列等式成立的是()。

参考答案:;;6.逻辑函数的最简式是唯一的。

参考答案:错7.卡诺图中为1的方格均表示逻辑函数的一个最小项。

参考答案:对8.每个最小项都是各变量相“与”构成的,即n个变量的最小项含有n个因子。

参考答案:对9.求逻辑函数的对偶式是。

参考答案:对10.逻辑函数的反函数是。

参考答案:错第三章测试1.下列逻辑器件属于组合逻辑电路的有()。

参考答案:编码器;译码器;数据选择器;数值比较器2.已知74HC138芯片的使能输入端信号为,,地址码A2A1A0=110,请问Y7-Y0的输出为()参考答案:111111013.八输入端的编码器按二进制数编码时,输出端的个数是()。

参考答案:3个4.编码器的输出量是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章测试1.数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

()A:错B:对答案:B2.十进制数(9)10比十六进制数(9)16小。

()A:错B:对答案:A3.逻辑变量的取值,1比0大。

()A:错B:对答案:A4.2019个1连续异或的结果是1。

()A:对B:错答案:A5.一位十六进制数可以用多少位二进制数来表示:()A:16B:4C:1D:2答案:B6.若输入变量A 、B 全为1时,输出F =0,则其输入与输出关系是:()A:与B:或C:与非D:非答案:C7.与模拟电路相比,数字电路主要的优点有:()A:通用性强B:抗干扰能力强C:保密性好D:容易设计答案:ABC8.在何种输入情况下,“与非”运算的结果是逻辑0。

()A:全部输入是1B:全部输入是0C:仅一输入是0D:任一输入是0答案:A9.电路如图(a),(b)所示,设开关闭合为1、断开为0;灯亮为1、灯灭为0。

灯的状态F 对开关A、B、C的逻辑函数表达式分别为:()。

A:B:C:D:答案:C10.用8421BCD码表示的十进制数45,可以写成:()A:[1010111]BCDB:[01000101]BCDC:[1011101]BCDD:75答案:B11.下列四个数中,最大的数是:()A:(198)10B:(AF)16C:(10100000)2D:(001010000010)8421BCD;答案:C第二章测试1.逻辑函数表达式的化简结果是唯一的。

()A:错B:对答案:A2.若两个函数具有相同的真值表,则两个逻辑函数必然相等。

()A:错B:对答案:B3.约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作 0。

()A:对B:错答案:A4.有冒险必然存在竞争,有竞争就一定引起冒险。

()A:错B:对答案:A5.在利用卡诺图进行逻辑表达式化简时,4个最小项合并成一项时可以消去的变量的个数是:()A:3B:2C:4D:1答案:B6.L= AB+C 的对偶式为:()A:A+BCB:(A+B)CC:ABCD:A+B+C答案:B7.下列几种说法中错误的是:()A:同一个卡诺图化简结果可能不是唯一的B:卡诺图中1的个数和0的个数相同C:逻辑函数的卡诺图是唯一的D:任何逻辑函数都可以用卡诺图表示答案:B8.函数F(A,B,C)=AB+BC+AC的最小项表达式为:()A:F(A,B,C)=∑m(0,2,4)B:F(A,B,C)=∑m(0,2,3,4)C:F(A,B,C)=∑m(2,4,6,7)D:F (A,B,C)=∑m(3,5,6,7)答案:A9.引起组合电路中竞争与险象的原因是:()A:电源不稳定B:干扰信号C:逻辑关系错D:电路时延答案:D10.逻辑函数Y=ABC+A+B+C的最简与或形式为:()A:1B:已是最简与或形式C:A+B+CD:0答案:C11.下列函数中,是最小项表达式形式的是:()。

A:B:C:D:答案:B12.A:B:C:D:答案:B13.A:B:C:D:答案:D14.A:B:C:D:答案:D15.A:B:C:D:答案:C第三章测试1.将二个或二个以上的普通TTL 与非门的输出端直接相连,可实现线与。

()A:错B:对答案:A2.CMOS 门电路的闲置输入端可以悬空。

()A:对B:错答案:B3.CMOS或非门与TTL或非门的逻辑功能完全相同。

()A:错B:对答案:B4.当TTL与非门的输入端悬空时相当于输入为逻辑1。

()A:对B:错答案:A5.以下电路中常用于总线应用的:()A:OC门B:CMOS与非门C:TSL传输门D:漏极开路门答案:C6.在 TTL 逻辑门中,为实现“线与”,应选用:()A:与非门B:三态门C:异或门D:OC门答案:D7.可用于总线结构进行分时传输的门电路是:()A:OCB:同或门C:三态门D:异或门答案:C8.以下电路中可以实现“线与”功能的有:()A:漏极开路门B:三态输出门C:与非门D:集电极开路门答案:AD9.三极管作为开关使用时,要提高开关速度,可以:()A:降低饱和深度B:采用有源泄放回路C:采用抗饱和三极管D:增加饱和深度答案:ABC10.CMOS数字集成电路与TTL数字集成电路相比突出的优点是:()A:高速度B:电源范围宽C:低功耗D:抗干扰能力强答案:BCD11.对于TTL与非门闲置输入端的处理,可以:()A:接地B:接电源C:通过3kΩ电阻接电源D:与有用输入端并联答案:BCD12.在正逻辑条件下,如图所示的逻辑电路为( ) 。

A:非门B:与门C:与非门D:或门答案:B13.已知某二变量输入逻辑门的输入A、B及输出Y的波形如图所示,则可判断该逻辑门为:( )。

A:或非门B:异或门C:与非门D:与门答案:D第四章测试1.编码与译码是互逆的过程。

()A:错B:对答案:B2.共阳接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

()A:错B:对答案:A3.八路数据分配器的地址输入(选择控制)端有8个。

()A:错B:对答案:A4.十六路数据选择器的地址输入(选择控制)端的个数为:()A:16B:2C:8D:4答案:D5.欲对全班43个学生以二进制代码编码表示,最少需要二进制码的位数是:()A:43B:6C:5D:8答案:B6.利用2个74LS138和1个非门,可以扩展得到1个( ) 线译码器。

A:2-4B:无法确定C:4-16D:3-8答案:C7.一位8421BCD码译码器的数据输入线与译码输出线的组合是:()A:1:10B:4:6C:4:10D:2:4答案:C8.已知 74LS138 译码器的输入三个使能端(E1=1, E2A = E2B=0)时,地址码 A2A1A0=011, ) 。

则输出 Y7 ~Y0 是:()A:11111101B:11111111C:10111111D:11110111答案:D9.与4位串行进位加法器比较,使用超前进位全加器的目的是:()A:完成自动加法进位B:完成4位串行加法C:完成4位加法D:提高运算速度答案:D10.如图所示组合逻辑电路的功能为半加器。

()A:对B:错答案:A11.如图所示所示组合逻辑电路的功能为:()A:实现输入变量的相加B:判断输入变量的奇偶性C:实现输入变量的相减D:判断输入变量是否相等答案:D12.用数据选择器实现逻辑函数的逻辑图如图所示,则逻辑函数Y=AB+BC+AC。

()A:错B:对答案:B13.如图所示,图中Y的最简与或表达式为:()A:B:C:D:答案:D14.A:错B:对答案:A第五章测试1.RS触发器的约束条件RS=0表示不允许出现R=S=1的输入。

()A:对B:错答案:A2.由两个TTL或非门构成的基本RS触发器,当 R=S=0时,触发器的状态为不定。

()A:错B:对答案:A3.同步触发器存在空翻现象,而边沿触发器和主从触发器克服了空翻。

()A:错B:对答案:B4.对边沿JK触发器,在CP为高电平期间,当J=K=1时,状态会翻转一次。

()A:对B:错答案:B5.下列触发器中没有约束条件的是:()A:边沿D触发器B:基本RS触发器C:同步RS触发器D:主从RS触发器答案:A6.如果把触发器的JK输入端接到一起,该触发器就转换成()触发器。

A:TB:RSC:T′D:D答案:A7.同步RS触发器的两个输入信号RS为00,要使它的输出从0变成1,它的RS应为:()A:10B:01C:00D:11答案:B8.如果把D触发器的输出Q反馈连接到输入D,则输出Q的脉冲波形的频率为CP脉冲频率f的:()A:四分频B:不变C:二分频D:二倍频答案:B9.要使JK触发器的输出Q从1就成0,它的输入信号JK就为:()A:无法确定B:10C:00D:01答案:D10.边沿式D触发器是一种()稳态电路。

()A:单B:双C:无D:多答案:B11.如果触发器的次态仅取决于CP()时输入信号的状态,就可以克服空翻。

A:无法确定B:高电平C:上升(下降)沿D:低电平答案:C12.为实现如图所示的触发器逻辑功能转换,虚线框中应为:( )。

A:或门B:与门C:非门D:异或门答案:C13.已知某触发器的功能表如表所示(A、B为触发器的输入),则其输出信号的表达式为:( )。

A:B:C:D:答案:D第六章测试1.时序逻辑电路的特点是:电路任一时刻的输出状态与同一时刻的输入信号有关,与原有状态没有任何的联系。

()A:错B:对答案:A2.异步时序电路的各级触发器类型不同。

()A:错B:对答案:A3.时序电路中一定含有记忆功能的器件。

()A:对B:错答案:A4.把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

()A:错B:对答案:A5.计数器的模是指构成计数器的触发器的个数。

()A:对B:错答案:B6.同步时序电路具有统一的时钟CP控制。

()A:对B:错答案:A7.同步计数器和异步计数器比较,同步计数器的最显著优点是:()A:电路简单B:不受时钟CP控制C:工作速度快D:触发器利用率高答案:C8.N个触发器可以构成能寄存( )位二进制数码的寄存器。

A:NB:2NC:N-1D:N+1答案:A9.根据组成计数器的各触发器状态翻转的时间与CP的关系分类,计数器可分为哪两种:()A:同步和异步B:二、十和N进制C:加法、减法及加减可逆D:摩尔型和米里型答案:A10.四个触发器组成的环行计数器最多有多少个有效状态。

()A:4B:6C:16D:8答案:A11.8位移位寄存器,串行输入时经()个脉冲后,8位数码全部移入寄存器中。

A:2B:4C:1D:8答案:D12.下列电路中,不属于时序逻辑电路的是:()A:译码器B:移位寄存器C:数据选择器D:计数器答案:AC13.某计数器的输出波形如图所示,该计数器是:()A:六进制计数器B:七进制计数器C:五进制计数器D:四进制计数器答案:A14.如图所示的电路(图中为上升沿Jk触发器),设触发器当前状态Q3 Q2 Q1为“100”,则在时钟作用下,触发器下一状态(Q3 Q2 Q1)为:()A:“000”B:“011”C:“101”D:“100”答案:B15.如图所示的时序逻辑电路的功能为:()A:四进制减法计数器B:四进制加法计数器C:六进制加法计数器D:六进制减法计数器答案:A16.如图所示时序逻辑电路的功能为同步四进制加法计数器。

()A:错B:对答案:B17.如图所示时序逻辑电路的功能为四进制减法计数器。

()A:错B:对答案:A18.如图所示电路的逻辑功能为异步三进制加法计数器。

(设触发器的初态为零)()A:对B:错答案:B19.用集成计数器74HVC161构成的计数器为八进制加计数器。

()A:错B:对答案:A20.用集成计数器74HVC161构成的计数器如图(a)所示,则该计数器的状态转换图为(b)。