原理图-P2020RDB-PCA

Quectel_EC20_原理图设计

VDD_EXT

DC_5V

S

USB_VBUS [1,2,8]

G

Reserved

R205 10K

W_DISABLE# [1]

USB_DP [1,8]

R204 10K

C201 NM

[2] W_DISABLE_M

Q203

DTC043ZEBTL

VBUS_CONTROL [2] ON/OFF_MCU [2] RESET_MCU [2] W_DISABLE_M [2] SLEEP_STATUS [2] SD_PWR_EN [7] VBAT_EN [3]

R207 10K

R208 4.7K

AP_READY [1,2]

[2] RESET_MCU

Q205

[2] SLEEP_STATUS

DTC043ZEBTL

[2] SLEEP_STATUS

Q206

Q207 2SA2018

B

DTC043ZEBTL

AP_READY [1,2]

R209 100K

AP_READY High level detection

C304

470uF 100nF

R307 470R

Supply Power for PCM Codec and SD Card

U302 1 IN EN SGM2019-ADJ OUT 5 4 VDD_3.0V

3

R303 47K 1%

VBAT

B

R304

51K

BP

1uF

100nF

R305 63.4K 1%

B

A

2. Pin 73~84 and 117~140 are unused in the design. You can ignore them in schematic and PCB decal. 3. The DBG_RXD/DBG_TXD, CTS/RTS/DCD and SD functions are not supported on EC20-E currently.

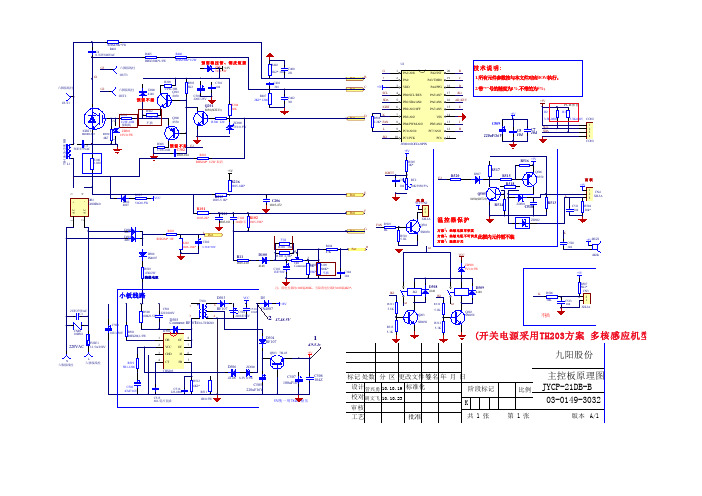

JYCP-21DB-B主控板原理图

Q505

VCC CN2

VCC

+

0805-5.1K*

R215

C206

0805-472 Port C102 104独石 F

风扇

-

8050(SOT23)

R514

ZD501

R513

AC

AC

R101

0805-2K*

C100 R102

0805-101 0805-39K*

2 1 XH-2A FAN R509 Q501 R510 5.1K SS8050

RHX470K*1W R401 C4 0.3UF/800VAC

R405 RHX330K*1/2W

R406 RHX330K*1/2W

预留稳压管、铜皮短接

ZD5 +18V 3V/0.5W

G3 G1

六脚接线柱

六脚接线柱

R402 C400 1K2* 1206 221 Port B C +5V SCL SDA IGBT Port D R508 2.2K* FAN L JK2 K C401 301 R407 2K2* 1206 C402 301 G F 1 2 3 4 5 6 7 8 9 10

C510

D5

+18V R311 5.1K

D505 EE16-THX203 Comment: RF107

IC500 1 2 3 OB VCC GND CT THX203 R512 OC OC IS FB 8 7 6 5

C504 104Z 220UF/25V

1N4007

2

17-18.5V

R313 5.1K

D507

+5V

R517 R515 R518

Q506 8550

DSPF2808-2802开发板原理图

5V

R57 10K 5 6 7 8 5 6 7 8

R58 10K

02 09 硬 52 汉 78 科 .t 技 ao

L3

D2 RED_LED

RN8

1nf caps should be placed closest to pins of the DSP

BLM21P221SN

PWM3H PWM3L

1 2 3 4

VDD_3.3 C40 100nF/25V

P10

P9

1

1

E2ROM电路

VDD_3.3 R12 R13 10K/5% 10K/5% GPIO33 GPIO32

96

89 82

IC6 A-B8 A-B7 PWM1_H PWM1_L PWM2_H PWM2_L PWM3_H PWM3_L 5V 13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4 VDD_3.3 C81 100nF/25V 7 6 B A

5

6

.c o

7

8

蜂鸣器和步进电机驱动电路

D1 1N4148

5V

C9100nF/25V

直流电机驱动电路

5V U7 Diode 1N4007 Diode 1N4007 D15 R63 1K/5% R82 0R/5% Q3 S8550 RXB GPIO23 TXB GPIO22 1 4 2 3 Q2 S8550 R62 1K/5%

485通讯(不用)

R83 470 J6 1 2 485

5V

5V

4n7 L4 BLM21P221SN

5AV

电源电路

S1 3 2 5V

VDD_1.8 VDD_3.3 R67 10K/5% 10K/5% R66

原理图设计——精选推荐

原理图设计DXP2004原理图设计⼀、实验⽬的1.了解DXP2004的软件平台,熟悉原理图设计的流程2.掌握元件库管理、元器件搜索、元件放置、绘图⼯局的应⽤。

⼆、实验仪器计算机、DXP2004软件三、实验原理图(课本P176页,图7-24)四、实验原理与步骤4.1新建⼯程项⽬(1)从桌⾯或者开始/所有程序中打开DXP 2004 SP2软件。

图1 从电脑开始菜单启动软件(2)打开软件后,从菜单File/New/Project下,选择PCB Project。

就可新建⼀个⼯程⽂件。

图2 新建⼯程的⽅法(3)⼯程⽂件新建后,准备保存⽂件夹。

先在E盘新建⽂件夹并将⽂件夹命名为⾃⼰的名字。

然后,选择File/Save Project,或者在Projects⼯具⾯板⾥,将⿏标移到PCB_Project1.PrjPCB上,点击右键,选择Save Project。

将⼯程项⽬保存到E盘以我们各⾃的名字命名的⽂件夹下,⼯程项⽬的名字为电话接听器。

保存之后,Project⼯作⾯板的PCB_Project1.PrjPCB变为图3a 从File菜单保存⼯程项⽬图3b 从⼯作⾯板保存⼯程项⽬(4)往⼯程项⽬中添加设计⽂件。

有两种⽅法。

第⼀种是从Project⼯作⾯板中,将⿏标移到电话接听器.PrjPCB出,点击右键进⼊,如下图4。

第⼆种⽅法是才菜单Project处进⼊选择。

图4 添加设计⽂件“Add New to Project”表⽰添加新的⽂件到⼯程项⽬中来。

在电路板设计中,主要添加四种类型的⽂件:Schematic(原理图设计⽂件)、PCB(PCB电路板设计⽂件)、Schematic Library (原理图元件库⽂件)、PCB Library(PCB元件库⽂件)。

“Add Existing to Project”表⽰从电脑中添加现有的⽂件到⼯程项⽬中来,现有的⽂件可以是⼯程项⽬中的任何⼀种⽂件。

本实验是原理图设计,选择Schematic。

EPC-6G2C-L 底板部分原理图介绍

修改日期修改内容1#2015-09-06增加RS232 BLOCK 1.MAINWDO_ENVREF_ADC USB_OTG2_ID USB_OTG2_D_P USB_OTG2_D_N USB_OTG1_ID USB_OTG1_D_P USB_OTG1_D_N UART8_TX UART8_RXUART7_TX UART7_RX SD2_CD SD2_WP UART4_TX UART4_RX UART3_TX UART3_RX UART2_TX UART2_RX UART1_RX SD2_CLK SD2_CMD SPI1_SCK SPI1_SS0SPI1_MOSI SPI1_MISO CAN1_RX CAN1_TX CAN2_RX CAN2_TX GPIO5_1GPIO5_2GPIO5_3GPIO5_4GPIO5_7GPIO5_8GPIO5_9GPIO4_14GPIO4_16ADC_CH8ADC_CH9PWM6_OUTTS_YN TS_YP TS_XN TS_XPLCD_PCLK LCD_DE LCD_HSYNC LCD_VSYNCLCD_RSTBOOT_MODE0BOOT_MODE1BT_CFG1_7CCM_CLK1_N CCM_CLK1_P ENET_MDCENET_MDIOENET1_RXD0ENET1_RXD1ENET1_RXEN ENET1_RXER ENET1_TXD0ENET1_TXD1ENET1_TXEN ENET1_TXCLKENET2_RXD0ENET2_RXD1ENET2_RXEN ENET2_RXER ENET2_TXD0ENET2_TXD1ENET2_TXEN JTAG_MOD JTAG_nTRST JTAG_TCK JTAG_TDI JTAG_TDO SD1_CD SD1_CLK SD1_CMD SD1_DATA[0..3]SD1_WPLCD_D[0..15]PWM5_OUT PMIC_ON_REQ MX6_ONOFF nRST_IN nRST_OUT MQS_RIGHT MQS_LEFT UART1_TX JTAG_TMS GND5V_IN 3V_BATUSB_OTG1_VBUS USB_OTG2_VBUS ENET2_TXCLK BT_CFG1_6nUSB_OTG1_CHDGPIO5_5GPIO5_6SD2_DATA[0..3]UART5_TX UART5_RX i.MX6UL02. MX6_PACK.SchDoc3.3VGND 5V EARTH 03. Power.SchDoc3.3V GNDWDO_EN SPI1_SCK SPI1_SS0SPI1_MOSI SPI1_MISOADC_CH8ADC_CH9BOOT_MODE0BOOT_MODE1BOOT_SELECT1JTAG_MOD JTAG_nTRST JTAG_TCK JTAG_TDI JTAG_TDO nRST_IN JTAG_TMS RUNERR 5V CAN1_RX CAN1_TX CAN2_RX CAN2_TX UART7_TX UART7_RX UART4_TX UART4_RX UART3_TX UART3_RX UART2_TX UART2_RX UART1_RX UART1_TX HPL HPRGPIO5_9GPIO3_25GPIO3_26CLR_REG SYS_MODE BOOT_SELECT0UART5_TX UART5_RX I2C_SCL I2C_SDA GPIO4_17GPIO4_18GPIO3_4GPIO2_9GPIO2_10GPIO2_11GPIO2_8GPIO2_13GPIO2_14GPIO2_15GPIO2_12USB_OTG1_ID04. Others.SchDoc3.3V GNDBEEP05. BEEP.SchDoc3.3V GNDI2C_SDAI2C_SCL3V_BAT 06. RTC.SchDoc3.3V GNDSD_CLK SD_CMD SD_D[0..3]SD_nWPSD_nCD TF07. TFCard.SchDoc5V GND EARTH3.3V USB_OTG2_ID USB_OTG2_D_P USB_OTG2_D_N USB_OTG1_ID USB_OTG1_D_P USB_OTG1_D_N USB_OTG1_VBUS USB_OTG2_VBUS nUSB_OTG1_CHDUSB HOST USB OTG08. USB_OTG_HOST.SchDoc5V GND3.3V TS_XM TS_XP TS_YM TS_YP TFT_D[0..15]TFT_PWM TFT_VSYNC TFT_HSYNC TFT_VCLK TFT_VDEN TFT_PWR LCD09. LCD.SchDocCSI_MCLKCSI_PCLK CSI_VSYNC CSI_HSYNC CSI_D0CSI_D1CSI_D2CSI_D3CSI_D4CSI_D5CSI_D6CSI_D7CSI_SDA CSI_SCL GND3.3V CSI_RST CSI_EN10. Camera.SchDoc3.3V GND3.3V GND3.3V GND3.3V5V GND 3.3V GNDEARTH5V GND 3.3V EARTH3V_BAT SPI1_SCK SPI1_SS0SPI1_MOSI SPI1_MISO5V GNDRTC 15uA 5V GND3.3V ENET1_MDCENET1_MDIO ENET1_RXDV ENET1_TXEN ENET1_nRST ENET1_TXD0ENET1_TXD1ENET1_RXD0ENET1_RXD1ENET2_MDC ENET2_MDIO ENET2_RXDV ENET2_TXEN ENET2_nRST ENET2_TXD0ENET2_TXD1ENET2_RXD0ENET2_RXD1ENET1_CLK ENET2_CLK ENET2_RXER ENET1_RXER 3.3V GND EARTH12. NET_Interface.SchDoc3V_BAT 5V MARK1ESD-MARKUR1URHOLE1HOLE4EARTHEARTHHOLE2HOLE5HOLE3HOLE6IDC-AUART3_TX UART3_RXUART3_CTS UART3_RTS 102,±10%C2GNDEARTHI2C_SCL I2C_SDA IDC-BSPI1_SCK SPI1_SS0SPI1_MOSI SPI1_MISORTC 0.25uASD2_DATA0SD2_DATA1SD2_DATA2SD2_DATA3SD2_CD SD2_WP SD2_CLK SD2_CMDI2C_SCL I2C_SDAI2C_SCL I2C_SDA 3.3V GNDGPIO5_5GPIO5_6GPIO5_9GPIO3_25GPIO3_26SD2_DATA[0..3]SD2_CD SD2_WP SD_CLK SD_CMD SD_D0UART_TXD UART_RXD UART_CTS_N UART_RTS_N WL_REG_ONWL_HOST_WAKE GND3.3V BT_WAKE BT_RST_NBT_HOST_WAKE SD_D1SD_D2SD_D3WIFI 11. WIFI.SchDoc GND3.3V UART3_TX UART3_RX UART3_RTS UART3_CTS SD2_CLK SD2_CMD GPIO5_9GPIO5_6GPIO3_25GPIO3_260Ω,±5%/NCR5LCD_RST LCD_RST UART6_TX UART6_RXGPIO3_4I2CGPIO2_14GPIO2_13GPIO2_11GPIO2_12GPIO2_10GPIO2_15GPIO2_8GPIO2_9SD1_DATA[0..3]GPIO5_5MARK4MARK2MARK3MARK5MARK6MARK7QCM1ZY QCUSB_OTG1_IDUSB_OTG1_IDGND 3.3V EARTHUART_TXD UART_RXDGND3.3V RS23215. RS232.SchDocGND3.3V UART1_TX UART1_RX UART1_TX UART1_RX1M Ω,1206R2TFT_D[0..15]TP922Ω,±5%R5322Ω,±5%R5122Ω,±5%R5222Ω,±5%R76EARTH1EARTH2102,±10%C110GNDEARTH11M Ω,1206R78102,±10%C111GNDEARTH21M Ω,1206R790Ω,±5%R1270Ω,±5%R1281234876522Ω×4,SMD RP121234876522Ω×4,SMD RP11SD2_DATA0SD2_DATA1SD2_DATA2SD2_DATA322Ω,±5%R1522Ω,±5%R117-1CGPIO-2C修改日期修改内容1#2015-09-06替换JTAG 接口为2.00mm ,删除调试串口4.OthersERRRUN3.3VERRRUN,0603LED2,0603LED1(1) LED 指示(3) JTAGSPI1_SCK3.3VBOOT_SELECT1SPI1_MISOSPI1_SS0BOOT_MODE1GND SPI1_MOSIWDO_ENBOOT_MODE0ADC_CH8ADC_CH9GND3.3V WDO_ENBOOT_MODE1BOOT_MODE0BOOT_SELECT1ADC_CH8ADC_CH9SPI1_SCK SPI1_SS0SPI1_MOSI SPI1_MISOERR RUN JTAG_nTRSTJTAG_TCKJTAG_MODJTAG_TDIJTAG_TDOJTAG_TMSnRST_IN JTAG_TMS JTAG_TDO JTAG_TDI JTAG_MOD JTAG_TCKJTAG_nTRSTnRST_IN RUNERR(2) 复位5V5V CAN2_TX UART7_TXUART4_RXUART3_TXUART1_RXUART2_RXUART5_TX UART7_RXHPRUART5_RX UART2_TX CAN1_TXI2C_SCL UART1_TXI2C_SDAUART4_TXCAN2_RX CAN1_RXHPLUART3_RX UART1_TXUART1_RX UART2_TX UART2_RX UART3_TX UART3_RX UART4_TX UART4_RX UART7_TX UART7_RX UART5_TX UART5_RX HPL HPR I2C_SCL I2C_SDA CAN1_TX CAN1_RX CAN2_TX CAN2_RXADC_CH8ADC_CH9I2C_SCLI2C_SDAGND5VSPI1_SCK SPI1_MOSI SPI1_MISO SPI1_SS0CAN1_RX CAN1_TX UART1_RXUART1_TX 1234567891011121314151617181920212223242526J2HEADER 13X2ERRRUNGND5V3.3V GNDCLKMISO RUN CR2CR1RX7RX5RX4RX3RX2RX1GND GNDSS MOSI ERR CT2CT1TX7TX5TX4TX3TX2TX13V35VNCNC RX8SDA NC AI9GND HPL 5VTX6SCL NC AI8NC HPR GNDHPLHPR CAN2_RX CAN2_TX UART2_RX UART2_TX UART3_RX UART3_TX UART4_RX UART4_TX UART7_RX UART7_TX UART5_RX UART5_TX 1K,±5%R135VPWR,0603LED3GND2K,±5%R12RST GNDGNDnRST_IN22Ω,±5%R160.1μF,±10%C290.1μF,±10%C30GND4.7K,±5%/NCR194.7K,±5%R21JTAG_MOD(4) 排座USB_BTQSPI_SDWDG(5) 模式配置JP1 3.3VJP6BOOT_MODEBOOT_SELECT1WDO_ENJP2GNDB1C3E2SS8050LT(1.5A)Q14.7K,±5%R17GND3.3VBOOT_MODE4.7K,±5%R22BOOT_MODE0BOOT_MODE13.3V4.7K,±5%R201K,±5%R18CLR_REGBOOT_SELECT0SYS_MODE BOOT_SELECT0CLR_REG SYS_MODE SDBOOT_SELECT0JP3CLRJP4GNDENCJP5GND启动方式短路JP1NAND USB 断开JP1、JP2、JP3(默认)短路JP2SD短路JP2、JP3QSPISYS_MODECLR_REG配置GPIO3_26GPIO5_9GPIO3_25GPIO3_25GPIO5_9GPIO3_26GPIO3_25GPIO3_26NC NC RX6P3.4P5.9NC NC NC NC TX8GPIO4_18GPIO4_17GPIO4_17GPIO4_18GPIO2_15GPIO2_13GPIO2_11GPIO2_9GPIO2_14GPIO2_12GPIO2_10GPIO2_8GPIO3_4GPIO3_4GPIO2_12GPIO2_11GPIO2_10GPIO2_8GPIO2_14GPIO2_9GPIO2_13GPIO2_15GPIO2_9GPIO2_8GPIO2_10GPIO2_11GPIO2_13GPIO2_12GPIO2_14GPIO2_15GPIO3_4GPIO4_18GPIO4_17GPIO5_9端子:1.10.11.0058,2.54mm,180°,4P,1.10.03.016314236×6×5.0mm,S1 3.3V 1234567891011121314151617181920212223242526J3HEADER 13X2HOST1JP7USB_OTG1_IDGNDUSB_OTG1_IDUSB_OTG1_IDJTAG_nTRSTJTAG_TDI JTAG_TMSJTAG_TCK JTAG_RTCKJTAG_TDO JTAG_nSRSTGNDJTAG3.3V0.1μF,±10%C139GND4.7K,±5%R14123456789102.00mm,10PJ4 3.3V213PESD3V3S2UTESD1GND10K,±5%R323.3V1234TS3544-0351B,90°S2断开 -> Internal Boot(Default)短接 -> USB Boot断开 -> 看门狗使能短接 -> 看门狗输出禁能断开 -> BOOT From NAND短接 -> BOOT From QSPI(Default)/SD断开 -> BOOT From QSPI短接 -> BOOT From SD断开 -> 正常工作模式短接 -> 厂商加密模式断开 -> 正常工作模式短接 -> 清空注册表断开 -> USB1做Device,默认短接 -> USB1做Host核心板附近A7工控板EPC-6G2C产品名称产品型号图纸描述设计人员设计日期2015-07-01审核人员审核日期2015-08-10双网口图纸名称ENET 图纸版本Rev.C林德光黄钦宁修改日期修改内容123#2015-11-18增加本地时钟13.ENET第 13 张 / 共 15 张A3广州致远电子股份有限公司3.3V3.3VGNDENET1_MDCENET1_MDIOENET1_RXDV ENET1_TXEN 3.3V3.3V GND GND ENET1_MDCENET1_MDIO ENET1_TXEN ENET1_RXDV 2.87K Ω,±0.5%R74GNDGNDPFBOUT13.3V3.3VGNDNET1_LINK_LEDNET1_SPEED_LEDN E T 1_T X D _P N E T 1_T X D _NN E T 1_R X D _P N E T 1_R X D _NP F B O U T 1P F B O U T 1PFBOUT1GNDGNDP H Y 1_A D 0GND3.3VNET1_LINK_LEDNET1_SPEED_LED L E D 1_C F GM D I X 1_E N MDIX1_EN ENET1_nRSTENET1_nRST ENET1_TXEN ENET1_TXD0ENET1_TXD1ENET1_MDCENET1_MDIOENET1_nRST3.3VGND600Ω,1A L3ENET1_MDIOENET1_RXDVENET1_TXD0ENET1_TXD1ENET1_TXD0ENET1_TXD1ENET1_RXD0ENET1_RXD1ENET1_RXD1ENET1_RXD0P H Y 1_A D 3P H Y 1_A D 4LED1_CFG10uF,6.3VC6510uF,6.3VC590.1μF,±10%C620.1μF,±10%C630.1μF,±10%C640.1μF,±10%C660.1μF,±10%C602K,±5%R612K,±5%R622K,±5%R602K,±5%/NCR642K,±5%R652K,±5%R582K,±5%R593.3VGNDPHY1_AD0ENET1_RXD02K,±5%R692K,±5%R572K,±5%R682K,±5%/NCR56ENET1_RXD12K,±5%R672K,±5%R66PHY1_AD3PHY1_AD4NET1_RXD_N NET1_RXD_P NET1_TXD_N NET1_TXD_PNET1_SPEED_LEDNET1_LINK_LED NET1_RXD_N NET1_TXD_NNET1_TXD_PNET1_LINK_LED NET1_SPEED_LED3.3V3.3VGNDENET2_MDC ENET2_MDIO ENET2_RXDV ENET2_TXENENET2_MDCENET2_MDIO ENET2_TXEN ENET2_RXDV 2.87K Ω,±0.5%R98GNDGNDPFBOUT23.3V3.3VGNDNET2_LINK_LEDNET2_SPEED_LEDN E T 2_T X D _P N E T 2_T X D _N N E T 2_R X D _PN E T 2_R X D _N P F B O U T 2P F B O U T 2PFBOUT2GNDGNDGNDP H Y 2_A D 0GND3.3VNET2_LINK_LEDNET2_SPEED_LED L E D 2_C F GM D I X 2_E N MDIX2_EN ENET2_nRST ENET2_nRST ENET2_TXEN ENET2_TXD0ENET2_TXD1ENET2_RXD1ENET2_RXD0ENET2_RXDV ENET2_MDCENET2_MDIOENET2_nRST3.3VGND600Ω,1A L5ENET2_MDIOENET2_RXDVENET2_TXD0ENET2_TXD1ENET2_TXD0ENET2_TXD1ENET2_RXD0ENET2_RXD1ENET2_RXD1ENET2_RXD0P H Y 2_A D 3P H Y 2_A D 4LED2_CFG10uF,6.3VC7710uF,6.3VC710.1μF,±10%C740.1μF,±10%C750.1μF,±10%C760.1μF,±10%C780.1μF,±10%C722K,±5%R842K,±5%R852K,±5%R862K,±5%/NCR912K,±5%R922K,±5%R822K,±5%R833.3VGNDPHY2_AD0ENET2_RXD02K,±5%R902K,±5%R812K,±5%/NCR892K,±5%R80ENET2_RXD12K,±5%R882K,±5%R87PHY2_AD3PHY2_AD4NET2_RXD_N NET2_RXD_P NET2_TXD_N NET2_TXD_PNET2_SPEED_LEDNET2_LINK_LED A V D D 3.3_2NET2_RXD_N NET2_TXD_NNET2_TXD_P NET2_LINK_LED NET2_SPEED_LED以太网CPU 到PHY 的数据线和时钟线要等长处理以太网CPU 到PH 的数据线和时钟线要等长处理ENET2_CLK ENET1_CLK 2K,±5%/NCR932K,±5%/NCR63NET1_RXD_P NET2_RXD_PENET2_CLKENET1_RXERENET2_RXERENET1_CLKENET1_RXER ENET2_RXER PHY1_CLKIN PHY2_CLKIN 49.9Ω,±1%R7049.9Ω,±1%R7149.9Ω,±1%R7249.9Ω,±1%R73GND0.1μF,±10%C670.1μF,±10%C683.3VGNDGND49.9Ω,±1%R9449.9Ω,±1%R9549.9Ω,±1%R9649.9Ω,±1%R970.1μF,±10%C790.1μF,±10%C803.3VGNDGNDi ENET1i ENET1i ENET1i ENET1i ENET1i ENET1i ENET1i ENET1i ENET2i ENET2i ENET2i ENET2i ENET2i ENET2i ENET2i ENET2AVDD3.3_1AVDD3.3_2AVDD3.3_2AVDD3.3_1LED_CFG 亮:Good Link01红灯绿灯闪烁:Activity 亮:100Mb/s 灭:10Mb/s 亮:Good Link 灭:No Link亮:100Mb/s 灭:10Mb/sIOVDD331TX_CLK2TX_EN 3TXD_04TXD_15TXD_26TXD_37RESERVED 8RESERVED 9RESERVED10R D -11R D +12A G N D 13T D -14T D +15P F B I N 116A G N D 17A V D D 3V 318P F B O U T 19R B I A S20LED_SPEED/AN121LED_LINK/AN022RESET_N 23MDIO 24MDC 25IOVDD3326X227X128DGND 29PFBIN230R X _C L K31R X _D V 32C R S /L E D _C F G 33R X _E R /M D I X _E N 34C O L /P H Y A D 035R X D _0/P H Y A D 136R X D _1/P H Y A D 237R X D _2/P H Y A D 338R X D _3/P H Y A D 439I O G N D40DP83848KSQ/NoPBU8DP83848KIOVDD331TX_CLK 2TX_EN 3TXD_04TXD_15TXD_26TXD_37RESERVED 8RESERVED9RESERVED10R D -11R D +12A G N D 13T D -14T D +15P F B I N 116A G N D 17A V D D 3V 318P F B O U T 19R B I A S20LED_SPEED/AN121LED_LINK/AN022RESET_N 23MDIO 24MDC 25IOVDD3326X227X128DGND 29PFBIN230R X _C L K31R X _D V 32C R S /L E D _C F G 33R X _E R /M D I X _E N 34C O L /P H Y A D 035R X D _0/P H Y A D 136R X D _1/P H Y A D 237R X D _2/P H Y A D 338R X D _3/P H Y A D 439I O G N D 40DP83848KSQ/NoPBU9DP83848KMDIX1_ENMDIX2_ENTP10TP82K Ω,±0.5%R992K Ω,±0.5%R7550M50MENET1_RXDV ENET1_RXD1ENET1_RXD01234876522Ω×4,SMDRP71234876522Ω×4,SMD RP81234876522Ω×4,SMDRP91234876522Ω×4,SMD RP10NC/E 1GND2CLKO 3VCC450.0000MHz,±30ppm/NCX33.3VGND600Ω,1A/NCL10GND 0.1μF,±10%/NCC120.1μF,±10%/NC C26GND0Ω,±5%/NC R300Ω,±5%/NCR40ENET1_CLKENET2_CLK CLK_50M0Ω,±5%R10Ω,±5%R45PHY1_CLKIN PHY2_CLKINA7工控板EPC-6G2C产品名称产品型号图纸描述设计人员设计日期2015-07-01审核人员审核日期2015-08-10以太网接口图纸名称NET_Transformer 图纸版本Rev.C林德光黄钦宁修改日期修改内容123#2015-09-06增加IP4220_Transformer第 14 张 / 共 15 张A3广州致远电子股份有限公司NET1_TXD_PEARTHGND NET1_RXD_P 3.3V NET1_RXD_NNET1_TXD_N NET1_TXD_P NET1_TXD_N NET1_RXD_P NET1_RXD_NGND3.3V3.3V102,±10%C83TX1_PTX1_N RX1_PRX1_N TPOUT+1MT 2TPOUT-3NC 4NC 5TPIN+6MR 7TPIN-8TX+16EMT 15TX-14NC 13NC 12RX+11EMR 10RX-9HS16-102CS,12.6×6.7×6.2mmT10.1μF,±10%C810.1μF,±10%C82EARTHCHSGND1M11M21NC13.3V GND EARTH NET1_TXD_PNET1_TXD_N NET1_RXD_P NET1_RXD_N 3.3VGND75Ω,±1%R10275Ω,±1%R10375Ω,±1%R10475Ω,±1%R105265431IP4220CZ6D9S H0TD1+1TD1-2RD1+3M1_14M1_25RD1-6NC17CHSGND18TD2+9TD2-10RD2+11M2_112M2_213RD2-14NC215CHSGND216L E D 1_G -17L E D 1_G +18L E D 1_R -19L E D 1_R +20L E D 2_G -21L E D 2_G +22L E D 2_R -23L E D 2_R +24HLJ5622S-8P8C-1×2J10HLJ5622S-8P8C-1×2NET2_SPEED_LED NET1_SPEED_LEDNET2_LINK_LEDNET1_LINK_LED EARTHNET2NET13.3V3.3V0.1μF,±10%C1420.1μF,±10%C143330Ω,±5%R106330Ω,±5%R107GND330Ω,±5%R101330Ω,±5%R1000.1μF,±10%C40.1μF,±10%C13GNDNET1_LINK_LEDNET1_SPEED_LED NET1_SPEED_LED NET1_LINK_LEDNET2_TXD_PNET2_RXD_PNET2_RXD_NNET2_TXD_NNET2_TXD_PNET2_TXD_N NET2_RXD_P NET2_RXD_N NET2_LINK_LEDNET2_SPEED_LEDNET2_SPEED_LED NET2_LINK_LEDNET2_TXD_PNET2_TXD_N NET2_RXD_P NET2_RXD_NGND3.3V3.3V102,±10%C86TX2_PTX2_NRX2_PRX2_N TPOUT+1MT 2TPOUT-3NC 4NC 5TPIN+6MR 7TPIN-8TX+16EMT 15TX-14NC 13NC 12RX+11EMR 10RX-9HS16-102CS,12.6×6.7×6.2mmT20.1μF,±10%C840.1μF,±10%C85EARTHCHSGND2NC23.3VGND75Ω,±1%R10875Ω,±1%R10975Ω,±1%R11075Ω,±1%R111265431IP4220CZ6D12TX1_P TX1_N RX1_P TX2_PTX2_N RX2_P RX2_N RX1_N CHSGND1CHSGND2M11M21NC1M12M22NC2M12M22靠近网络变压器中心抽头(MT 、MR )放置电容100欧姆差分阻抗Bob-Smith 端接100欧姆差分阻抗靠近网络变压器中心抽头(MT 、MR )放置电容Bob-Smith 端接。

DB_PCap01Ax_0301_电容测试芯片

RMS 噪声和精度 vs. 输出数据频率.......................................................................................................... 2-3

2.2.2

RMS 噪声 vs. 供电电压............................................................................................................................... 2-5

1.1 性能特点

基于CMOS技术的数字测量原理 在接地模式中最多可以测量8路电容 在漂移模式最多可测量4路电容(零电势及

零偏压) 内部(接地)补偿和外部(漂移)寄生电容补

偿 高精度: 最高达

6 aF 在 5 Hz 和 10 pF 基础电容 17 位精度在5 Hz 和 100 pF基础电

2.1.1

绝对最额定值............................................................................................................................................... 2-2

5.1 配置 & 参数寄存器 5.2 配置寄存器的说明 5.3 读寄存器

6.1 DSP 管理和编程 6.2 存储器映射 6.3 存储器管理 6.4 OTP 固件编程 6.5 入门指南

7 其它

7.1 错误报告 7.2 文档历史

1-1

2-2 2-3 2-7 2-8 2-9

PADS、PCB原理图常见错误及DRC报告网络问题(精选)

PADS、PCB原理图常见错误及DRC报告网络问题(精选)第一篇:PADS、PCB原理图常见错误及DRC报告网络问题(精选)PADS/PCB/原理图常见错误及DRC报告网络问题1.原理图常见错误:(1)ERC报告管脚没有接入信号:a.创建封装时给管脚定义了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c.创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.2.PCB中常见错误:(1)网络载入时报告NODE没有找到:a.原理图中的元件使用了pcb库中没有的封装;b.原理图中的元件使用了pcb库中名称不一致的封装;c.原理图中的元件使用了pcb库中pin number不一致的封装。

如三极管:sch中pin number 为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:a.创建pcb库时没有在原点;b.多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:表示这个网络没有连通,看报告文件,使用选择CONNECTED COPPER查找。

另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。

如果作较复杂得设计,尽量不要使用自动布线。

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

AR2000sopc开发板 原理图

Configuration PLD.Sch LAN91C111.Sch Configuration PLD.Sch LAN91C111.Sch

Flash.Sch Flash.Sch

Leds Buttons.Sch Leds Buttons.Sch

Mictor Connector.Sch Mictor Connector.Sch

A

1

2

3

4

5

6

D

D

VDD_5P0

1 L1 47nH C1 104 C

2

C71 102

C2 104 U2 13 X8 8 4 VCC OUT 5 1 R1 1 20 GND *R VDD_3P3 49FCT3805PY GND GND VDD_3P3 VCC3_3 VCC3_3 12 11 9 10 MON_n OEA_n INA OA0 OA1 OA2 OA3 OA4 OB0 OB1 OB2 OB3 OB4 GND GND GND 2 3 4 6 7 19 18 17 15 14 5 8 16 4 3 2 1

GND J1 2 3 SMAREC B GND 5 1 4

GND

B GND C3 104 C72 102

GND

A Title Size Orcad B 1 2 3 4 5 Date: File: 23-Jun-2006 Sheet of E:\Work\Projects\sdb\Design\Hardware\SoC1x-Altera-AR2000.ddb Drawn By: 6 Number Revision

C74 102

C6 104

C75 102

C7 104

《单片机微型计算机原理与接口技术》第八章 80C51单片微机的系统扩展原理与接口技术

②开始数据传送 在串行时钟线(SCL)保持高电平的情况下,串行数据线(SDA )上发生一个由高电平到低电平的变化作为起始信号(START) ,启动I2C 总线。I2C总线所有命令必须在起始信号以后进行。 ③停止数据传送 在串行时钟线(SCL)保持高电平的情况下,串行数据线 (SDA)上发生一个由低电平到高电平的变化,称为停止信号( STOP)。这时将停止I2C 总线上的数据传送。 ④数据有效性 在开始信号以后,串行时钟线(SCL)保持高电平的周期 期间,当串行数据线(SDA)稳定时.串行数据线的状态表示数 据线是有效的。需要一个时钟脉冲。 每次数据传送在起始信号(START)下启动,在停止信号 (STOP)下结束。 在I2C总线上数据传送方式有两种,主发送到从接收和从发 送到主接收。它们由起始信号(START)后的第一个字节的最低 位(即方向位R/W)决定。

①串行数据线(MISO、MOSI) 主机输入/从机输出数据线(MISO)和主机输出/ 从机输入数据线(MOSI),用于串行数据的发送和接收。 数据发送时.先传送MSB(高位),后传送LSB(低位)。 在SPI设置为主机方式时,MISO线是从机数据输入线 ,MOSI是主机数据输出线;在SPI设置为从机方式时, MISO线是从机数据输出线,MOSI是从机数据输入线。

8.1.1外部并行扩展原理

单片微机是通过芯片的引脚进行系统扩展的。 80C51系列带总线的单片微机芯片引脚可以构成图8-1所 示的三总线结构.即地址总线(AB)数据总线(DB)和控制总 线(CB)。具有总线的外部芯片都通过这三组总线进行扩展。 (1)地址总线(AB) 地址总线由单片微机P0口提供 低8位地址A0~A7,P2口提 供高8位地址A8~A15。P0口是地址总线低8位和8位数据总线复 用口,只能分时用作地址线。故P0口输出的低8位地址A0~A7必 须用锁存器锁存。 锁存器的锁存控制信号为单片微机ALE引脚输出的控制信 号。在ALE的下降沿将P0口输出的地址A0~A7锁存。P0、P2口 在系统扩展中用做地址线后便不能作为一般I/O口使用。 由于地址总线宽度为16位,故可寻址范围为64 KB。 (2)数据总线(DB) 数据总线由P0口提供,用D0~D7表示。P0口为三态双向

【Allegro档案】CADENCE从原理图到PCB

【Allegro档案】CADENCE从原理图到PCBCADENCE从原理图到PCB步骤⼀.原理图1.建⽴⼯程与其他绘图软件⼀样,OrCAD以Project来管理各种设计⽂件。

点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第⼀项OrCAD_Capture_CIS_option with capture,点击Ok 进⼊Capture CIS。

接下来是File--New--Project,在弹出的对话框中填⼊⼯程名、路径等等,点击Ok进⼊设计界⾯。

2.绘制原理图新建⼯程后打开的是默认的原理图⽂件SCHEMATIC1 PAGE1,右侧有⼯具栏,⽤于放置元件、画线和添加⽹络等等,⽤法和Protel类似。

点击上侧⼯具栏的Project manager(⽂件夹树图标)进⼊⼯程管理界⾯,在这⾥可以修改原理图⽂件名、设置原理图纸张⼤⼩和添加原理图库等等。

1)修改原理图纸张⼤⼩:双击SCHEMATIC1⽂件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、⼤⼩等;2)添加原理图库:File--New--Library,可以看到在Library⽂件夹中多了⼀个library1.olb的原理图库⽂件,右键单击该⽂件,选择Save,改名存盘;3)添加新元件:常⽤的元件⽤⾃带的(⽐如说电阻、电容的),很多时候都要⾃⼰做元件,或者⽤别⼈做好的元件。

右键单击刚才新建的olb 库⽂件,选New Part,或是New Part From Spreadsheet,后者以表格的⽅式建⽴新元件,对于画管脚特多的芯⽚元件⾮常合适,可以直接从芯⽚Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,⽅便快捷。