定点DSPs的定标及其运算方法

IQ定标

基于IQmath库的定点DSP算法设计彭志明,李琳华南理工大学时间:2012年05月23日现代电子技术字体: 大中小关键词:定点DSPIQmathTMS320F28xx摘要:基于TI公司提供的IQmath库实现在定点DSP芯片TMS320F28xx上进行精确的浮点运算,方便开发人员采用C/C++编写浮点运算程序,可以节省设计和调试时间。

IQmath库主要应用于高速度和高精度的实时计算,与直接采用ANSI C语言相比效率更高,这对设计实时性要求很高的控制系统尤其重要。

关键词:IQmath库;TMS320F28xx;浮点运算;实时性引言DSP数字信号处理器分为定点和浮点两种基本类型,它们之间最大差异在于浮点DSP比定点DSP具有更强大的计算能力和更大范围的动态精度。

浮点DSP内部设有专门支持浮点运算的硬件单元,对浮点格式的数据可以直接通过代码加入硬件运算中,因此运算速度很高。

而定点DSP没有定点运算单元,它对浮点格式的实数必须通过软件才能实现,这样就增加了指令代码,间接地使得定点DSP运算速度低于浮点DSP,典型的浮点处理器,如TI公司的C6000系列,几乎所有的嵌入式微控制器都为定点处理器,如TI公司的C2000系列。

因为浮点DSP的价格更加昂贵,因此定点DSP仍然有其巨大的优势。

但是任何算法都需要进行浮点运算,因此如何提高在定点DSP上进行的浮点运算的速度和精度,就成为了用户开发时必须要考虑的关键问题。

TI公司专门为定点处理器TMS320C2000系列提供的IQmath库为解决上述问题提供了良好的实现方法。

1 数的定标:Q格式定点DSP不能直接处理小数,编程时处理小数有3种方法:①把变量定义成float类型。

该方法编程量最小,但编译出来的代码最大。

②把整数变量放大来表示小数。

这是许多开发定点DSP的程序员经常使用的方法,但程序不具有可移植性。

③采用整数定标的方法来确定小数,即采用Q格式来表示小数。

精品课件-数字信号处理(第三版) 刘顺兰-第7章

第7章数字信号处理中的有限字长效应

7.1.2 定点制误差分析 1. 数的定点表示 定点制下,一旦确定了小数点在整个数码中的位置,在整个

运算过程中即保持不变。因此,根据系统设计要求、 数值范围来 确定小数点处于什么位置很重要,这就是数的定标。 数的定标有Q表示法和S表示法两种。Q表示法形如Qn,字母Q后的 数值n表示包含n位小数。如Q0表示小数点在第0位的后面,数为整 数;Q15 表示小数点在第15位的后面,0~14位都是小数位。S表 示法则形如Sm.n,m表示整数位,n表示小数位。以16位DSP为例, 通过设定小数点在16位数中的不同位置,可以表示不同大小和不 同精度的小数。表7.1列出了一个16位数的16种Q表示、 S表示及 它们所能表示的十进制数值范围。

小的正数: (01.000..0)2×2-127=1×2-127≈5.9×10-39

(4) 当S=1,E=-127,F的23位均为1时,表示的浮点数为绝 对值最小的负数:

(10.111..1)2×2-127=(-1-2-23)×2-127≈-5.9×10-39 双精度浮点数占用8个字节(64位)存储空间,包括1位符号位、 11位阶码、 52位尾数,数值范围为1.7E-308~1.7E+308。

第7章数字信号处理中的有限字长效应

乘除运算时,假设进行运算的两个数分别为x和y,它们的Q 值分别为Qx和Qy,则两者进行乘法运算的结果为xy,Q值为Qx+Qy, 除法运算的结果为x/y,Q值为Qx-Qy。

在程序或硬件实现中,上述定标值的调整可以直接通过寄存 器的左移或右移完成。若b>0,实现x×2b需将存储x的寄存器左 移b位;若b<0,实现x×2b则需将存储x的寄存器右移|b|位即可。

称为小数点位置。

实验一 CCS使用及DSP基本数学运算

四、实验程序结构说明 1.math.c这个文件中包含了实验关于DSP运算的主演函数。 主要有: fixed_add(int x,int y):定点加法运算; fixed_sub(int x,int y):定点减法运算; fixed_mul(int x,int y):定点乘法运算; fixed_div(int x,int y):定点除法运算; float_add(double x,double y):浮点加法运算; float_sub(double x,double y):浮点减法运算; float_mul(double x,double y):浮点乘法运算; float_div(double x,double y):浮点除法运算; float_fixed(double x):浮点转定点运算; fixed_float(int x):定点转浮点运算;

结果不超过16位表示范围 • 设x的Q值为Qx,y的Q值为Qy,且Qx>Qy,加法/ 减法结果z的定标值为Qz,则: • z=x+y

zq 2

Qz

xq 2

Qx

yq 2 ] 2

Qx

Qy

xq 2

Qx

yq 2

( Qx Qy )

2Qx

( Qz Qx )

⑶加载源文件到工程

点击Project,选择Add Files to Project,添加 math.c、math.cmd、rts.lib文件到工程中。

①添加源文件到工程 在下拉菜单中选择.c点击打开,即可添加 源程序到工程中

②同样的方法可以添加文件math.cmd、rts.lib到工 程文件中 在下面窗口中可以看到math.c、rts.lib文件已经加 到工程文件中。

浮点,simulink 定标指导,定点

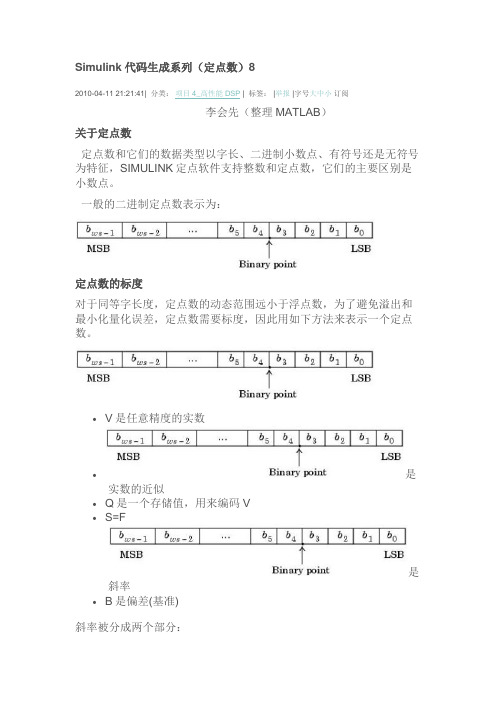

Simulink代码生成系列(定点数)82010-04-11 21:21:41| 分类:项目4_高性能DSP | 标签: |举报 |字号大中小订阅李会先(整理MATLAB)关于定点数定点数和它们的数据类型以字长、二进制小数点、有符号还是无符号为特征,SIMULINK定点软件支持整数和定点数,它们的主要区别是小数点。

一般的二进制定点数表示为:定点数的标度对于同等字长度,定点数的动态范围远小于浮点数,为了避免溢出和最小化量化误差,定点数需要标度,因此用如下方法来表示一个定点数。

∙V是任意精度的实数∙是实数的近似∙Q是一个存储值,用来编码V∙S=F是斜率∙B是偏差(基准)斜率被分成两个部分:∙确定二进制小数点,E是2的幂指数∙F是斜率调整因子,规范化时1≤F﹤2只有缩放标度的二进制小数∙F=1∙S=F=∙B=0一个被量化的实数的标度用斜率S定义,这被严格的限制为2的幂,负的2的幂指数被称为分数长度,分数长度是二进制小数点右边的比特数。

对于仅有缩放的二进制小数,定点数据类型表示为:∙signed types —fixdt(1, WordLength, FractionLength)∙unsigned types —fixdt(0, WordLength, FractionLength)整数是定点数类型的特殊情况,整数的用斜率为1直接标度,偏差为0,或者相当于分数长度为0,整数表达为:∙signed integer —fixdt(1, WordLength, 0)∙unsigned integer —fixdt(0, WordLength, 0)斜率和偏差(基准)标度当用斜率和偏差标度,被量化的实数的斜率S和偏差B可以使任何值,斜率必须是正数,用S和B定点数被表达为:∙fixdt(Signed, WordLength, Slope, Bias)范围和精度数的范围给出了表达的限制,精度给出了表达连续两数之间的距离,定点数的范围和精度取决于字的长度和标度。

西北工业大学DSP实验(定点数据表示与处理实验)

西北工业大学DSP实验(定点数据表示与处理实验)实验名称定点数据表示与处理实验课程名称 DSP系统实验实验室名称水下电子信息与通信综合实验室姓名学号班级日期一、实验目的掌握数据的定点表示方法;理解数据的量化效应;掌握定点数的溢出、饱和对数据处理的影响;二、实验要求1(理解定点数量化、溢出与饱和的原理;2(建立工程并编写源程序;3(运行程序并观察、分析运行结果。

三、实验原理实验分成信号的量化、定点数的溢出与饱和两个相对独立的实验。

3.1 信号的量化通常模拟数字转换(A/D转换)是数字信号处理的第一步,模数转换在时间上将采样信号离散化,在幅度上对信号进行量化编码,量化将连续的幅度信息变换成了离散的幅度信息。

幅度的离散化,即量化会产生误差,误差的大小与位数有关,即位数越高,误差越小;而位数越小,误差越大。

信号的量化实验首先产生一个16位的正弦波信号,然后依次屏蔽掉信号的低4为、8为和10位,构成可以与16位数据在幅度上可以比拟的12为、8为和6为数据,从而模拟16位、12位、8位和6位量化编码的过程,比较不同位数量化编码的效果。

3.2 定点数的溢出与饱和定点数可以表示的数值范围与数据的位数有关,与浮点数相比,定点数可以表示的数值范围要小得多。

定点数运算式,如果运算值超过了可以表示的最大值,会发生数据的溢出。

在运算中溢出会造成很大的误差,应尽量避免。

DSP处理器一般都有饱和模式。

在饱和模式下,溢出数据用带有正确符号的最大值填充,相当于对运算结果进行了限幅,使结果不会超出数值的表示范围。

定点数的溢出与饱和实验中,让DSP 分别在非饱和模式和饱和模式下对两组数据进行处理,说明溢出、饱和的情况。

一组数据种是将一个数反复的加上一个常数,这个数的数值会不断增加,当大到超过16位定点数的表示范围时,会发生溢出,观察非饱和模式与饱和模式的差别。

另一组数据是16位的正弦波,将正弦波数据乘上一个常数,当正弦波的数值大时,乘上常数会超过16位定点数的表示范围,而发生溢出,观察非饱和模式与饱和模式的差别。

DSP(知识点+思考题)

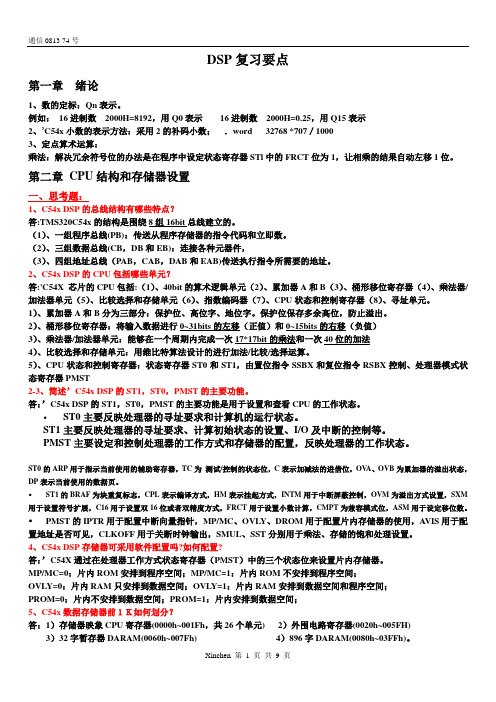

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

dsp数的定标名词解释

dsp数的定标名词解释DSP是数字信号处理(Digital Signal Processing)的缩写,是指利用数字技术对信号进行处理的一种方式。

数字信号处理是现代通信技术、音频处理、图像处理、雷达信号处理等众多领域中的关键技术之一,被广泛应用于各个领域。

DSP数的定标是指对数字信号进行精度补偿、峰值标定和校准,以确保测量结果的准确性和可靠性。

定标是指在已知标准参考信号下对DSP系统进行校正,使得系统能够正确地量化输入信号并进行相应的数字处理。

在DSP系统中,数的定标是非常重要且必要的一步。

它旨在确保DSP系统在各种环境和条件下的性能稳定和可靠性。

数的定标涉及到几个关键的步骤,下面将对这些步骤进行详细解释。

首先,数的定标需要确定DSP系统的量化精度。

量化精度是指系统可以采样和量化的最小输入变化。

通过在已知输入信号下对系统进行测试,可以确定系统可以准确测量的最小变化值。

这个步骤通常涉及选择适当的参考信号源,并在不同的输入水平下进行测试。

根据测试结果,可以确定系统的量化精度。

接下来,数的定标还需要考虑系统的峰值标定。

峰值标定是指确定DSP系统可以正确定量的最大输入信号。

这对于在系统使用过程中能够正确处理高幅度信号至关重要。

峰值标定可以通过将已知幅度的信号输入到系统中,并观察系统是否能够准确测量这些信号的幅度来实现。

通过对系统进行多个不同幅度的测试,可以确定系统的峰值标定值。

此外,校准也是数的定标的重要一环。

校准是指对DSP系统进行调整和校正,以确保其输出的准确性和稳定性。

校准通常涉及对系统的各个部分进行测试,并根据测试结果进行相应的调整。

校准可以包括对时钟源的校准、模数转换器的校准以及滤波器的校准等。

数的定标还需要考虑信号的线性性。

线性性是指系统对输入信号的响应与输入信号幅度成正比。

在进行数的定标时,需要检查系统的线性性,并在必要时进行校正。

这可以通过对多个不同幅度的输入信号进行测试来实现。

最后,数的定标也需要考虑对系统进行环境测试。

IQmath的应用

IQmath库的定点DSP算法设计引言DSP数字信号处理器DSP数字信号处理器是一个实时处理信号的微处理器,分为定点和浮点两种基本类型,它们之间最大差异在于浮点DSP比定点DSP具有更强大的计算能力和更大范围的动态精度。

浮点DSP内部设有专门支持浮点运算的硬件单元,对浮点格式的数据可以直接通过代码加入硬件运算中,因此运算速度很高。

而定点DSP没有定点运算单元,它对浮点格式的实数必须通过软件才能实现,这样就增加了指令代码,间接地使得定点DSP运算速度低于浮点DSP,典型的浮点处理器,如TI公司的C6000系列,几乎所有的嵌入式微控制器都为定点处理器,如TI公司的C2000系列。

因为浮点DSP的价格更加昂贵,因此定点DSP仍然有其巨大的优势。

但是任何算法都需要进行浮点运算,因此如何提高在定点DSP 上进行的浮点运算的速度和精度,就成为了用户开发时必须要考虑的关键问题。

TI公司专门为定点处理器TMS320C2000系列提供的IQmath库为解决上述问题提供了良好的实现方法。

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

1 数的定标:Q格式有符号数的表示法,机器数(出现在电脑的二进位数值)有3个特点,无符号或符号转换成数值来表示,没有+10101这样的资料,而是以010101来表示,只表示单纯的整数或小数,小数点的位置预设在一定的位置而较少变动,它的长度受到电脑硬体的限制,而不能无限增长。

Q格式,就是将一个小数放大若干倍后,用整数来表示小数定点DSP不能直接处理小数,编程时处理小数有3种方法:①把变量定义成float类型。

定点 DSP 处理浮点数

定点DSP处理浮点数BG6RDFTMS320C5509A是16位定点数处理器,其累加器是32位/40位的。

在定点处理器中处理浮点数需要对定点数进行定标。

下面所说的定点数都是指有符号数。

通常采用的定标有Q15和Q31,分别表示小数点后有二进制15位和二进制16位。

因此16位Q15最大能表示的数是1 2 ,32位Q31最大能表示的数是1 2 。

定标不同的数可以直接相乘,例如Q13*Q15=Q28。

两个定标不同的数不能直接相加,比如Q13+Q15,通常要将Q15右移两位,转换为Q13后再相加,当然这样损失了两位的精度。

DSP进行的乘累加操作常常Q15的数,这样结果为Q30,存储在累加器中。

为了将累加器的结果转换为更为常用的Q31定标,55x系列DSP在状态寄存器ST1_55中设置了FRCT 控制位,FRCT=1时,乘积自动左移一位,这样乘积变成了Q31。

对于累加器中Q31定标的数,直接取累加器中高16位,就能获得结果的Q15定标数。

很多时候Q15不能解决问题,比如IIR滤波器num, den系数中通常有大于等于1的系数,超过了Q15的范围,只能用Q14,Q13等定标。

这时乘累加操作就需要进行修正了,比如IIR滤波器中系数用Qx定标,输入数据和输出数据用Qy定标,Q Q Q ,为获得Qy的输出数据必须将累加器中的乘积右移x位,另外在乘累加操作开始前必须将输入数据在累加器中左移y位,进行对齐后才能进行乘累加。

当然,这种修正都是在没有考虑FRCT 的情况下。

在C5500 DSPLIB中iircas51函数中,FRCT设置为1,输入输出数据采用Q15定标,如果系数也是Q15定标,则程序运行无误,如果系数采用Q14及以下定标则会产生严重的问题。

以下是其代码片段:MOV *AR0+ << #16, AC1 ; HI(AC1) = x(n)||RPTBLOCAL loop2‐1 ;inner loop: process a bi‐quadMPYM *AR1+, AC1, AC0 ; AC0 = b0*x(n)MACM *AR1+, *(AR3+T0), AC0 ; AC0 += b1*x(n‐1)MACM *AR1+, *AR3, AC0 ; AC0 += b2*x(n‐2)MOV HI(AC1), *AR3 ; x(n) replaces x(n‐2)||AADD T1, AR3 ; point to next x(n‐1)MASM *AR1+, *(AR4+T0), AC0 ; AC0 ‐= a0*y(n‐1)MASM *AR1+, *AR4, AC0 ; AC0 ‐= a1*y(n‐2)MOV rnd(HI(AC0)), *AR4 ; y(n) replaces y(n‐2)||AADD T1, AR4 ;point to next y(n‐1)MOV AC0, AC1 ;input to next biquad从代码片段可以看出,累加器AC0为Q31定标,输出数据是累加器高16位。

除法运算在定点DSP中的实现

20 06正

安阳师范学院学报

2 9

除法运算在定 点 D P中的 实现 S

丁 电 宽 万 毅2 ,

(. 1 安阳师范学院 电气电子信 息工程系 , 河南 安 阳 450 ;. 502 2 西南交通 大学 机 械工程学院 , 四川 成都 603 ) 10 1 f 摘 要] 分析 了定点 D P中数 的表示方法 , S 讨论 了两个定点 数的除法运算 机理 , 实现 了定 点 D P中数 的除法 运算。 S

1 2 数 据定 点格式 的 转换 .

在 一 个 D P系 统 中 , 际参 与 运 算 的 参 量 在 一 个 实 S 实

运 算 在 定 点 D P中的 实 现 问 题 及 编 程 处 理 手 段 进 行 了详 S

细 探讨 。

际工程环境 中都有一定 的动态 范 围, 该动态 范围确定 了 , S的值也就确定 了, 因此 需要 编程员在设计程序 之前 找 出

所 处理数的类型 , 即不 能确 定 小 数 点 的 位 置 ; 且 在 汇 编 而 语 言程 序 设 计 时 , 不 能 直 接 写 入 十 进 制 小 数 , 此 必 须 也 因

变成整 数 , 然后再将整数转换成相应 的 S 格式。例如设 …

=75 该 数 式 , 将 应

应的权 值的乘积之和 ; 同理 s 。 S 0分别是带符号纯小 o5 1 和 5

.

数 和整 数 的表 示 方 法 。 由 此 可 见 定 点 格 式 所 表 示 的数 的

范 围 和 数据 的 精 度 是 确 定 的 , 示 数 的 范 围越 大 则 数 据 表 的精 度 越 低 。 因 此 , 编 程 时 需 要 程 序 员 根 据 数 的 大 小 在

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字信号处理器是一种实DSPs(Digital Signal Processors)时、快速的实现各种数字信号处理运算的微处理器。由于它具有丰富的硬件资源、改进的并行结构、高速数据处理能力和强大的指令系统而在通信、航空、航天、雷达、工业控制、网络及家用电器等各个领域得到广泛应用。分为DSPs定点和浮点两种,系列是公司推出的位TMS320C2000TI 16定点。本文以该种芯片为例,讨论定点的定标和DSPsDSPs算术运算中的编程处理手段。所讨论的这些问题在系DSPs统设计中有实际的参考和应用价值。 一般来说,定点芯片价格低,运算中占用内存单元少,运算速度较快,但数的表示范围太小,且必须经过定标才能进行运算。采用浮点数可使数值的表示范围大大提高,保证了运算精度,且编程时不必考虑小数点的位置。但浮点芯片的价格要比定点芯片高的多。本文讨论的定点芯片系列采用补码形式TMS320C2000来表示无符号或有符号整数、小数及混合小数。它的表示形式是:符号位整数部分小数部分。那么,在运算过程中,..定点怎样表示混合小数,又如何去处理这样的小数运DSPs算呢?这就是下面所要讨论的问题。定点数的定标1 计算机在运算中操作的数可能是整数,也可能是小数或混合小数。然而,在执行算术运算指令时,并不知道当CPU前所处理的数据是整数还是小数,更不能指出小数点的位置在哪里。因此,在编程时必须由程序员指定一个数的小数点处于哪一位,这就是定标的概念。通过定标可以在位位16(/8位位数的不同位置上确定小数点,从而表示出一个范/24/32)围大小不同且精度也不同的小数。通常,定标方法有两种:表示法和表示法。以位QS16数为例,表示法用 QQ0、Q1、…Qi、…、Q15分别表示小数点在D0位之后、D1位之后、…Di位之后、…D15位之后注(意: D15位是符号位。显然,)Q0表示的是一个有符号的整数,而Q15表示的是一个有符号的小数,其他各种情况表示了一个有符号的混合小数,它可以含有个整数位和个小i15-i数位。对应的有的表示法,它与表示法的对S15.0~S0.15SQ应关系如表所示。由表可总结出下列几点:11(1)Q x的值表示小数点在位xDx之后,即位中有个小

16x

数位和个整数位。(15-x)(2)Qx的值决定了所表示数的精度为 x2-x。

同样一个位数,因为小数点的设定位置不同,它(3)16所表示的数就不同。例如:在Q15中,1080H=0.001 0000 1000 0000=2-3 +2 -8(10)

=0.12890625(10)在Q0中,1080H=0001 0000 1000 0000.=212 +2 7(10)

=4224(10)在Q7中,1080H=0001 0000 1.000 0000=25 +20 (10)

=33(10)(4)Qx的值不同,则位数的表示范围和精度也就不

x16

同。Qx的值越大,则数值范围越小,但精度越高;相反,xQx的值越小,则数值范围越大,但精度越低。因此对定点

x

数来说,数值范围和精度是一对矛盾,在程序设计中应该两者兼顾,充分考虑各种因素,以获取最佳的运算结果。由此可见,在使用定点时,如何选择合适的DSPsQx值是一个关键性问题。就计算机运算的处理过程来说,实际参与运算的都是变量,有的是未知的,有的则在运算过程中不断改变数值,但它们在一个实际工程环境中作为一个物理参量而言都有一定的动态范围。只要这个动态范围确定了,Q

x值也就确定了。因此,在程序设计前,编程员首先要通过细致和严谨的分析,找出参与运算的所有变量的变化范围,充分估计运算中可能出现的各种情况,然后确定采用何种定

作者简介:张卫宁~,女,副教授,主要从事数字信号处(1953)

理、嵌入式处理器应用技术的研究;赵子婴高工,

收稿日期:2001-04-25

定点的定标及其运算方法DSPs张卫宁,赵子婴 (山东大学信息科学与工程学院,济南) 250061

摘要 :分析了定点的定标问题,讨论了定点运算中的DSPsQx值选择和解决数值超范围的方法,提出了定点加法的通用处理方法,并DSPs

就定点运算程序设计中的一些具体问题进行了讨论。关键词:;定标;定点运算DSPs

Fixed-point DSPs' Scale Operation and Operation Method

ZHANG Weining, ZHAO Ziying(College of Information Science and Engineering, Shandong University, Jinan250061)【Abstract 】The paper analyzes the problem of fixed-point DSPs's scale operation, discusses the choice of Q

x number and the method of

how to solve the problem above the range of number. The paper puts a general-purpose algorithm on the fixed-point's addtion and discusses some specific problems about program design of DSPs 's fixed-point operation.【Key words】DSPs ; Scale operation; Fixed-point operation

第28卷 第3期Vol.28 № 3计 算 机 工 程Computer Engineering2002年3月

March 2002

・ 开发研究与设计技术・ 中图分类号: TP 301.6文章编号:1000—3428(2002)03 —0223—

03

文献标识码:

A

—223—标标准才能保证运算结果正确可靠。这里,可以参考文献[所讨论的理论分析法和统计分析法去确定变量绝对值的最1]大值,然后根据再确定 Qx的值。 x表表示法和表示法1 QS但是,计算机操作过程中的意外情况是无法避免的,即使采用统计分析法也不可能涉及到所有情况。因此,在定点运算过程中应该采取一些判断和保护措施特别(是在定点加法中。另外,在数字信号处理中的大量运)算是乘法和累加,应尽量采用纯整数或纯小数运算即(全部变量都用Q0或Q15格式表示。这样做的好处是操)作简单、编程方便。只有当纯整数或纯小数运算不能满足变量的动态范围和精度要求时,才采用混合小数表示法去进行定点运算。下面讨论数字信号处理中的主要运算:定点加法和定点乘法中的一些问题。定点加法运算2 DSP两定点数相加,被加数和加数必须有相同的Qx值,还要注意结果溢出问题。系列芯片提供了状态标TMS320C2000志寄存器的ST0D12位作为溢出标志位,当加法运算溢出OV时,该位置,表示有符号的加法运算结果不正确。但"1"OV并不能反映出加法的和是否超出Qx的表示范围。因为DSPs 的累加器是位的,只表示位有符号数产生了ACC32OV=132溢出。一般位微处理器例如的是位的,只能16(8086)ACC16表示单精度的和,而的则可以用双精度数表示加DSPsACC法和,这一特点对扩大定点加法的使用范围非常有利,尤其适于数字信号处理中的累加运算,但这也给判断是否超出Qx的表示范围带来困难。因此必须找到一种新的方法作为判断依据。下面通过一个实例讨论解决问题的方法。例如:用的指令求的定点TMS320C2000 DSPsADDA+B加法运算,其中、均为有符号数,则存在下面种情况:AB4①,;②,;③,;④,。A>0B>0A>0B<0A<0B<0A<0B>0如取±,±,并选择定标A=0.5B=0.5625Qx值为Q15,则在Q15下有: , +0.5(10)= 4000H +0.5625(10)= 4800H, -0.5(10)= C000H -0.5625(10)= B800H

的种情况示于表。由表可见:定点加法是比较A+B422复杂的,情况①和③的运算结果都超出Q15的表示范围,其中,情况①引起了符号位的改变,而情况③则向高ACC16位进位。情况②和④的运算结果虽然不超出Q15表示范围,但情况④有一个向高位进位。这样,如果编程者想ACC16读出正确的运算结果,就要针对不同情况制定出不同的读出方案,否则,就会得出错误的运算结果。针对正数正数情况①的读出方案:(1)+()假定只作正数正数的操作,那么在+Q15下,其可表示的数值范围是:,可表示的最大-1~+0.9999695(8000H~7FFFH)负数为;最小负数为;最大-0.000030517(FFFFH)-1(8000H)正数为。则有:0.9999695 (7FFFH)两正数相加最大结果是,不会7FFFH+7FFFH=FFFEH超出位范围,但此结果已经超出16Q15的表示范围,表现在符号位D15由变为。因此,如果只作一次加法,则运算"0""1"后只要检测到D15就说明此结果已经超出=1Q15的表示范围,此时,的ACCD16位是符号位,而D0~D15位均为运算结果,小数点仍在D15之后。表的种情况2 A+B4

在进行正数累加时,一旦确定了一种值后,就不必 Q考虑累加运算的结果是否超出表示范围,因为它是自动扩大Q结果位数的,即向的高位进位。但要保证所有参加ACC16加法运算的数据都具有同样的值,并要考虑是否会溢出,Q即是否超出位的表示范围。在读结果时,切记开始确定的31值并没有改变,即小数点的位置没有改变,这样,才能读Q出正确的结果。针对负数负数情况③的读出方案:(2)+()假定只作负数负数的操作,则在+Q15下,最小结果是,超出位范围,并超出8000H+8000H=10000H16Q15的表示范围,表现在符号位由变为,且的D15"1""0"ACCD16位由"0"变为。因此,如果只作一次加法,则运算后只要检测到"1" D15,就说明此结果已经超出=0Q15的表示范围,此时,

的ACCD16位是符号位,而D0~D15位均为运算结果,小数点仍在 D15之后。关于正数负数的分析(3)+ 假定只作正数负数的操作则从极限情况看在+,,Q15下最,大正数最大负数;最小负数最小正数,+=0.999939449+=-1均不超出Q15的表示范围。得出结论:任何在Q15下表示的一个正数和一个负数相加,其和都不会超出Q15的表示范围。显然,使用其它Qx值只是数值的表示范围有变化,而分析方法是一样的。如Q7指定小数点在D7位的后面,数的表示范围是:。当两正数相加的和≥时,-256~+255.9921875256D15位变为;当两负数相加的和时1 <-256D15位变为,都说