verilog源代码第8.9章例题

单片机习题及答案第8章

单片机习题及答案第8章单片机习题及答案第8 章】第八章系统扩展一、填空题1 、常用程序存储器芯片有,其中程序存储器芯片的代号,后2位数字代表程序存储器的容量。

2 、2864A 被当作程序存储器扩展后。

只能用命令读取数据,用OE; 2864A被当作数据存储器扩展后,只能用MOVX命令读取数据, 用RD 选通OE 。

3 、8051 扩展并行I/ O 口时,对扩展I / O 芯片输入/ 输出端的基本要求是:构成输出口时,接口芯片应具有功能;构成输入口时,接口芯片应具有功能。

4 、用74系列芯片,扩展输入口时,用为宜;扩展输出口时,用双向总线时,用74LS245 为宜;扩展单项总线时,用74LS244 为宜。

5 、51 系列单片机能扩展容量的程序存储器和数据存储器。

6 、从理论上讲,8051扩展并行I/ O 口最多可扩展16 个。

二、选择1、EPROM是(B )的程序存储器。

A、电擦除B、紫外线擦除C 、不须整片擦写D、以上都不对2、EEPROM是( A ) 的存储器。

A 、电擦除B 、紫外线擦除C 、必须整片擦写D 、以上都不对3、51 系列单片机可扩展( C ) 字节的程序存储器。

A 、8KB 、16KC 、64KD 、以上都不对4 、51 系列单片机可扩展 ( C )字节的数据存储器。

A 、8K B 、16K C 、64K D 、以上都不对5 、51 系列单片机的数据总线和地址总线的宽度分别是( A )。

A 、8 位和16 位B 、16 位和8 位C 、16 位和16 位D 、8 位和8位6、8051 扩展并行I / O 口输入输出操作时执行的指令和控制信号是(D )。

A、执行MOVX指令,用PSEN信号控制读B 、执行MOVC指令,用RD、WR信号控制读写C、执行MOVC 指令,用PSEN信号控制读D 、执行MOVX指令,用RD、WR信号控制读写7 、片选连接P2.6 ,扩展1 片4K 8 并行存储器芯片,其地址范围是( B )。

VerilogHDL数字系统设计——原理、实例及仿真作者康磊第8-13章第11章

4

冯· 诺依曼结构的处理器使用同一个存储器,经由同一个 总线传输,具有以下特点: (1) 结构上由运算器、控制器、存储器和输入/输出设备 组成。 (2) 存储器是按地址访问的,每个地址是唯一的。 (3) 指令和数据都是以二进制形式存储的。 (4) 指令按顺序执行,即一般按照指令在存储器存放的顺 序执行,程序的分支由转移指令实现。

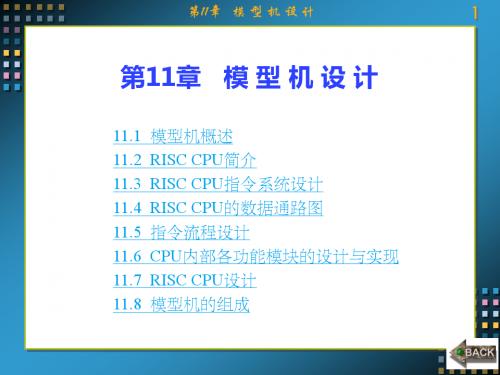

第11章 模 型 机 设 计

2

教材其余课件及动画素材请查阅在线教务辅导网 在线教务辅导网:

QQ址:

第11章 模 型 机 设 计

3

11.1 模 型 机 概 述

第11章 模 型 机 设 计

1

第11章 模 型 机 设 计

11.1 11.2 11.3 11.4 11.5 11.6 11.7 11.8 模型机概述 RISC CPU简介 RISC CPU指令系统设计 RISC CPU的数据通路图 指令流程设计 CPU内部各功能模块的设计与实现 RISC CPU设计 模型机的组成

(5) 以运算器为中心,在输入输出设备与存储器之间的数

据传送都途经运算器。运算器、存储器、输入输出设备的操 作以及它们之间的联系都由控制器集中控制。

第11章 模 型 机 设 计

5

哈佛结构使用两个独立的存储器模块,分别存储指令和 数据,并具有一条独立的地址总线和一条独立的数据总线, 具有以下特点: (1) 每个存储模块都不允许指令和数据并存,以便实现并 行处理。

CPU是计算机系统中最为重要的组成部分,它在计算机

系统中负责信息的处理和控制,因而被人们称为计算机的大 脑。CPU和外围设备构成计算机。模型机是一个简单的计算 机硬件系统,可以实现计算机的基本功能。 计算机的体系结构可分为两种类型:冯· 诺依曼结构和哈 佛结构。大多数CPU采用冯· 诺依曼结构。

verilog数字系统设计教程第四版例题源码

verilog数字系统设计教程第四版例题源码verilog数字系统设计教程第四版是一本深入浅出的数字系统设计教材,其中包括了丰富的例题与对应的源码。

以下是该书第四版例题的源码综述:1. `add` 模块源码:```verilogmodule add (input [3:0] a,input [3:0] b,output [3:0] sum,output carry);wire [3:0] intermediate_sum;wire intermediate_carry;assign intermediate_sum = a + b;assign carry = intermediate_sum[4];assign sum = intermediate_sum[3:0];endmodule````add` 模块实现了将两个四位数相加的功能。

本例子还演示了 verilog 的基本语法、数据类型、变量的使用、运算符的使用、模块的定义与实例化等基本概念。

2. `d_flip_flop` 模块源码:```verilogmodule d_flip_flop (input clk,input d,output reg q);always @(posedge clk) beginq <= d;endendmodule````d_flip_flop` 模块实现了一个 D 触发器的功能。

本例子还演示了时序逻辑的基本概念,包括时钟信号的使用和寄存器的使用。

3. `counter` 模块源码:```verilogmodule counter (input clk,input reset,output reg [7:0] count);always @(posedge clk or posedge reset) beginif (reset) begincount <= 0;end else begincount <= count + 1;endendendmodule````counter` 模块实现了一个八位计数器的功能。

第9章verilog_HDL_程序设计PPT课件

reg[12:0] temp2; reg[11:0] temp3; reg[10:0] temp4;

reg[9:0] temp5; reg[8:0] temp6;

reg[7:0] temp7;

function[7:0] mult8x1;

//该函数实现8×1乘法

input[7:0] operand; input sel;

temp5<=((mult8x1(a,b[2]))<<2);temp4<=((mult8x1(a,b[3]))<<3);

temp3<=((mult8x1(a,b[4]))<<4);temp2<=((mult8x1(a,b[5]))<<5);

temp1<=((mult8x1(a,b[6]))<<6);temp0<=((mult8x1(a,b[7]))<<7);

module count7(reset,clk,cout);

input clk,reset; output wire cout;

reg[2:0] m,n; reg cout1,cout2;

assign cout=cout1|cout2;

//两个计数器的输出相或

always @(posedge clk)

endmodule

(4)查找表乘法器

查找表乘法器将乘积直接存放在存储器中,将操作数 (乘数和被乘数)作为地址访问存储器,得到的输出 数据就是乘法运算的结果。

查找表方式的乘法器速度只局限于所使用存储器的存 取速度。但由于查找表规模随操作数位数增加而迅速 增大,因此如用于实现位数宽的乘法操作,需要 FPGA器件具有较大的片内存储器模块。比如,要实 现8×8乘法,要求存储器的地址位宽为16位,字长 为16位,即存储器大小为1M比特。

verilog_lecture8

¾

14.仿真与综合的不匹配

Full case

综合前后的仿 真结果一致

en信号被优化

14.仿真与综合的不匹配

Parallel case

具有优先级

综合为两个 and门

14.仿真与综合的不匹配

Casex

Casex 会将 x视为 无关位

综合前仿真一般会通过reset消除x态,综合后仿真容易产生 x态和毛刺带来的误动作。

Coding styles for FSMs

¾ Guideline: make each state machine a separate Verilog module 将状态机单独在一个模块中进行描述,可以方便进行状态 机的定义、修改、调试和逻辑综合。同时,如果状态机单独在 一个模块中进行描述,也会方便使用EDA工具进行状态机的辅 助设计 ¾ Guideline: make state assignments using parameters with symbolic state names 使用参数命令进行状态的形象化定义可以方便 verilog 代码的读写和修改。不推荐使用`define命令进行 状态的定义,因为它定义的是全局变量

State machine design techniques for Verilog

Synopsys FSM Tool a “/synopsys state_vector <state_vector_name>” Synopsys comment must be placed immediately before the state-reg declaration and the exact same “//synopsys enum<name>” comment, used above, must be place after the reg range declaration but before the state (and next) declarations.

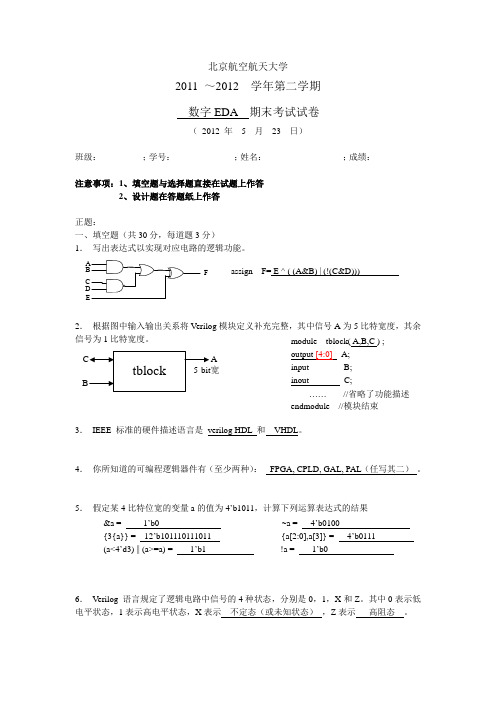

Verilog试题2012(A答案)

北京航空航天大学2011 ~2012 学年第二学期 数字EDA 期末考试试卷( 2012 年 5 月 23 日)班级:__________;学号:______________;姓名:__________________;成绩:___________注意事项:1、填空题与选择题直接在试题上作答2、设计题在答题纸上作答正题:一、填空题(共30分,每道题3分)1. 写出表达式以实现对应电路的逻辑功能。

F2. 根据图中输入输出关系将Verilog模块定义补充完整,其中信号A 为5比特宽度,其余信号为1比特宽度。

A 宽3. IEEE 标准的硬件描述语言是 verilog HDL 和 VHDL 。

4. 你所知道的可编程逻辑器件有(至少两种): FPGA, CPLD, GAL, PAL (任写其二) 。

5. 假定某4比特位宽的变量a 的值为4’b1011,计算下列运算表达式的结果6. Verilog 语言规定了逻辑电路中信号的4种状态,分别是0,1,X 和Z 。

其中0表示低电平状态,1表示高电平状态,X 表示 不定态(或未知状态) ,Z 表示 高阻态 。

assign F= E ^ ( (A&B) | (!(C&D)))module tblock( A,B,C ) ; output [4:0] A;input B;inout C; …… //省略了功能描述endmodule //模块结束 &a = 1’b0 ~a = 4’b0100 {3{a}} = 12’b101110111011 {a[2:0],a[3]} = 4’b0111 (a<4’d3) || (a>=a) = 1’b1 !a = 1’b07. 下面两段代码中信号in ,q1,q2和q3的初值分别为0,1,2和3,那么经过1个时钟周期后,左侧程序中q3的值变成 0 ,右侧程序中q3的值变成 2 。

8. Verilog 语言规定的两种主要的数据类型分别是 wire(或net) 和 reg 。

verilog数字系统设计教程习题答案

verilog数字系统设计教程习题答案verilog数字系统设计教程习题答案第二章1.Verilog HDL 既是一种行为描述语言,也是一种结构描述语言。

如果按照一定的规则和风格编写代码,就可以将功能行为模块通过工具自动转化为门级互联的结构模块。

这意味着利用Verilog语言所提供的功能,就可以构造一个模块间的清晰结构来描述复杂的大型设计,并对所需的逻辑电路进行严格的设计。

2.模块的基本结构由关键词module和endmodule构成。

3.一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

4.Verilog HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

5.不是6.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

7.综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile是作为一个综合的工业标准,它还有另外一个产品叫Behavior Compiler,可以提供更高级的综合。

另外最近美国又出了一个软件叫Ambit,据说比Synopsys的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit被Cadence公司收购,为此Cadence 放弃了它原来的综合软件Synergy。

Verilog-有限状态机设计

'define state1 2'b00

//不要加分号“;”

'define state2 2'b01

'define state3 2'b11

'define state4 2'b10

case(state)

'state1: …;

//调用,不要漏掉符号“'”

'state2: …;

……

要注意两种方式定义与调用时的区别,一般情况下,更倾向于采用方式1来定

if(x) next_state<=S3;

else next_state<=S0;

end

S3:begin

if(x)

next_state<=S1;

else next_state<=S2;

end

default: next_state<=S0;

/*default语句*/

endcase

end

always @(state) /*该过程产生输出逻辑*/

【例10.8】自动转换量程频率计控制器

/* 信号定义

clk:

时钟输入

reset:

系统复位信号

half_dollar: 投入5角硬币

one_dollar: 投入1元硬币

half_out: 找零信号

dispense: 机器售出饮料

collect:

提示取走饮料 */

第26页,共36页。

module FSM( clk, clr, out, start, step2, step3 ); input clk, clr, start, step2, step3;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第八章语法概念总复习练习1)以下给出了一个填空练习,请将所给各个选项根据电路图,填入程序中的适当位置。

a s s i g n m o d u l e;~| &i n p u t o u t p u ti n p u t s o u t p u t s e n d m o d u l eA ,B ,C , DAOI ( A, B, C, D, F )input A,B,C,D;output F;assign F = ((A&B)&(C&D));endmodule2〕 在这一题中,我们将作有关层次电路的练习,通过这个练习,你将加深对模块间调用时,管脚间连接的理解。

假设已有全加器模块FullAdder,若有一个顶层模块调用此全加器,连接线分别为W4,W5,W3,W1和W2。

请在调用时正确地填入I/O 的对应信号。

module FullAdder(A,B,Cin,Sum,Cout); input A, B, Cin;output Sum, Cout;endmodule3)initial begin endinitialSEL=0; A=0; B=0;#10 A=1;#10 SEL=1; #10 B=1;$monitor (SEL , A ,B , ,F) ; reg A, B , SEL;wire F;A Sum W1 W2 W3 W4 W5B Cin Countendmodule标准答案:module TestFixturereg A,B,SEL;wire F;MUX2M(SEL,A,B,F);initialbeginSEL=0; A=0; B=0;#10 A=1;#10 SEL=1; #10 B=1;endinitial$monitor(SEL,A,B,,F);endmodule4)指出下面几个信号的最高位和最低位。

reg [1:0] SEL; input [0:2] IP; wire [16:23] A;标准答案:MSB:SEL[1] MSB:IP[0] MSB:A[16]LSB:SEL[0] LSB:IP[2] LSB:A[23]5)P,Q,R都是4bit的输入矢量,下面哪一种表达形式是正确的。

1)input P[3:0],Q,R;2)input P,Q,R[3:0];3)input P[3:0],Q[3:0],R[3:0];4)input [3:0] P,[3:0]Q,[0:3]R;5)input [3:0] P,Q,R;标准答案:5)6)请将下面选项中的正确答案填人空的方括号中。

1. (0:2)2. (P:0)3. (Op1:Op2)4.(7:7)5. (2:0)6. (7:0)reg [7:0] A;reg [2:0] Sum, Op1, Op2;reg P, OneBit;initialbeginSum=Op1+Op2;P=1;A[ ]=Sum;.....end标准答案:57)请根据以下两条语句,从选项中找出正确答案。

7.1) reg [7:0] A;A=2'hFF;1) 8'b0000_0011 2) 8'h03 3) 8'b1111_1111 4) 8'b11111111标准答案:1)、2)7.2) reg [7:0] B;B=8 'bZ0;1) 8'0000_00Z0 2) 8'bZZZZ_00003) 8'b0000_ZZZ0 4) 8'bZZZZ_ZZZ0标准答案:4)8)请指出下面几条语句中变量的类型。

8.1) assign A=B;8.2) always #1Count=C+1;标准答案:A(wire) B(wire/reg) Count(reg) C(wire/reg)9)指出下面模块中Cin,Cout,C3,C5,的类型。

module FADD(A,B,Cin,Sum,Cout);input A, B, Cin;output Sum, Cout;....endmodulemodule Test;...FADDM(C1,C2,C3,C4,C5);...endmodule标准答案:Cin(wire) Cout(wire/reg) C3(wire/reg) C5(wire)10〕在下一个程序段中,当ADDRESS的值等于5'b0X000时,问casex执行完后A和B 的值是多少。

A=0;B=0;casex(ADDRESS)5'b00???: A=1;5'b01???: B=1;5'b10?00,5'b11?00:beginA=1;B=1;endendcase标准答案: A=1 and B=0;11)在下题中,事件A分别在10,20,30发生,而B一直保持X状态,问在50时Count的值是多少。

reg [7:0] Count;initialCount=0;alwaysbegin@(A) Count=Count+1;@(B) Count=Count+1;end标准答案:Count=1;(这是因为当A第一次发生时,Count的值由0变为1,然后事件控制 @(B) 阻挡了进程。

)12)在下题中initial块执行完后I,J,A,B的值会是多少。

reg [2:0] A;reg [3:0] B;integer I, J;initialbeginI=0;A=0;I=I-1;J=I;A=A-1;B=A;J=J+1;B=B+1;end标准答案:I=-1 (整数可为负数)J=0A=7 (A为reg型为非负数,又因为A为3位即为111)B=8 (在B=A时,B=0111,然后B=B+1,所以B=4’b1000)13)在下题中,当V的值发生变化且为-1时,执行完always块后Count的值应是多少?reg[7:0]V;reg[2:0]Count;always @(V)beginCount=0;while(~V[Count])Count=Count+1;end标准答案:Count=0;14)在下题中循环执行完后,V的值是多少?reg [3:0] A;reg V ,W;integer K;....A=4'b1010;for(K=2;K>=0;K=K-1)beginV=V^A[k];W=A[K]^A[K+1];end标准答案:V的值是它进人循环体前值的取反。

(因为V的值与0,1,0 进行了异或,与1的异或改变了V的值。

)15)在下题中,给出了几种硬件实现,问以下的模块被综合后可能是哪一种?always @(posedge Clock)if(A)C=B;1.不能综合。

2.一个上升沿触发器和一个多路器。

3.一个输入是A,B,Clock的三输入与门。

4.一个透明锁存器。

5.一个带clock有始能引脚的上升沿触发器。

标准答案:2,516)在下题中,always状态将描述一个带异步Nreset和Nset输入端的上升沿触发器,则空括号内应填入什么,可从以下五种答案中选择。

always @( )if(!Nreset)Q<=0;else if(!Nset)Q<=1;elseQ<=D;1.negedge Nset or posedge Clock2.posedge Clock3.negedge Nreset or posedge Clock4.negedge Nreset or negedge Nset or posedge Clock5.negedge Nreset or negedge Nset标准答案:417)在下题中,给出了几种硬件实现,问以下的模块被综合后可能是哪一种?1.带异步复位端的触发器。

2.不能综合或与预先设想的不一致。

3.组合逻辑。

4.带逻辑的透明锁存器。

5.带同步复位端的触发器。

1.always @(posedge Clock)beginA<=B;if(C)A<=1'b0;end标准答案:52.always @( A or B)case(A)1'b0: F=B;1'b1: G=B;endcase标准答案:23.always @( posedge A or posedge B )if(A)C<=1'b0;elseC<=D;标准答案:14.always @(posedge Clk or negedge Rst)if(Rst)A<=1'b0;elseA<=B;标准答案:2 (产生了异步逻辑)18)在下题中,模块被综合后将产生几个触发器?always @(posedge Clk)begin: Blkreg B, C;C = B;D <= C;B = A;end1. 2个寄存器 B 和 D2. 2个寄存器 B和 C3. 3个寄存器 B, C 和 D4. 1个寄存器 D5. 2个寄存器 C 和D标准答案:219)在下题中,各条语句的顺序是错误的。

请根据电路图调整好它们的次序。

标准答案:1) 2)20)根据左表中SEL与OP的对应关系,在右边模块的空括号中填入相应的值。

SEL:OP000:1001:3 casex(SEL)010:1 3'b( ): OP=3;011:3 3'b( ): OP=1;100:0 3'b( ): OP=0;101:3 endcase110:0111:3标准答案:casex(SEL)3'bXX1: OP=3;3'b0X0: OP=1;3'b1X0: OP=0;endcase21)在以下表达式中选出正确的.1) 4'b1010 & 4'b1101 = 1'b12) ~4'b1100 = 1'b13) !4'b1011 || !4'b0000 = 1'b14) & 4'b1101 = 1'b15) 1b'0 || 1b'1 = 1'b16) 4'b1011 && 4'b0100 = 4'b11117) 4'b0101<<1 =5'b010118) !4'b0010 is 1'b09) 4'b0001 || 4'b0000 = 1'b1标准答案:3), 5), 8), 9)22)在下一个模块旁的括号中填入display的正确值。

integerI;reg[3:0]A;reg[7:0]B;initialbeginI=-1;A=I;B=A;$display("%b",B);( )A=A/2;$display("%b",A);( )B=A+14$diaplay("%d",B);( ) A=A+14;$display("%d",A);( ) A=-2;I=A/2;$display("%d",I);( ) end标准答案:I=-1;A=I;B=A;$display("%b",B);(00001111) A=A/2;$display("%b",A);(0111) B=A+14$diaplay("%d",B);(21) A=A+14;$display("%d",A);(5)(A 为4位,所以21被截为5)23)]。