16位乘法器学习笔记(Verilog语言源程序+仿真程序)

verilog 乘法 除法

Verilog乘法除法引言Verilog是一种硬件描述语言,用于描述数字系统的行为和结构。

在数字系统设计中,乘法和除法是非常常见的运算。

本文将详细讨论Verilog中的乘法和除法的实现方法和技巧。

乘法乘法的基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在Verilog中,乘法可以通过多种方式实现,包括硬件乘法器、查找表、移位运算等。

硬件乘法器硬件乘法器是一种专门用于执行乘法运算的电路。

它通常由多个乘法单元和加法器组成。

乘法单元用于执行部分乘法,而加法器用于将部分积相加得到最终的乘积。

在Verilog中,可以使用*操作符来表示乘法运算。

例如,A * B表示将A和B相乘得到的结果。

在编写Verilog代码时,可以使用assign语句将乘法运算的结果赋值给一个变量。

查找表乘法查找表乘法是一种使用查找表进行乘法运算的方法。

它通过预先计算所有可能的乘法结果,并将其存储在一个查找表中。

然后,根据输入的乘数,从查找表中查找对应的乘积。

在Verilog中,可以使用case语句来实现查找表乘法。

首先,需要定义一个包含所有可能乘积的查找表。

然后,使用case语句根据输入的乘数选择对应的乘积。

移位运算乘法移位运算乘法是一种使用移位运算进行乘法运算的方法。

它通过将乘数逐位与被乘数相乘,并将部分积相加得到最终的乘积。

在Verilog中,可以使用<<操作符进行左移位运算,用于将数值向左移动指定的位数。

例如,A << 2表示将A向左移动2位。

同样,可以使用>>操作符进行右移位运算。

除法除法的基本原理除法是一种基本的算术运算,用于计算两个数的商。

在Verilog中,除法可以通过多种方式实现,包括硬件除法器、查找表、移位运算等。

硬件除法器硬件除法器是一种专门用于执行除法运算的电路。

它通常由除法单元和其他辅助电路组成。

除法单元用于执行除法运算的主要计算,而辅助电路用于处理除法运算中的特殊情况,如除数为0或除数为负数。

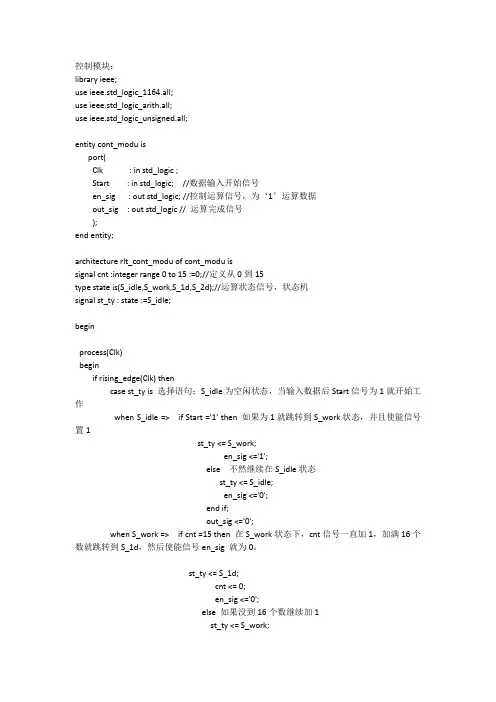

16位vhdl乘法器详解,加仿真图

控制模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity cont_modu isport(Clk : in std_logic ;Start : in std_logic; //数据输入开始信号en_sig : out std_logic; //控制运算信号,为‘1’运算数据out_sig : out std_logic // 运算完成信号);end entity;architecture rlt_cont_modu of cont_modu issignal cnt :integer range 0 to 15 :=0;//定义从0到15type state is(S_idle,S_work,S_1d,S_2d);//运算状态信号,状态机signal st_ty : state :=S_idle;beginprocess(Clk)beginif rising_edge(Clk) thencase st_ty is 选择语句;S_idle为空闲状态,当输入数据后Start信号为1就开始工作when S_idle => if Start ='1' then 如果为1就跳转到S_work状态,并且使能信号置1st_ty <= S_work;en_sig <='1';else 不然继续在S_idle状态st_ty <= S_idle;en_sig <='0';end if;out_sig <='0';when S_work => if cnt =15 then 在S_work状态下,cnt信号一直加1,加满16个数就跳转到S_1d,然后使能信号en_sig 就为0。

verilog 乘法 除法

verilog 乘法除法Verilog是一种硬件描述语言,广泛用于数字电路设计和验证。

在Verilog中,乘法和除法是两个常用的运算操作,用于实现数字电路中的乘法器和除法器。

本文将介绍Verilog中的乘法和除法的实现原理和方法。

一、Verilog中的乘法实现在Verilog中,乘法操作可以通过使用乘法运算符“*”来实现。

乘法运算符可以用于两个整数或两个实数之间的乘法运算。

具体实现乘法操作的方式可以有多种,下面将介绍一种基于加法和移位的乘法实现方法。

1. 基于加法的乘法实现基于加法的乘法实现方法是一种常见的乘法器实现方式。

它的原理是将被乘数和乘数分别拆分成若干个部分,并使用加法器将这些部分进行加法运算,最终得到乘法结果。

具体实现时,可以将被乘数和乘数分别拆分成若干个位数,并使用加法器将对应位数的部分进行加法运算。

每次运算时,先将被乘数的某一位与乘数的每一位相乘,然后将这些乘积通过加法器进行累加。

最终得到的累加结果就是乘法的结果。

2. 基于移位的乘法实现基于移位的乘法实现方法是另一种常见的乘法器实现方式。

它的原理是通过移位和累加的方式进行乘法运算。

具体实现时,先将被乘数和乘数进行位数对齐,然后从最低位开始,逐位地将被乘数与乘数的对应位相乘,并将乘积累加到最终的乘法结果中。

每次乘法运算完成后,将被乘数和乘数向左移位一位,继续进行下一位的乘法运算,直到所有位都计算完毕。

二、Verilog中的除法实现在Verilog中,除法操作可以通过使用除法运算符“/”来实现。

除法运算符可以用于两个整数或两个实数之间的除法运算。

具体实现除法操作的方式可以有多种,下面将介绍一种基于减法和移位的除法实现方法。

1. 基于减法的除法实现基于减法的除法实现方法是一种常见的除法器实现方式。

它的原理是通过多次减法运算来逼近除法的结果。

具体实现时,先将除数与被除数进行比较,如果除数小于被除数,则将除数与被除数相减,并将商的对应位设置为1。

verilog 乘法 除法

verilog 乘法除法Verilog是一种硬件描述语言,广泛应用于数字电路设计和验证。

本文将介绍Verilog中的乘法和除法原理及其在实际应用中的实现。

一、Verilog乘法器原理与实现1.原理Verilog乘法器的原理是基于位级运算。

输入的两个二进制数按位进行与运算,得到乘积的位级表示。

然后通过移位和加法运算,将位级乘积转换为最终的整数乘积。

2.实现Verilog乘法器的实现主要分为三个部分:全加器、位级乘法器和移位器。

全加器用于处理乘数和被乘数的各位与运算结果;位级乘法器用于计算乘数和被乘数的各位与运算;移位器用于调整位级乘积的位数。

3.实例以下是一个简单的Verilog乘法器实例:```module multiplier(input [7:0] a, b [7:0], output [15:0] result);wire [15:0] partial_product;wire [15:0] temp_result;// 位级乘法器wire [15:0] product [7:0];genvar i;generatefor (i = 0; i < 8; i = i + 1) beginassign product[i] = a * b[i];endendgenerate// 移位器assign partial_product = {product[7], product[6:0]};// 全加器assign temp_result = partial_product + result;assign result = temp_result;endmodule```二、Verilog除法器原理与实现1.原理Verilog除法器的原理是采用迭代算法,将除法问题转化为加法和减法问题。

除数和被除数按位进行与运算,得到余数的位级表示。

然后通过循环移位和加法运算,将余级表示转换为最终的整数商和余数。

verilog乘法运算

verilog乘法运算Verilog乘法运算是数字电路设计中非常基础的运算之一,其实现过程完全依赖于已有的硬件结构,通常使用乘法器实现。

下面介绍Verilog 乘法器的基本原理以及实现方法,供大家学习参考。

一、Verilog乘法器的基本原理乘法器是将两个二进制数进行乘法运算的一种专门的数字电路,可以通过硬件电路结构来实现。

具体来讲,它由一系列与门、异或门、加法器和移位器组成,因此可以将两个n位的二进制数相乘,得到一个2n位的结果。

二、Verilog乘法器的实现方法Verilog语言可以非常方便地实现乘法器,下面我们来看一下乘法器的代码实现。

假设我们要实现8位的乘法器,用于计算两个8位的二进制数的乘积,可以采用如下的Verilog代码:module multi(x, y, z);input [7:0] x, y;output [15:0] z;wire [15:0] w;assign w = x * y;assign z = w;endmodule上述代码中,module multi定义了一个名为multi的模块。

该模块有三个端口,x和y用于输入两个8位的二进制数,z用于输出它们的乘积。

在模块中,使用wire类型定义了一个16位的中间变量w,用来存储计算结果。

乘法操作是通过赋值运算符“*”完成的。

最后,把w直接赋值给z即可。

三、Verilog乘法器的测试最后,为了验证我们实现的乘法器的正确性,我们还需要编写一个测试程序。

测试程序通常采用assert语句检查乘法运算的正确性。

下面是一个测试程序的例子:module testbench;reg [7:0] x, y;wire [15:0] z;multi m(x, y, z);initial beginx = 10;y = 20;#1;assert(z == 200);$display("Test passed!");endendmodule上述代码中,testbench是一个测试程序的名字。

基于FPGA的16位乘法器的实现

目录引言....................................................................................................................................... - 1 - 摘要....................................................................................................................................... - 2 -一、乘法器概述....................................................................................................................... - 3 -1.1 EDA技术的概念........................................................................................................ - 3 -1.2 EDA技术的特点........................................................................................................ - 3 -1.3 EDA设计流程............................................................................................................ - 5 -1.4硬件描述语言(Verilog HDL)................................................................................ - 5 -二、16位乘法器的设计要求与设计思路.............................................................................. - 6 -2.2 设计要求.................................................................................................................... - 6 -三、16位乘法器的总体框图.................................................................................................. - 6 -四、16位乘法器的综合设计.................................................................................................. - 7 -4.1 16位乘法器功能........................................................................................................ - 7 -4.2 16位乘法器设计思路................................................................................................ - 8 -4.3 基于Verilog HDL 硬件语言的乘法器设计 ............................................................ - 8 -(1)输入模块......................................................................................................... - 8 -(2)乘法模块......................................................................................................... - 9 -五、总体调试与仿真结果..................................................................................................... - 10 -5.1乘法器的RTL Viewer .......................................................................................... - 10 -5.2 16位乘法器的系统程序:....................................................................................... - 11 -5.3计算结果仿真结果................................................................................................... - 12 -5.3.1仿真测试程序(a=6,b=10).............................................................................. - 12 - 总结......................................................................................................................................... - 16 - 参考文献................................................................................................................................. - 16 -引言随着微电子技术的飞速发展,集成电路工艺进入深亚微米阶段,特征尺寸变得越来越小。

verilog乘法运算和加法运算

verilog乘法运算和加法运算Verilog乘法运算和加法运算一、引言Verilog是一种硬件描述语言(HDL),广泛应用于数字电路设计领域。

其中,乘法运算和加法运算是Verilog中常见的基本算术运算。

本文将分别介绍Verilog中的乘法运算和加法运算的相关知识。

二、Verilog乘法运算1. 乘法运算符在Verilog中,乘法运算可以使用乘法运算符“*”来实现。

例如,使用如下语句进行乘法运算:```C = A * B;```其中,A和B是乘法运算的两个操作数,C是运算结果。

2. 乘法运算的类型在Verilog中,乘法运算可以分为有符号乘法和无符号乘法。

有符号乘法适用于带符号数的运算,而无符号乘法适用于无符号数的运算。

乘法运算的结果的位数可以根据操作数的位数自动确定。

3. 乘法运算的实现原理Verilog中的乘法运算可以通过移位和加法运算来实现。

具体来说,对于N位的操作数A和M位的操作数B,乘法运算可以分为M次移位和M次加法运算。

每次移位将A乘以B的一个比特位,并将结果累加到最终的运算结果中。

4. 乘法运算的应用乘法运算在数字电路设计中有广泛的应用,例如乘法器、滤波器、数字信号处理等领域。

乘法运算可以用于实现复杂的算法和逻辑功能。

三、Verilog加法运算1. 加法运算符在Verilog中,加法运算可以使用加法运算符“+”来实现。

例如,使用如下语句进行加法运算:```C = A + B;```其中,A和B是加法运算的两个操作数,C是运算结果。

2. 加法运算的类型在Verilog中,加法运算可以分为有符号加法和无符号加法。

有符号加法适用于带符号数的运算,而无符号加法适用于无符号数的运算。

加法运算的结果的位数可以根据操作数的位数自动确定。

3. 加法运算的实现原理Verilog中的加法运算可以通过逐位相加和进位的方式来实现。

具体来说,对于N位的操作数A和B,加法运算可以从低位到高位逐位相加,同时考虑上一位的进位情况。

verilog 乘法 除法

Verilog乘法和除法引言Verilog是一种硬件描述语言(HDL),用于描述数字电路的结构和行为。

它广泛用于设计和验证集成电路(IC)和其他数字系统。

Verilog的一个重要应用是实现乘法和除法运算。

在本文中,我们将详细介绍Verilog中的乘法和除法的实现原理和方法。

我们将讨论乘法和除法的基本概念、Verilog中的乘法和除法操作符、乘法和除法的实现技术等内容。

乘法乘法的基本概念乘法是一种基本的数学运算,用于计算两个数的乘积。

在Verilog中,乘法可以使用乘法操作符*来实现。

乘法操作符的语法如下:<result> = <operand1> * <operand2>;其中,<operand1>和<operand2>是要相乘的操作数,<result>是乘法的结果。

Verilog中的乘法操作符Verilog中的乘法操作符*可以用于乘法运算。

它可以用于任何大小的整数、浮点数和向量。

以下是一些使用乘法操作符的示例:// 乘法示例reg a = 5;reg b = 3;reg c;always @(*) beginc = a * b;end上述示例中,c的值将被计算为5 * 3,即15。

乘法的实现技术在硬件实现中,乘法通常使用乘法器来完成。

乘法器是一种特殊的电路,用于将两个数字相乘。

乘法器的实现方式有很多种,包括布斯算法、Wallace树算法、Dadda树算法等等。

这些算法都有各自的特点和适用范围。

在Verilog中,可以使用内置的乘法操作符*来实现乘法。

这些内置操作符会根据操作数的类型和位宽自动选择合适的乘法器。

除法除法的基本概念除法是一种基本的数学运算,用于计算两个数的商。

在Verilog中,除法可以使用除法操作符/来实现。

除法操作符的语法如下:<result> = <operand1> / <operand2>;其中,<operand1>和<operand2>是要相除的操作数,<result>是除法的结果。

乘法器verilog设计的设计方法

乘法器verilog设计的设计方法【1.乘法器的Verilog设计概述】乘法器是数字电路设计中常见的组件,其作用是将两个二进制数相乘得到结果。

Verilog是一种通用的硬件描述语言,可以用于描述和实现数字电路。

乘法器的Verilog设计就是利用Verilog语言实现乘法器的功能。

【2.乘法器Verilog设计的基本原理】乘法器Verilog设计的基本原理是通过移位和相加操作实现两个二进制数的乘积。

典型的乘法器架构包括全加器、半加器和数据选择器等。

在全加器中,乘数和被乘数分别经过多次移位操作后与乘法器输出相加,从而得到最终结果。

【3.乘法器Verilog设计的实现步骤】乘法器Verilog设计的实现步骤如下:1) 确定乘法器的输入和输出:根据需求确定乘法器的输入信号,如乘数和被乘数,以及输出信号,如乘积。

2) 编写Verilog代码:利用Verilog语言编写乘法器的逻辑功能,包括移位、相加和数据选择等操作。

3) 仿真和验证:对编写好的Verilog代码进行仿真和验证,确保其功能正确。

4) 优化和调试:根据仿真结果对代码进行优化和调试,以提高性能和减少资源占用。

5) 下载和测试:将设计好的乘法器下载到目标硬件,进行实际测试。

【4.乘法器Verilog设计的优化策略】1) 优化代码结构:合理划分模块,减少模块间的耦合度,提高代码的可读性和可维护性。

2) 采用高效的算法:如布斯算法、Wallace树等,提高乘法器的运算速度。

3) 减少资源占用:通过合理分配信号位数、使用紧凑型数据结构等方法,降低硬件成本。

4) 电源和时序优化:针对功耗和时序要求,采用适当的电路设计和优化技术。

【5.乘法器Verilog设计的应用领域】乘法器Verilog设计广泛应用于各类电子设备和系统中,如数字信号处理、图像处理、通信系统等。

在这些领域,乘法器作为基本组件,为实现高速、高效、低功耗的数字信号处理提供了有力支持。

【6.总结与展望】乘法器Verilog设计是数字电路设计的重要内容。

16位布斯算法乘法器和ALU

16位布斯算法乘法器和ALUBooth算法16位乘法器西安电子科技大学大三集成电路设计与集成系统专业尹俊镖一乘法器原理分析16位有符号乘法器可以分为三个部分:根据输入的被乘数和乘数产生部分积、部分积压缩产生和和进位、将产生的和和进位相加。

这三个部分分别对应着编码方式、拓扑结构以及加法器。

被乘数X(16-bit)符号位扩展S01?X(17-bit)X(17-比特)01?X2?XMUXADD/SUBBooth译码&ALU(17-bit)控制逻辑符号位扩展S乘积(低16-bit)乘数乘积(高16-bit)保留移出位右移2-bit1 编码方式:本设计采用booth2编码。

部分积是负数时S=1,部分积是正数时S=0;当部分积是+0时,E=1,部分积是-0时,E=0,其余情况E=S取反。

2 拓扑结构:本设计采用二进制树的拓扑结构。

二进制树拓扑结构排列的较为规整,且部分积压缩的速度也非常快。

部分积压缩的目的是为了减小进位传播的延时,采用进位保留加法器,根据当前位信息产生下一位的进位,仅仅产生而没有进位行波传播,这样就可以把当前的多位压缩到较少的位数。

经过几次压后,把部分积压缩成和以及进位。

部分积主要是通过counter和compressor进行压缩,通常使用(3:2)counter 和(4:2)compressor。

(3:2)counter其实质就是一个全加器,进位输入为ci,进位输出为c;(4:2)compressor可以由两个全加器组成,ci为进位输入,Coin为内部进位,输入到下一位的进位输入Ci,Coex为输出进位。

上图为二进制树的拓扑结构图,每4个部分积输入到一个(4:2)compressor 中,产生两个输出,则8个部分积使用3次(4:2)compressor就可以得到和和进位。

部分积的压缩方式可以见下图。

如图中所示,加上最后一个部分积的进位,共有9个部分积,本设计把最后的进位位移到第一个部分积上,使用5个全加器,把进位融合到第一个部分积,这样就转变成8个部分积了,再使用两级二进制树压缩,所以总共使用了三级压缩,最终得到部分积的和和进位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LCD1602显示源程序如下:module lcd1602(input clk, //60Minput rst_n,output lcd_p, //Backlight Source + lcd屏幕背光output lcd_n, //Backlight Source -output reg lcd_rs, //0:write order; 1:write dataoutput lcd_rw, //0:write data; 1:read dataoutput reg lcd_en, //negedge 在lcd_en下降沿需保证数据有效output reg [7:0] lcd_data);mux16mul(.rst_n(rst_n),.clk(clk),.start(start),.ain(data0),.bin(data1),.yout(data2),.done(done));//端口名称关联//--------------------lcd1602 order----------------------------parameter Mode_Set = 8'h31, //功能设置,Cursor_Set = 8'h0c, //光标设置Address_Set = 8'h06, //输入模式设置Clear_Set = 8'h01; //清屏设置/****************************LCD1602 Display Data****************************/ wire [7:0] data_r0,data_r1,data_r2; //乘数、被乘数wire [15:0]data0,data1; //结果显示wire [31:0]data2;wire [7:0] addr; //write addresswire start,done;assign data_r0 = 8'h30 + data0[7:0] ; // 8'h30在LCD1602上显示值为0。

assign data_r1 = 8'h30 + data1[7:0] ;assign data_r2 = 8'h30 + data2[7:0];//-------------------address------------------assign addr = 8'h80;/****************************LCD1602 Driver****************************///-----------------------lcd1602 clk_en---------------------reg [31:0] cnt;reg lcd_clk_en;always @(posedge clk or negedge rst_n)beginif(!rst_n)begincnt <= 1'b0;lcd_clk_en <= 1'b0;endelse if(cnt == 32'h24999) //600usbeginlcd_clk_en <= 1'b1;cnt <= 1'b0;endelsebegincnt <= cnt + 1'b1;lcd_clk_en <= 1'b0;endend//-----------------------lcd1602 display state-------------------------------------------reg [6:0] state;always@(posedge clk or negedge rst_n)beginif(!rst_n)beginstate <= 1'b0;lcd_rs <= 1'b0;lcd_en <= 1'b0;lcd_data <= 1'b0;endelse if(lcd_clk_en)begincase(state)//-------------------init_state---------------------6'd0: beginlcd_rs <= 1'b0;lcd_en <= 1'b1;lcd_data <= Mode_Set; //进入功能设置模式,“31”:数据总线8位,显示一行。

6*7点阵/每字符state <= state + 1'd1;end6'd1: beginlcd_en <= 1'b0; //lcd_en变低电平,使led_en出现下降沿state <= state + 1'd1;end6'd2: beginlcd_rs <= 1'b0;lcd_en <= 1'b1;lcd_data <= Cursor_Set;//光标设置:光标右移一格,且AC值加1.state <= state + 1'd1;end6'd3: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd4: beginlcd_rs <= 1'b0;lcd_en <= 1'b1;lcd_data <= Address_Set;//模式设置:写入新数据后光标右移,AC自增1state <= state + 1'd1;end6'd5: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd6: beginlcd_rs <= 1'b0;lcd_en <= 1'b1;lcd_data <= Clear_Set;//清屏操作:0x01state <= state + 1'd1;end6'd7: beginlcd_en <= 1'b0;state <= state + 1'd1;end//--------------------work state--------------------6'd8: beginlcd_rs <= 1'b0;lcd_en <= 1'b1;lcd_data <= addr; //write addrstate <= state + 1'd1;end6'd9: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd10: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= "R"; //write datastate <= state + 1'd1;6'd11: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd12: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= "E"; //write datastate <= state + 1'd1;end6'd13: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd14: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= "S"; //write datastate <= state + 1'd1;end6'd15: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd16: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= ":"; //write datastate <= state + 1'd1;end6'd17: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd18: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= data_r1; //write data: tens digitstate <= state + 1'd1;end6'd19: beginlcd_en <= 1'b0;state <= state + 1'd1;6'd20: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= "*";state <= state + 1'd1;end6'd21: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd22: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= data_r0; //write data: single digitstate <= state + 1'd1;end6'd23: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd24: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= "="; //write data: single digitstate <= state + 1'd1;end6'd25: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd26: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= data_r2; //write data: single digitstate <= state + 1'd1;end6'd27: beginlcd_en <= 1'b0;state <= state + 1'd1;end6'd28: beginlcd_rs <= 1'b1;lcd_en <= 1'b1;lcd_data <= "."; //write data: single digitstate <= state + 1'd1;end6'd29: beginlcd_en <= 1'b0;state <= 6'd8;enddefault: state <= 6'bxxxxxx;endcaseendendassign lcd_rw =1'b0; //only write//------------------backlight driver----------------assign lcd_n = 1'b0;assign lcd_p = 1'b1;Endmodule16位乘法器源程序如下:`timescale 1ns / 1psmodule mux16(clk,rst_n,start,ain,bin,yout,done);input clk; //芯片的时钟信号。