分频器的verilog hdl语言

Verilog实现任意分频

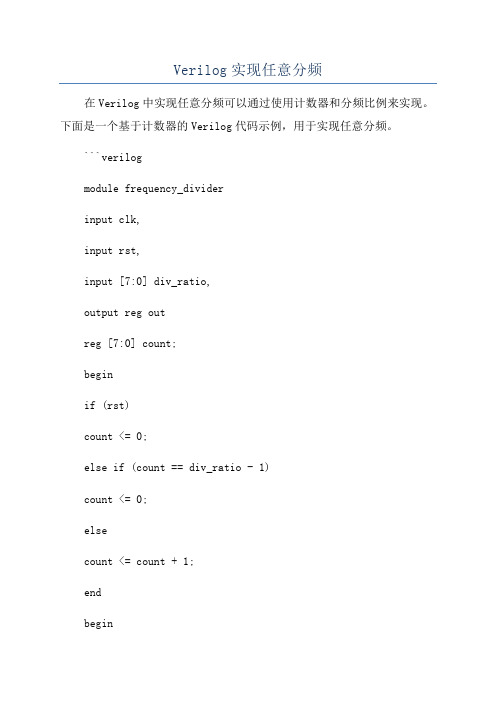

Verilog实现任意分频在Verilog中实现任意分频可以通过使用计数器和分频比例来实现。

下面是一个基于计数器的Verilog代码示例,用于实现任意分频。

```verilogmodule frequency_dividerinput clk,input rst,input [7:0] div_ratio,output reg outreg [7:0] count;beginif (rst)count <= 0;else if (count == div_ratio - 1)count <= 0;elsecount <= count + 1;endbeginif (rst)out <= 0;else if (count == div_ratio - 1)out <= ~out;endendmodule```在以上代码中,我们定义了一个名为"`frequency_divider`"的模块,该模块具有以下输入和输出:- `clk`:时钟信号- `rst`:复位信号- `div_ratio`:分频比例,使用8位二进制表示,范围为0到255- `out`:输出信号我们使用一个8位计数器(`count`)来进行分频。

每当计数器达到分频比例减1时,输出信号取反。

例如,如果分频比例为1,则输出信号将与时钟信号同步;如果分频比例为2,则输出信号将是时钟信号的一半频率;如果分频比例为4,则输出信号将是时钟信号的四分之一频率,以此类推。

需要注意的是,以上示例代码仅展示了分频的基本原理,并未考虑输入和输出信号的时序问题,如使 `div_ratio` 在运行时可更改、输出信号的不稳定性等。

针对具体应用需求,可以根据实际情况做出适当的修改和调整。

希望以上内容对您有所帮助!。

第04讲 Verilog-HDL语法——第2部分 语法要点

` timescale

`timescale 说明延时单位及延时精度

格式:`timescale <time_unit> / <time_precision> 如:`timescale 1 ns / 100 ps

`timescale必须在模块之前出现 `timescale 1 ns / 100 ps // All time units are in multiples of 1 nanosecond module MUX2_1 (out, a, b, sel); output out; input a, b, sel; wire sel_;

12 'H83a 8'b1100_ 0001 64'hff01 9'O17 32'bz01x 3’b1010_ 1101 6.3 32e- 4 4.1E3 unsized decimal (zero-extended to 32 bits) unsized hexadecimal (zero- extended to 32 bits) 8-bit binary 64-bit hexadecimal (zero- extended to 64 bits) 9-bit octal Z-extended to 32 bits 3-bit number, truncated to 3’b101 decimal notation scientific notation for 0.0032 scientific notation for 4100

hex

oct

dec

bin

ACSII

string

time

strength module

转义符

\t \n \\ \” %% \<1-3 digit octal number>

verilogHDL分频器(奇数分频和偶数分频)

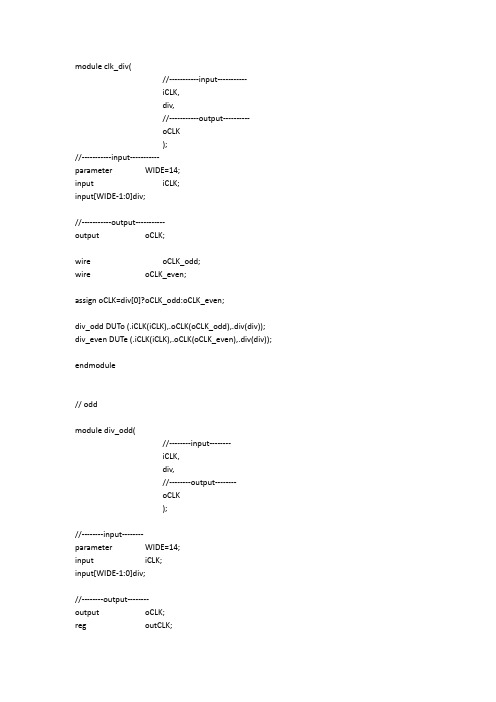

module clk_div(//-----------input-----------iCLK,div,//-----------output----------oCLK);//-----------input-----------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//-----------output-----------output oCLK;wire oCLK_odd;wire oCLK_even;assign oCLK=div[0]?oCLK_odd:oCLK_even;div_odd DUTo (.iCLK(iCLK),.oCLK(oCLK_odd),.div(div)); div_even DUTe (.iCLK(iCLK),.oCLK(oCLK_even),.div(div));endmodule// oddmodule div_odd(//--------input--------iCLK,div,//--------output--------oCLK);//--------input--------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//--------output--------output oCLK;reg outCLK;/*=========================== solve 1=========================== reg cout;reg[WIDE-1:0] cnt;initial cnt=0;wire inCLK;reg cc;initial cc=0;always @(posedge cout)cc<=~cc;assign inCLK = iCLK^cc;always @(posedge inCLK)beginif(cnt<(div[WIDE-1:1]))begincnt<=cnt+1;cout<=1'b0;endelsebegincnt<=0;cout<=1'b1;endendalways @(negedge iCLK)outCLK <= cout;assign oCLK=cc;*///======================== //solve 2//======================== reg[WIDE-1:0] cnt_a;initial cnt_a=0;reg[WIDE-1:0] cnt_b;initial cnt_b=0; reg cout_a;reg cout_b;always @(negedge iCLK)beginelse if(cnt_a<=(div[WIDE-1:1]))begincnt_a=cnt_a+1;cout_a=1'b1;endelse if(cnt_a>(div[WIDE-1:1])&&cnt_a<(div[WIDE-1:0]-1))begincout_a=1'b0;cnt_a=cnt_a+1;endelsebegincnt_a=0;endendalways @(posedge iCLK)beginif(cnt_b<=(div[WIDE-1:1]))begincnt_b=cnt_b+1;cout_b=1'b1;endelse if(cnt_b>(div[WIDE-1:1])&&cnt_b<(div[WIDE-1:0]-1))begincout_b=1'b0;cnt_b=cnt_b+1;endelsebegincnt_b=0;endendassign oCLK = cout_a&cout_b;endmodule//evenmodule div_even(//--------input--------iCLK,div,//--------output--------oCLK);//--------input--------parameter WIDE=14;input iCLK;input[WIDE-1:0]div;//--------output--------output oCLK;reg oCLK;initial oCLK = 1'b0;reg[WIDE-1:0] cnt;initial oCLK = 0;always @(posedge iCLK)beginif(cnt<(div[WIDE-1:1]-1))cnt <= cnt + 1;elsebegincnt <= 0;oCLK <= ~oCLK;endendendmodule//============================//testbench//============================/*module clk_div_test;//-----------input-----------parameter WIDE=14;reg iCLK;reg[WIDE-1:0] div;//-----------output-----------wire oCLK;clk_div cc(.iCLK(iCLK),.div(div),.oCLK(oCLK));always #20 iCLK = ~iCLK;initialbeginiCLK = 0;div=14'd7;#1000 $stop;endendmodule*/module clk_div14bits(clk,a,clkout);input clk,a;output clkout;reg clkout;wire oCLK1,oCLK2;clk_div cc1(.div(14'd8),.iCLK(iCLK),.oCLK(oCLK1)); clk_div cc2(.div(14'd9),.iCLK(iCLK),.oCLK(oCLK2));always @(a or posedge clkin)beginif(a==1)clkout=oCLK1;elseclkout=oCLK2;endendmodule//测试代码//testbenchmodule clk_div14bits_test;//-----------input-----------parameter WIDE=14;reg clk;reg[WIDE-1:0] div;//-----------output-----------wire oCLK;clk_div14bits cc3(.clk(clk),.a(a),.clkout(clkout)); always #20 clk = ~clk;initialbeginiCLK = 0;div=14'd7;#1000 $stop;EndModelsim仿真结果1.七分频2.四分频。

veriloghdl的原理 -回复

veriloghdl的原理-回复Verilog HDL(Hardware Description Language)是一种用于硬件描述和设计的编程语言。

它被广泛用于数字电路设计和验证,并在集成电路(IC)设计和电子系统设计中发挥着关键作用。

本文将详细介绍Verilog HDL的原理,包括其概念、工作原理和应用,就中括号内的内容进行逐步回答。

1. 什么是Verilog HDL?Verilog HDL是一种硬件描述语言,用于描述数字电路的结构、行为和功能。

它为硬件工程师提供了一种高级语言的方式来描述和设计硬件电路。

与低级语言如汇编语言相比,Verilog HDL具有更高的抽象层级,可以更容易地进行电路设计和验证。

2. Verilog HDL的起源和发展Verilog HDL最早于1984年由Gateway Design Automation公司的Phil Moorby提出,并在1985年开始商业化。

之后,它逐渐在硬件设计领域流行起来,并在1995年成为了IEEE标准(IEEE 1364-1995)。

此后,Verilog HDL经历了多次更新和改进,分别发布了Verilog-2001、SystemVerilog和最新的Verilog-2017版本。

3. Verilog HDL的设计层次结构Verilog HDL包括三个主要层次的描述:结构层次、行为层次和功能层次。

- 结构层次描述了电路的物理布局和组成,包括模块、端口、管脚和内部互连。

它类似于组成电路的黑盒子,忽略了内部的工作原理。

- 行为层次描述了电路的运行方式和时序。

它使用模块的输入和输出信号之间的顺序和时间关系来定义电路的行为。

- 功能层次提供了更高级别的抽象,描述了模块的功能和操作,而不是具体的实现细节。

在功能层次上,可以使用与C语言类似的语法和控制结构。

4. Verilog HDL的基本元素Verilog HDL包括了多种基本元素,用于描述电路的不同方面。

实验六Verilog设计分频器计数器电路

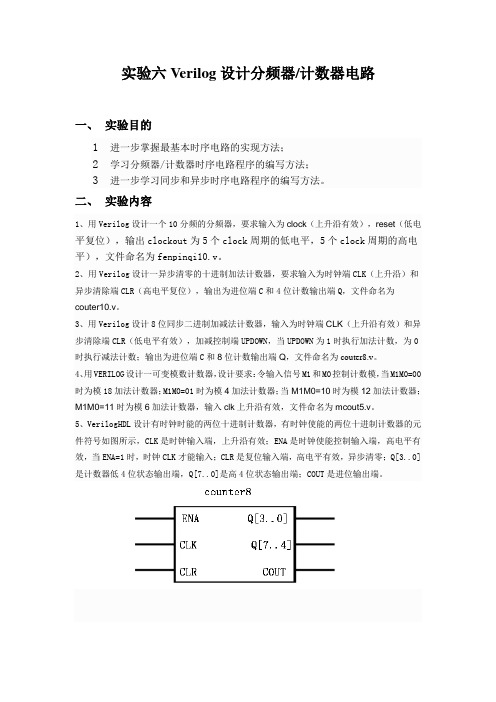

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

用Verilog语言实现奇数倍分频电路3分频5分频7分频

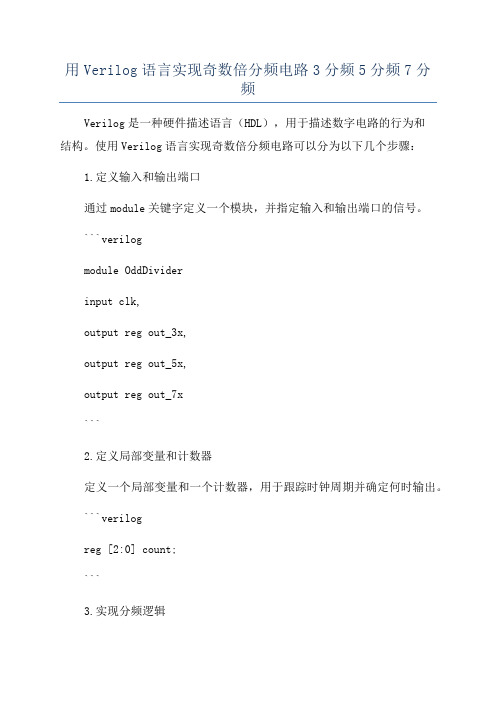

用Verilog语言实现奇数倍分频电路3分频5分频7分频Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

使用Verilog语言实现奇数倍分频电路可以分为以下几个步骤:1.定义输入和输出端口通过module关键字定义一个模块,并指定输入和输出端口的信号。

```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7x```2.定义局部变量和计数器定义一个局部变量和一个计数器,用于跟踪时钟周期并确定何时输出。

```verilogreg [2:0] count;```3.实现分频逻辑使用always块,根据计数器的值判断何时输出,并在输出端口上更新信号。

```verilogif (count == 3'b000) beginout_3x <= !out_3x;endif (count == 3'b001) beginout_5x <= !out_5x;endif (count == 3'b010) beginout_7x <= !out_7x;endcount <= count + 1;end```4.结束模块使用endmodule关键字结束模块定义。

```verilogendmodule完整的Verilog代码如下:```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7xreg [2:0] count;if (count == 3'b000) begin out_3x <= !out_3x;endif (count == 3'b001) begin out_5x <= !out_5x;endif (count == 3'b010) begin out_7x <= !out_7x;endcount <= count + 1;endmodule```以上代码实现了一个奇数倍分频电路,其中输入时钟信号为`clk`,输出分别是3倍分频的信号`out_3x`,5倍分频的信号`out_5x`和7倍分频的信号`out_7x`。

verilog hdl语言100例详解

verilog hdl语言100例详解Verilog HDL语言是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它是硬件设计工程师在数字电路设计中的重要工具。

本文将介绍100个例子,详细解释Verilog HDL语言的应用。

1. 基本门电路:Verilog HDL可以用于描述基本门电路,如与门、或门、非门等。

例如,下面是一个描述与门电路的Verilog HDL代码:```verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule```2. 多路选择器:Verilog HDL也可以用于描述多路选择器。

例如,下面是一个描述2:1多路选择器的Verilog HDL代码:```verilogmodule mux_2to1(input a, input b, input sel, output y);assign y = sel ? b : a;endmodule```3. 寄存器:Verilog HDL可以用于描述寄存器。

例如,下面是一个描述8位寄存器的Verilog HDL代码:```verilogmodule register_8bit(input [7:0] d, input clk, input reset, output reg [7:0] q);always @(posedge clk or posedge reset)if (reset)q <= 0;elseq <= d;endmodule```4. 计数器:Verilog HDL可以用于描述计数器。

例如,下面是一个描述8位计数器的Verilog HDL代码:```verilogmodule counter_8bit(input clk, input reset, output reg [7:0] count);always @(posedge clk or posedge reset)if (reset)count <= 0;elsecount <= count + 1;endmodule```5. 加法器:Verilog HDL可以用于描述加法器。

Verilog-HDL中的基本语法

一个完整的源程序都应当加上需要的注释, 以加强程序的可读性。

2.2 Verilog HDL的语法

2.2.1 空白符和注释

Verilog HDL的空白符包括空格、tab符号、换行 和换页。

空白符如果不是出现在字符串中,编译源程序 时将被忽略。

8. 条件操作符(Conditional operators)

条件操作符为:?:

条件操作符的操作数有3个,其使用格式为

操作数 = 条件 ? 表达式1:表达式2;

即当条件为真(条件结果值为1)时,操作数 = 表达式1;为假(条件结果值为0)时,操作数 = 表达 式2。

9. 位并接操作符(Concatenation operators) 并接操作符为:{} 并接操作符的使用格式: {操作数1的某些位,操作数2的某些位,…,操作数n 的某些位};

位运算操作符包括:~(按位取反)、&(按位与)、 |(按位或)、^(按位异或)、^~或~^(按位同或)。

在进行位运算时,当两个操作数的位宽不同时, 计算机会自动将两个操作数按右端对齐,位数少的操 作数会在高位用0补齐。

4. 关系操作符(Pelational operators)

关系操作符有:

<(小于)、<=(小于等于)、>(大于)、>=(大 于等于)。

② 每个模块首先要进行端口定义,并说明输入 (input)、输出(output)或双向(inouts),然 后对模块的功能进行逻辑描述。

③ Verilog HDL程序的书写格式自由,一行可以一 条或多条语句,一条语句也可以分为多行写。

④ 除了endmodule语句外,每条语句后必须要有 分号“;”。

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

Verilog语言实现5分频电路的设计

Verilog语言实现5分频电路的设计1.行为建模方法:使用行为建模方法,可以通过描述电路的功能行为来实现5分频电路。

以下是使用Verilog语言进行行为建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outreg [2:0] counter;counter <= 0;clk_out <= ~clk_out;end else begincounter <= counter + 1;endendendmodule```在该示例中,定义了一个模块`DivideBy5`,包含一个输入端口`clk`和一个输出端口`clk_out`,分别用于输入时钟信号和输出分频后的时钟信号。

`reg [2:0] counter`是一个3位的寄存器,用于计数。

当计数达到5时,即计数器的值为5,会将`counter`复位为0,并将输出时钟信号`clk_out`取反。

否则,计数器的值会自增12.结构建模方法:使用结构建模方法,可以通过组合和顺序电路的连接方式来实现5分频电路。

以下是使用Verilog语言进行结构建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outwire clk_out_2;wire clk_out_3;wire clk_out_4;DivideBy2 div_by_2 ( .clk(clk), .clk_out(clk_out_2) );DivideBy2 div_by_3 ( .clk(clk_out_2), .clk_out(clk_out_3) );DivideBy2 div_by_4 ( .clk(clk_out_3), .clk_out(clk_out_4) );DivideBy2 div_by_5 ( .clk(clk_out_4), .clk_out(clk_out) );endmodulemodule DivideBy2input wire clk,output wire clk_outreg clk_out;clk_out <= ~clk_out;endendmodule```在该示例中,定义了两个模块`DivideBy5`和`DivideBy2`。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

分频器的verilog HDL描述(转)

分频器,在许多涉及时序的电路设计中都会用到,在这里,我转载某位高人的文章,关于分频器的设计

偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

module odd_division(clk,rst,count,clk_odd);

input clk,rst;

output clk_odd;

output[3:0] count;

reg clk_odd;

reg[3:0] count;

parameter N = 6;

always @ (posedge clk)

if(! rst)

begin

count <= 1'b0;

clk_odd <= 1'b0;

end

else

if ( count < N/2-1)

begin

count <= count + 1'b1;

end

else

begin

clk_odd <= ~clk_odd;

end

endmodule

奇数倍分频:归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数从零开始,到(N-1)/2进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

再者同时进行下降沿触发的模N

计数,到和上升沿过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

module even_division(clk,rst,count1,count2,clk_even);

input clk,rst;

output[3:0] count1,count2;

output clk_even;

reg[3:0] count1,count2;

reg clkA,clkB;

wire clk_even;

parameter N = 5;

assign clk_re = ~clk;

assign clk_even = clkA | clkB;

always @(posedge clk)

if(! rst)

begin

count1 <= 1'b0;

clkA <= 1'b0;

end

else

begin

count1 <= count1 + 1'b1; if(count1 == (N - 1)/2)

begin

clkA <= ~clkA;

end

end

else

begin

clkA <= ~clkA;

count1 <= 1'b0;

end

always @ (posedge clk_re)

if(! rst)

begin

count2 <= 1'b0;

clkB <= 1'b0;

end

else

if(count2 < (N - 1))

begin

count2 <= count2 + 1'b1; if(count2 == (N - 1)/2)

begin

clkB <= ~clkB;

end

end

else

begin

clkB <= ~clkB; count2 <= 1'b0; end endmodule。