基于FPGA的1位LED设计-明德扬FPGA

明德扬科教的课程系列

明德扬科教的课程系列

1.FPGA在线培训课程

学费:159元

适合人群:适合零基础学生。

特点:通过大量案例来做练习,从而掌握FPGA设计。

通过本课程,可以独立进行FPGA的设计,足以胜任企业中的FPGA设计岗位。

2.FPGA开发板套餐

价格:288元

适合人群:零基础学生

特点:在线培训课程+开发板套餐

3.FPGA设计班

学费:1499元。

适合人群:零基础学生

特点:学习与在线培训课程相同的内容,但到明德扬现场培训,教师提供学习辅导和答疑服务。

通过本课程,可以独立进行FPGA的设计,足以胜任企业中的FPGA

设计岗位。

学习时间:全日学习约需一个半月(学生有空闲时间都可来公司培训)

4.FPGA就业班

学费:6700元,如已经完成了在线培训课程或FPGA设计班,学费减免1500元。

适合人群:零基础学生。

学习内容:在FPGA设计班的基础上,增加两个大型FPGA项目实践。

项目实践包括焊接电路、调试接口、系统方案设计、模块划分、模块设计、系统仿真和实现等

全过程,从而掌握整个项目的开发。

学习时间:约三至四个月。

保障:保障学会和就业,可一直培训到学会和就业。

一种基于FPGA的LED室内照明系统设计与实现

一种基于FPGA的LED室内照明系统设计与实现柴万东;张立萍【期刊名称】《内蒙古民族大学学报(自然科学版)》【年(卷),期】2016(031)002【摘要】针对LED光源在室内照明中的应用,设计了一种LED室内照明控制系统,该系统包括室内控制盒和模组控制器两部分.采用FPGA芯片Spartan-3E设计了室内控制盒硬件电路,并将模组控制器全部集成到XILINX公司的CoolRunner-II CPLD芯片中,用来接收DMX512协议上的调光数据,并将调光数据转化为PWM信号.LED驱动器接收PWM信号以便控制和调节LED光源亮度;利用SOPC开发工具EDK,搭建了基于32位嵌入式软核处理器的嵌入式系统,设计了室内控制盒的软件,最终实现了八种室内LED照明模式.%A set of indoor LED lighting control system for LED applications in indoor lighting is presented. The in-door LED lighting system include indoor control box and module controllers. A FPGA chip Spartan-3E is adapted to design the hardware circuit of indoor control box. The module controller is realized in a CoolRunner-II CPLD chip of Xilinx Company, which receives the brightness information from DMX512 protocol and output PWM signals. The LED driving chips receive PWM signals to control and adjust the LED lighting level. The SOPC Embedded Develop-ment Kit(EKD)is used to build the whole software system that is based on a 32-bit Microblaze soft processor. Final, 8 LED lighting patterns have been finished.【总页数】5页(P104-108)【作者】柴万东;张立萍【作者单位】赤峰学院物理与电子信息工程系,内蒙古赤峰 024000;赤峰学院物理与电子信息工程系,内蒙古赤峰 024000【正文语种】中文【中图分类】TM923【相关文献】1.基于Zigbee的室内LED智能照明系统 [J], 陈越2.基于物联网的LED室内照明系统设计趋势探讨 [J], 刘芳娇;王琦;胡海华3.基于物联网的LED室内照明系统设计趋势探讨 [J], 刘芳娇;王琦;胡海华4.基于WIFI的室内LED智能照明系统设计 [J], 周青山; 李建英; 郭晓华; 梁志鹏; 姜慧彬5.一种基于WiFi环境下的简易LED照明系统设计与实现 [J], 熊强强;李丽英;齐志艺;梁华;徐文磊;曾炜因版权原因,仅展示原文概要,查看原文内容请购买。

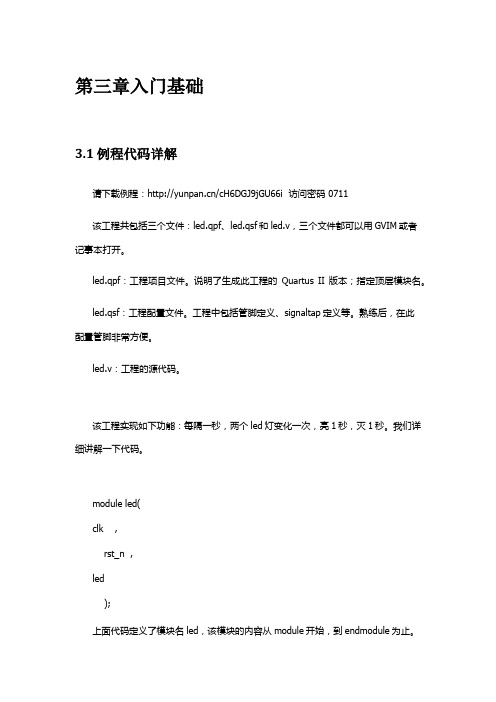

明德扬点拨FPGA高手进阶第三章入门基础 3.1 例程代码详解

第三章入门基础3.1 例程代码详解请下载例程:/cH6DGJ9jGU66i 访问密码 0711该工程共包括三个文件:led.qpf、led.qsf和led.v,三个文件都可以用GVIM或者记事本打开。

led.qpf:工程项目文件。

说明了生成此工程的Quartus II版本;指定顶层模块名。

led.qsf:工程配置文件。

工程中包括管脚定义、signaltap定义等。

熟练后,在此配置管脚非常方便。

led.v:工程的源代码。

该工程实现如下功能:每隔一秒,两个led灯变化一次,亮1秒,灭1秒。

我们详细讲解一下代码。

module led(clk ,rst_n ,led);上面代码定义了模块名led,该模块的内容从module开始,到endmodule为止。

该模块有三个输入输出信号,分别是clk、rst_n和led,是输入还是输出,分别是多少位宽(即多少根线)还未定义。

对于外界来说,看到的就是这三个信号,只需将这三个信号连接起来,就能使用这个模块的功能,至于内部是如何实现的、内部定义了什么信号,外界不关心。

input clk ;input rst_n ;output[1:0] led ;上面代码定义了信号的输入和输出,以及该信号的位宽。

例如,定义了clk和rst_n是输入的信号,并且每个位宽都是1位的,即只有一根线。

定义了led是输出信号,并且是2位的,即led信号有两根线。

输入信号即这个信号的激励,是由外部输入进来的;输出信号则是本模块根据功能,产生的信号。

reg [ 1:0] led ;reg [25:0] time_1s_cnt ;上面代码定义了led和time_1s_cnt的信号类型,声明他们是reg型的,并且表明led是2位宽,time_1s_cnt是26位宽(即有26根线)。

在设计代码中,一般只用到reg型和wire型。

reg型不一定就表示是寄存器。

到底是用reg型还是wire型,请记住一个原则:本module代码中,如果是在always 里产生的信号,都是用reg型,其他包括assign赋值、例化模块输出的信号都是用wire型。

基于FPGA的LED显示控制系统设计

基于FPGA的LED显示控制系统设计张志伟;赵峰【期刊名称】《科学技术与工程》【年(卷),期】2013(013)003【摘要】LED industry is the most promising high-tech industry in the 21st century, according to the structural characteristics of the LED display module, combining with FPGA technology.It designed a large-screen LED display control system.Display control system consists of input interface modules, signal write control module, the signal read control module, read control module, memory module and dynamic control modules, using Verilog-HDL language for programming, the design achieved a series of processing of the external input signal, including the address generation, selection, storage and dynamic control.The experimental results show that; the system can realize the dynamic display of character or pattern, has a practical application.%LED产业是21世纪最具有发展前景的高新技术产业.根据LED显示模块结构特点,应用FPGA技术对LED显示屏的控制系统进行设计.显示控制系统由输入接口模块、信号写入控制模块、信号读取控制模块、读取控制模块、存储模块、动态控制模块等模块构成.程序采用Verilog-HDL语言编写,从而实现外部输入信号的地址生成、选择、存储、动态控制等处理.实验测试结果表明:系统可以实现字符或图案的动态显示,具有实际应用价值.【总页数】4页(P753-756)【作者】张志伟;赵峰【作者单位】陕西理工学院物理与电信工程学院,汉中723000;陕西理工学院物理与电信工程学院,汉中723000【正文语种】中文【中图分类】TN873.5【相关文献】1.基于FPGA的LED全彩显示屏控制系统设计 [J], 李海富;熊本波;吴旭志2.基于FPGA的LED全彩显示屏控制系统设计 [J], 李海富;熊本波;吴旭志3.基于FPGA的LED显示屏控制系统设计 [J], 郭宝增;邓淳苗4.基于FPGA的高刷新率LED显示系统设计 [J], 耿迪;吴忠;张宇宁5.基于FPGA的LED电子显示屏系统设计 [J], 陆晶晶因版权原因,仅展示原文概要,查看原文内容请购买。

基础实验一、FPGA实现按键控制LED

7. 下载。 (1) 下载设置:如果第一次使用下载线下载配置文件到 FPGA,则需要在 QII 软件设 置下载线的型号等信息。先将 ByteBlasterII 下载线的一头接到 PC 的并口,执行菜单 Tools->Programmer(如下图)

Ñï¹âµç×Ó¹¤×÷ÊÒ

扬光电子工作室 qq:115513875 email:xiaoding113@

(5) 如果要下载到非易失 Flash 配置芯片(掉电后配置信息不丢失)里去,则将 ByteBlasterII 插到 EPCS1 芯片的下载口。并在下载界面的“Mode:”下拉列表应选择“Active Serial Programming”,并选择工程中.pof 后缀的文件进行下载。一般情况下使用 JTAG 下载 即可,等整个设计都完成了不需要再修改后才把最后的 POF 下载到 EPCS 芯片中。

Ñï¹âµç×Ó¹¤×÷ÊÒ

扬光电子工作室 qq:115513875 email:xiaoding113@

这里是选择其它 EDA 工具,对于该工程我们直接用 QuartusII 软件进行开发,因此不必 做修改,按 NEXT 进入工程的信息总缆对话框:

按 Finishi 按纽即建立一个空项目。 2、 建立顶层图

在工程目录下建立一个 name 为 Setup.tcl 的 file。File->New,选择 other files 页面:

Ñï¹âµç×Ó¹¤×÷ÊÒ

扬光电子工作室 qq:115513875 email:xiaoding113@

有关 tcl 文件的更详尽内容可参考 QuartusII 的帮助文档,对于我们所选用的 FPGA 开 发板 SOPC 开发板来说,由于不同型号的 FPGA 核心板的管脚与实验板上的引脚也不同, 因此不同的核心板对应的.tcl 文件也不同(关于核心板引脚与实验板引脚对应的详细情况请 学习套件用户手册”或相关电路原理图)。在实际项目中,该文件也可以根据具体管脚分配 要求来改写。

明德扬点拨FPGA高手进阶第三章入门基础 3.2 入门练习1

要求在代码详解工程的基础上修改:将 led 灯闪烁的个数由 2 个改为 3 个。

3.2.2 验收标准

按要求修改后பைடு நூலகம்上板验证,要求能看到三个 LED 灯闪烁。

3.2.3 练习答案

将两位 led 改为 3 位,需要改变如下几点:

1. 2. 3. led 输出声明的位宽:output[2:0] led; led 的信号类型的位宽:reg[2:0] led; 产生 led 信号的 always 中,所有位宽定义的。此处是复位时的语句改为:led <= 3’b00; 4. 在工程中配置 led[3]的管脚,可以配置成开发板上的 D1~D12。

以上文章出自明德扬点拨 FPGA 高手进阶,版权归明德扬所有,如需转载,请注明明德扬 谢谢!

基于SoC FPGA芯片的异步全彩LED显示控制器解决方案

基于SoC FPGA芯片的异步全彩LED显示控制器解决方案1 LED显示屏市场概况全彩LED显示被普遍应用于户外及室内的大型广告、舞台背景等场合(大多是同步显示),随着价格的下降,全彩LED显示已经开始被使用于门楣广告(异步显示)。

当前门楣广告一般采用单双色LED显示,市场需求大。

与单双LED相比,全彩LED 能够展现更丰富的内容,如真彩图片,动画,视频等,全彩LED显示将是门楣广告屏的发展趋势。

图1:中国LED显示屏产值(数据来源:GLII)2 市场流行方案的介绍目前市场上比较流行的方案有以下几种:1) ARM-CortexA8 + FPGA解决方案:图2:ARM-CortexA8 + FPGA方案框图特点:功能齐全,其中ARM Cortex-A8可以实现对主流视频格式的解码,但是方案成本偏高,对于门楣广告这种小屏显示的使用场景来说有些浪费。

2) ARM Cortex-M4解决方案:图3:ARM Cortex-M4方案框图特点:结构简单,但是由于没有使用FPGA,ARM Cortex-M4的实时性及速度无法满足全彩LED显示的控制要求,所以只能实现“七彩”显示,而不能实现真正意义上的全彩显示。

3) FPGA解决方案:图4:单FPGA方案框图特点:是同步全彩控制系统的一个衍生产品,实现简单的录制,功能相对单一。

3 京微雅格SoC FPGA方案京微雅格CME-M5系列FPGA集成了增强型8051 MCU,兼容标准8051指令集,12倍于标准8051的MIPS,频率最高可达200MHz,支持高达8MB数据及代码空间扩展,支持硬件32/16- bit MDU(Multiplication Division Unit),128K Byte SPRAM,可作为8051的代码或数据存储器,集成片上调试系统OCDS,支持JTAG 在线调试;外设有3个16-bit定时器,1个16-bit看门狗,1个I2C接口,1个SPI 接口,2个USART接口,1个RTC实时时钟,8通道DMA;支持STOP,IDLE电源管理模式。

明德扬点拨FPGA高手进阶第三章入门基础 3.3 入门练习2

3.3 入门练习23.3.1 练习要求要求在代码详解工程的基础上修改:将led灯闪烁的时间,由1秒改为2秒,其他保持不变。

3.3.2 验收标准按要求修改后,上板验证,2个led灯每两秒变化一次,亮2秒,灭2秒。

3.3.3 练习答案此处改变的是变化的时间。

首先原来程序是计算1秒时间,现在需要改为计算2秒;led变化的点,亦由原来的1秒,改为2位。

修改点如下:1.time_1s_cnt要计算2秒,因此其清0不再是49_999_999,而是变为99_999_999。

程序改为:always@(posedge clk or negedge rst_n)beginif(rst_n==1'b0)begintime_1s_cnt <= 0;endelse if(time_1s_cnt==99_999_999) begintime_1s_cnt <= 0;endelse begintime_1s_cnt <= time_1s_cnt + 1;endend2.time_1s_cnt要表示99_999_999,其位宽需要27位。

需要time_1s_cnt的类型声明改为: reg[26:0] time_1s_cnt;3.led改变时间点,改为2秒时间,其程序为:always@(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginled <= 2'b00;endelse if(time_1s_cnt==99_999_999)beginled<= ~led;endelse beginled<= led;endend以上文章出自明德扬点拨FPGA高手进阶,版权归明德扬所有,如需转载,请注明明德扬谢谢!。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1位闪烁灯设计1项目背景LED(Light Emitting Diode),发光二极管,是一种能够将电能转化为可见光的固态的半导体器件,它可以直接把电转化为光。

LED的心脏是一个半导体的晶片,晶片的一端附在一个支架上,一端是负极,另一端连接电源的正极,使整个晶片被环氧树脂封装起来。

半导体晶片由两部分组成,一部分是P型半导体,在它里面空穴占主导地位,另一端是N型半导体,在这边主要是电子。

但这两种半导体连接起来的时候,它们之间就形成一个P-N结。

当电流通过导线作用于这个晶片的时候,电子就会被推向P区,在P区里电子跟空穴复合,然后就会以光子的形式发出能量,这就是LED灯发光的原理。

而光的波长也就是光的颜色,是由形成P-N结的材料决定的。

LED可以直接发出红、黄、蓝、绿、青、橙、紫、白色的光。

最初LED用作仪器仪表的指示光源,后来各种光色的LED在交通信号灯和大面积显示屏中得到了广泛应用,产生了很好的经济效益和社会效益。

以12英寸的红色交通信号灯为例,在美国本来是采用长寿命,低光视效能的140瓦白炽灯作为光源,它产生2000流明的白光。

经红色滤光片后,光损失90%,只剩下200流明的红光。

而在新设计的灯中,Lumileds公司采用了18个红色LED光源,包括电路损失在内,共耗电14瓦,即可产生同样的光效。

汽车信号灯也是LED光源应用的重要领域。

对于一般照明而言,人们更需要白色的光源。

1998年发白光的LED开发成功。

这种LED是将GaN芯片和钇铝石榴石(YAG)封装在一起做成。

GaN芯片发蓝光(λp=465nm,Wd=30nm),高温烧结制成的含Ce3+的YAG荧光粉受此蓝光激发后发出黄色光射,峰值550nLED灯m。

蓝光LE D基片安装在碗形反射腔中,覆盖以混有YAG的树脂薄层,约200-500nm。

LED基片发出的蓝光部分被荧光粉吸收,另一部分蓝光与荧光粉发出的黄光混合,可以得到白光。

对于InGaN/YAG白色LED,通过改变YAG荧光粉的化学组成和调节荧光粉层的厚度,可以获得色温3500-10000K的各色白光。

这种通过蓝光LED得到白光的方法,构造简单、成本低廉、技术成熟度高,因此运用最多。

明德扬的教学板一共有8个可发绿光的LED灯。

下面是LED灯的原理图。

图130LED原理图左边的LED1~LED8是板子上LED灯的丝印。

右边的LED1~LED8_NET是信号线名,读者在板子上是看不到这些信号线的。

LED灯一端连着高电平3.3V,另一端是信号线LED1~LED8_NET。

如果LED1~LED8_NET是高电平,则电流不导通,那么LED灯则不会发光。

如果LED1~LED8_NET是低电平,则电流会导通,那么LED灯就发光。

所以LED灯发光与否,取决于信号LED1~LED8_NET处于什么电平。

信号线LED1~LED8_NET又连到哪里呢?搜索下原理图文档,可以发现这些信号是连到FPGA的管脚上的。

下面信号线和FPGA管脚的连接图,例如信号线LED1是连接到FPGA的AA4管脚上。

教学板丝印信号线FPGA管脚LED1LED1_NET AA4LED2LED2_NET AB4LED3LED3_NET AA5LED4LED4_NET AB6LED5LED5_NET AA10LED6LED6_NET AB13LED7LED7_NET AB14LED8LED8_NET AB16LED1~LED8_NET分别与FPGA的8个管脚相连,所以LED1~LED8_NET处于什么电平,即LED灯是否要发光,就取决于FPGA管脚的输出了。

例如FPGA管脚AB14连到LED7上。

要控制这个灯的亮灭,FPGA只需要将管脚AB14输出为低高就可以了。

当输出为高电平时,LED7灯为灭,当输出为低电平时,LED7灯为暗。

8个LED 灯都可由FPGA独立控制。

2设计目标本工程使用1个LED灯---LED1,实现一个闪烁灯的功能。

工程的工作时钟是50M,也就是时钟周期为20ns。

当管脚AA4输出低电平时,LED1灯亮,输出高电平时,LED1灯灭。

具体功能要求是:隔1秒,亮N秒。

N的变化是:1,2,3,---,9秒,然后再次循环。

下面是波形图:图132上板效果图如下图所示。

图1333设计实现2.1顶层信号新建目录:D:\mdy_book\my_led 。

在该目录中,新建一个名为my_led.v 的文件,并用GVIM 打开,开始编写代码。

我们先分析一下板子上的LED 灯。

要控制1个LED 灯亮和灭,那就FPGA 需要产生一个信号,假定为led ,这个信号连接到led 灯上。

要让LED 灯灭,FPGA 将信号led 输出为1;要让LED 灯亮,FPGA 将信号led 输出为0。

下面表格表示了硬件电路图的连接关系。

器件原理图信号FPGA 管脚FPGA 工程信号LED1LED1_NET AA4led X1SYS_CLK G1clk K1SYS_RSTAB12rst_n综上所述,我们这个工程需要三个信号,时钟clk ,复位rst_n 和输出信号led。

将module 的名称定义为my_led ,为此,代码如下:其中clk 、rst_n 是输入信号,led 是输出信号,并且三个信号都是1比特的,根据这些信息,我们补充输入输出端口定义。

代码如下:2.2信号设计我们再分析一下功能需求,LED 灯的变化规律是暗1秒,亮N 秒,其中N 的变化是:1,2,3,---,9秒,然后再次循环。

从现象转化成信号,其实就是信号led=1持续1秒,然后led=0持续N 秒,其中N 的变化是:1,2,3,---,9秒。

波形示意图如下:图134上图就是led 信号的变化波形图。

在第1次时,led=1并持续1秒,然后led=0并持续1秒,共2秒时间;在第2次时,led=1并持续1秒,然后led=0并持续2秒,共3秒时间;以此类推,第9次时,led=1并持续1秒,然后led=0并持续9秒,共10秒时间。

然后又再次重复。

由波形图可知,我们需要1个计数器用来计算时间,如2秒、3秒等。

本工程的工作时钟是50MHz ,即周期为20ns ,计数器计数到2_000_000_000/20=100_000_000个,我们就能知道2秒时间到了。

以此类推,在第2次时,数到150_000_000个,就知道了3秒时间到。

第9次时,数到500_000_000个,就表示10秒时间到。

另外,由于该计数器是不停地计数,永远不停止的,可以认为加1条件一直有效,可写成:assign add_cnt==1。

综上所述,结合变量法,该计数器的代码如下。

其中x表示该计数器cnt0要数的个数。

该值如何定义,后面再思考。

再次观察波形图,我们发现有第1次,第2次直到第9次的字,说明这还需要另外一个计数器来表示第几次。

该计数器表示次数,自然是一次完成了就加1,因为加1条件可为end_cnt0。

该计数器一共要数9次。

所以代码为:有了两个计数器,我们来思考输出信号led的变化。

概括起来,led有两种变化点:变0和变1。

变0的原因都是计数到1秒时间,也就是cnt0数到1_000_000_000/20=50_000_000个时,led变0。

变1的原因,都是计数时间到了,即end_cnt0。

所以led信号的代码如下:最后我们再来思考变量x,我们在讨论计数器cnt0的时候,曾经说过“计数器计数到2_000_0 00_000/20=100_000_000个,我们就能知道2秒时间到了。

以类类推,在第2次时,数到150_000 _000个,就知道了3秒时间到。

第9次时,数到500_000_000个,就表示10秒时间到。

”可以看到,cnt0要数多少个是跟第几次有关系的。

第1次,数100_000_000个,第2次数150_000_000个。

也就是与cnt1有关。

因此x的代码如下:此次,主体程序已经完成。

接下来是将module补充完整。

2.3信号定义接下来定义信号类型。

cnt0是用always产生的信号,因此类型为reg。

cnt0计数的最大值为500_000_000,需要用2 9根线表示,即位宽是29位。

因此代码如下:个线表示即可。

因此代码如下:即位宽是4位。

因此代码如下:根线表示即可。

因此代码如下:码如下:x是用always方式设计的,因此类型为reg。

并且其值是最大是500_000_000,需要29根线表示即可。

因此代码如下:至此,整个代码的设计工作已经完成。

下一步是新建工程和上板查看现象。

3综合与上板3.1新建工程首先在d盘中创建名为“my_led”的工程文件夹,将写的代码命名为“my_led.v”,顶层模块名为“my_led”。

图135然后打开QuartusⅡ,点击File下拉列表中的New Project Wzard...新建工程选项。

3.再出现的界面中直接点击Next。

图1384.之后出现的是工程文件夹、工程名、顶层模块名设置界面。

按照之前的命名进行填写,然后点击Next,在出现的界面再点击next。

图139图1405.之后是文件添加界面。

添加之前写的“my_led.v”文件,点击右侧的“Add”按钮,之后文件会在下方显示出来,之后点击“Next”。

图141器件型号选择界面。

选择CycloneⅣE,在芯片型号选择处选择EP4CE15F23C8,然后点击“Next”。

EDA工具界面。

直接点击“Next”。

8.之后出现的界面,点击“Finish”。

图1443.2综合1.新建工程步骤完成后,就会出现以下界面。

选中要编译的文件,点击编译按钮。

图1452.编译成功后会出现一下界面。

3.3配置管脚在菜单栏中,选中Assignments,然后选择Pin Planner,就会弹出配置管脚的窗口。

图148在配置窗口最下方中的location一列,参考下表中最右两列配置好FPGA管脚。

器件原理图信号FPGA管脚FPGA工程信号LED1LED1_NET AA4ledX1SYS_CLK G1clkK1SYS_RST AB12rst_n配置完成后,关闭Pin Planner,软件自动会保存管脚配置信息。

3.4再次综合在菜单栏中,选中Processing,然后选择Start Compilation,再次对整个工程进行编译和综合。

图150出现上面的界面,就说明编译综合成功。

3.5连接开发板图中,下载器接入电脑USB接口,电源接入电源,然后摁下下方蓝色开关。

图1513.6上板1.单击以下界面中的。

2.会出现如下界面,点击add file添加.sof文件,点击“Start”,会在“Progress”出显示进度。

图1533.进度条中提示成功后,即可在开发板上观察到相应的现象。

源码在技术交流群:97925396。