数字逻辑3-3n

数电逻辑16个公式

数电逻辑16个公式

数电逻辑是一种处理数字信号的技术,包含16个公式,其中最常用的是:

1. 加法:即同或或异或

2. 乘法:即与或或与非

3. 异或加法:即xor和or

4. 与或乘法:即AND和OR

5. 异或乘法:即XOR和AND

6. 异或加法和异或乘法:即xor和and

7. 与或加法和与或乘法:即or和and

8. 与或加法和异或加法:即or和xor

9. 与或乘法和异或乘法:即AND和XOR

10. 与或加法和与或乘法:即OR和AND

11. 异或加法和异或乘法:即xor和AND

12. 与或加法和与或乘法:即OR和AND

13. 与或加法和异或加法:即OR和xor

14. 与或乘法和异或乘法:即AND和XOR

15. 异或加法和与或加法:即xor和OR

16. 与或加法和异或加法:即OR和xor。

数字逻辑基础知识

例4 解

(427)D=( ? )H 16 427 16 26………… 余数 11=B 最低位

16 1……………10=A 0……………1=1 即 (427)D=(1AB)H 最高位

例5 解

(427)D=( ? )O 8 427 8 53………… 余数 3 最低位

8 6……………5 0……………6 即 (427)D=(653)O 最高位

2. 二进制数转换成八进制数或十六进制数 二进制数转换成八进制数或十六进制数

二进制数转换成八进制数(或十六进制数)时,其整数 部分和小数部分可以同时进行转换。其方法是:以二进 制数的小数点为起点,分别向左、向右,每三位(或四位) 分一组。对于小数部分,最低位一组不足三位(或四位)时, 必须在有效位右边补0,使其足位。然后,把每一组二进 制数转换成八进制(或十六进制)数,并保持原排序。对于 整数部分,最高位一组不足位时,可在有效位的左边补0, 也可不补。

某个数位上的数码Xi所表示的数值等于数码Xi与该位 的权值Ri的乘积。所以,R进制的数

( N ) R = X n −1 X n − 2 ... X 2 X 1 X 0 . X −1 X − 2 ... X − m

按权展开,又可以写成如下多项式的形式:

( N ) R = X n −1 R =

n −1

2. 十六进制 十六进制 在十六进制中,每个数位上规定使用的数码符号为0,1, 2,…, 9, A, B, C, D, E, F,共16个,故其进位基数 R=16。其计数规则是“逢十六进一”。各位的权值为16i, i 是各个数位的序号。 十六进制数用下标“H”或“16”表示。 在计算机应用系统中,二进制主要用于机器内部的数据 处理,八进制和十六进制主要用于书写程序,十进制主要 用于运算最终结果的输出。

数字逻辑与应用要点精华公式

数字逻辑与应用要点第一章数字概念与数制系统1.1-1.6数字与模拟(了解)1、数字量与模拟量:离散、有限;连续、无限2、数字系统的问题定义:输入/输出变量,映射函数(成员函数)3、数字系统分级:元件级、SSI、MSI(LSI)、VLSI1.7-1.8数位系统(重点)1、任意进制(r)数的多项式表示2、熟练10进制,2进制,8进制,16进制以及它们之间的相互转换3、转换方法:除基取余、乘基取整、多项式求和十进制整数转二进制P12:例1-12十进制小数转二进制P13:例1-14的第二步(每次乘二,取整数)二进制转十六进制P10:1.8.1(二进制从最后一位依次向前取四位不够添0,把每四位转化为十进制,10-15的分别为A、B、C、D、F)二进制转八进制P10:1.8.2(二进制从最后一位依次向前取三位不够添0,把每三位转化为十进制)十进制转十六进制、八进制,可短除可转二进制。

各进制之间的转换计算。

P34:13、14、15、17、18、191.9二进制编码(部分重点)1、BCD码:8421、5421、余3码,自补码特性2、算术补码:基数补码、基数减1补码,适用任意进制数;逻辑补码与二进制减1补码3、间隔位编码:GRAY码4、字符编码:ASCII码(7位),EBCDIC码(8位)5、符号数编码:原码、反码、补码十进制转BCD码P16:例1-19(就是简单的把每个位上的数字转化二进制)余3码就是把十进制加3再转BCD码带符号数量编码P20:表1-11(带符号数就是先把十进制转化二进制,正数前面添0,负数添1。

以1为基的补码就是反码,正数就是符号数,负数符号位不变,后面取反。

以2为基的补码就是补码,正数就是符号数,负数符号位不变,后面取反加一)以1为基、2为基等补码计算。

P35:30、311.10运算二进制(带符号)数的加减运算正数加法P23:例1-25正数减法P24:例1-28正数乘法P24:例1-29正数除法P24:例1-30带符号使用补码计算P25:1.10.2算数运算。

数字逻辑基础总复习三

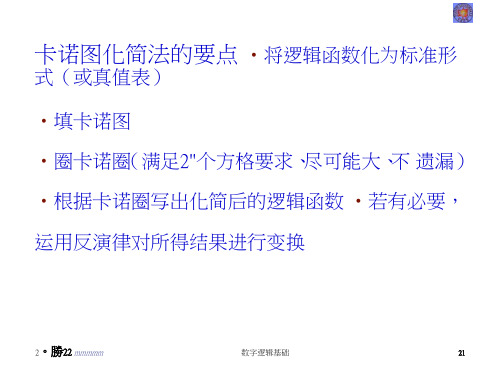

卡诺图化简法的要点•将逻辑函数化为标准形式(或真值表)•填卡诺图•圈卡诺圈(满足2"个方格要求、尽可能大、不遗漏)•根据卡诺圈写出化简后的逻辑函数•若有必要,运用反演律对所得结果进行变换2011-06-22 ■HBV纒雾.... ..tipi' T / ~W -WR -'数字逻辑基础22利用卡诺图运算来进行逻辑化简逻辑函数—卡诺图逻辑函数的运算—卡诺图的运算卡诺图的运算—对应的方格进行运算证明(以“与”运算为例):设/=Z%A=Z^W,则有f-f2=Z^1i m i*Z a2=Z(a U*a2i)m i+Z*a2i)m i m j=Z(a U,a2i Mi i^j i 证明的最后一步运用了最小项的性质2不完全确定的逻辑函数的化简不完全确定的逻辑函数:由打个逻辑变量构成的逻辑函数中,有效的逻辑状态数小于2〃个。

那些无效的状态或者是不可能出现,或者无意义。

这些无效的状态被称为任意项,或称为无关项、约束项、禁止项,等等使用异或函数的卡诺图化简异或运算的性质:d㊉5 = 5㊉d ㊉5)㊉C = ^㊉㊉C) = ^㊉5㊉Cd e o = d, d㊉ i=d d㊉d=0,d㊉d=id㊉5 = d㊉5 = d㊉5lipt T rn多输出逻辑函数的化简•考虑公共蕴涵的使用•公共蕴涵也是越大越好•有时在寻找公共蕴涵过程中会有多种可能的方案出现,这时要根据实际情况作一定的取舍,部分地要依赖于人为的经验影射变量卡诺图化简•在影射变量卡诺图的每个方格中,不但可以包含0, 1和任意项,还可以包含变量和函数(代入定理)。

第2章组合逻辑电路本章要求>掌握组合逻辑电路的基本分析方法和一般设计过程>掌握常见逻辑模块的功能及其使用>掌握实际逻辑电路中冒险现象的形成原理及其防止方法一般分析过程•确定电路结构为组合电路•逐级分析,或划分模块后分析。

得到逻辑表达式或真值表•分析得到的逻辑表达式或真值表,得出电路的功能描述常用组合逻辑模块•组合逻辑模块是一些基本的逻辑单元•熟悉组合逻辑模块的结构与功能,可以帮助分析复杂的逻辑结构•在设计逻辑电路时,可以从逻辑模块出发进行设计。

数字逻辑电路3

第一章

逻辑代数基础

四、逻辑函数及其表示方法 1、逻辑函数

3、函数表达式的常用形式

•最小项

•最小项表达式 •最大项 •最大项表达式

21

3、常见逻辑函数式

1、最小项

设A、B、C是三个逻辑变量,若由这三个逻辑变量按以下

规则构成乘积项: ①每个乘积项都只含三个因子,且每个变量都是它的一个 因子; ②每个变量都以反变量(A、B、C)或以原变量(A、B、C)的

例: F m1 m3 m5 m7 解: F m0 m2 m4 m6

F m0 m2 m4 m6 m0 m2 m4 m6

M0 M 2 M4 M6

: Mi mi

最小项与最大项的关系 相同编号的最小项和最大项存在互补关系

2

例: F(A、B、C) AB (A C) B A B C

F (A B) A C B (A B C)

或 其反函数为

注:

F (A B) (A C) B (A B C)

① 运用反演规则时,要注意保持原函数的运算次序—(先括号、 再相与,最后或) ,必要时可加或减扩号。 ② 不属于单个变量上的非号有两种处理方法 非号保留,而非号下面的函数式按反演规则变换 将非号去掉,而非号下的函数式保留不变

3、 最大项

n 个变量的逻辑函数中,M为n 个变量之和,每个变量 最大项: 必须而且只能以原变量或反变量的形式出现一次,称

M为该组变量的最大项。 n个变量有2n个最大项,记作i

最大项的性质:

任意一组变量取值,只有一个最大 项的值为0,其它最大 项的值均为1

同一组变量取值任意两个不同最大项的和为1。即Mi+Mj=1

3位移位寄存器的真值表

3位移位寄存器的真值表概述:移位寄存器是一种常见的数字逻辑电路,用于在数字系统中将数据向左或向右移动指定的位数。

3位移位寄存器是其中一种类型,它能存储和操作3位二进制数据。

本文将围绕3位移位寄存器的真值表展开讨论,详细解释其工作原理和应用场景。

真值表的定义和构成:真值表是用来描述逻辑函数的一种常见形式,其中每一行代表了逻辑变量的所有可能组合及其对应的函数输出。

对于3位移位寄存器,其真值表将包含8行(2^3=8)。

下面是3位移位寄存器的真值表:输入(A, B, C)输出(Q0, Q1, Q2)0 0 0 0 0 00 0 1 0 0 00 1 0 0 0 10 1 1 0 1 01 0 0 1 0 01 0 1 0 1 11 1 0 1 1 01 1 1 1 1 1解读真值表:在3位移位寄存器的真值表中,输入部分由3个变量(A, B, C)组成,每一行代表了一种输入组合。

输出部分由3个变量(Q0, Q1, Q2)组成,对应着每一种输入组合下的输出结果。

其中,输入变量(A, B, C)表示了要移位的原始数据。

输出变量(Q0, Q1, Q2)则表示了移位后的数据。

工作原理:3位移位寄存器的工作原理可以通过真值表来解释。

在移位寄存器中,数据可以向左或向右移动指定的位数。

当输入变量(A, B, C)的值发生变化时,输出变量(Q0, Q1, Q2)会根据移位规则进行更新。

根据真值表的结果,我们可以总结出3位移位寄存器的移位规则:- 当输入变量为(0 0 0)时,输出变量为(0 0 0),表示没有移位发生。

- 当输入变量为(0 0 1)时,输出变量为(0 0 0),表示向右移动1位。

- 当输入变量为(0 1 0)时,输出变量为(0 0 1),表示向右移动2位。

- 当输入变量为(0 1 1)时,输出变量为(0 1 0),表示向右移动3位。

- 当输入变量为(1 0 0)时,输出变量为(1 0 0),表示没有移位发生。

数字逻辑题库

莈`0001 01A1十进制数(12.5)D转化为二进制数是______________,对应的十六进制数是___________。

薆~00011100.1 C.1芁`0002 01A1十进制数(23.75)D转化为二进制数是______________,对应的十六进制数是___________。

螃~000210111.11 17.C螀`0003 01A1 (39)10=( )2 ;(87)10=( )8421BCD羆~0003100111 10000111肂`0004 01A1十进制数35转换成二进制数是____________;十六进制数是____________。

薀~0004100011 23袈`0005 01A1用8421码表示的十进制数65,可以写成_________。

蒅~000501100101螂`0006 01A1十进制数(33)D转化为二进制数是______________,对应的十六进制数是___________。

蚁~0006100001 21羇`0007 01A1(66)10=( )2 ;(68)10=( )8421BCD袄~00071000010 01101000薂`0008 02A1逻辑代数中最基本的三种逻辑运算是_________、_________和__________。

蚃~0008 与、或、非荿`0009 04A1含用触发器的数字电路属于(组合逻辑电路、时序逻辑电路)。

芄~0009 时序逻辑电路芃`0010 02A1AB +A 在四变量卡诺图中有个小格是“1”。

~0010 8`0011 03A1七段码显示器有共阴极和共阳极两种接法,若a-g各段输入0010010时,显示2的字形,则其采用共______极接法。

~0011阳`0012 03A1一个16选1数据选择器,应具有 ____ 个选择输入端(地址输入端) ____ 个数据输入端。

~00124 16`0013 04A1JK触发器的特性方程是_____________________________。

数字逻辑第三章,英文

Get Truth Table or Logic Function

Draw Logic Circuit

Emphasis

Using Logic IC Module

3

4.1 Switching Algebra

Boolean Algebra (1854) 1.Axioms Positive-Logic Negative-Logic 1-High 0-High

0⋅0 = 0

0+0 = 0 0⋅1=1⋅0=0 1+ 0 = 0 +1 = 1

5

1 ⋅1 = 1

1+1 = 1

2.Theorems (T1) Identities

X +0= X

(T2) Null elements

X ⋅1 = X

Single-Variable Theorems Variable Theor = X ⋅ Y + X ⋅ Z

(X +Covering + Z) Y)(X′ + Z)(Y (T10) = (X + X′⋅ ⋅Y X + Z X ⋅YXY+ X⋅Z′+=′XZ +Y ⋅Y′)(Y +Z + X ⋅ X′) + +Z Z )(Y ⋅

= ( X ⋅+ Y ) ⋅ (X ′′+ Z) ⋅ (Y + Z ) = ( X + Y ) ⋅ ( X ′ + Z ) X Y + X ⋅Z = ( X + Y + Z)(X + Y + Z ) (T12) DeMorgan’s ′⋅ A ⋅ B = X ⋅ Y + X ′ ⋅ Z X ⋅ Y +′ X ′ ⋅ Z +′Y ⋅ Z ′

3-3 时序逻辑电路

J K Qn+1

0 0 Qn 01 0 10 1 11

Hale Waihona Puke 功能说 明不变 置0 置1 翻转

电路符号图

真值表

J-K触发器的次态方程为

Qn

触发器

• T触发器:又称为计数触发器。

T Qn+1 功能 说明

0 Qn 不变 1 Qn 翻转

电路符号图

T触发器的次态方程为

真值表

寄存器

触发器

• 一个触发器可以存储一位二进制信息。 • 触发器应具备三个基本特点:

– ⑴ 有互补的输出端Q和Q。 – ⑵ 具有两个能够自行保持的稳定状态。 – ⑶ 在输入信号的作用下,触发器可以从一种

状态翻转到另一种状态。

触发器

• R-S触发器:最基本的触发器。

反馈

Q

Q

Q

Q 两个输出端

Q

&

&

a

b

Q

Q

R

0 1 0 10 1 0 1

0 01 10 010 101 0101 1010 0101 101

并行输入-串行输出(并-串转换) 数据拆卸

101

010 101 0101 101 011 110 10 11

0 1 0 10 1 0 1

计数器

计数器的基本功能就是用来累计输入 脉冲的个数。计数器不仅可以用来计数, 也可用来定时、分频等。

时序逻辑电路

时序逻辑电路

所谓时序逻辑电路,是指此电路任一 时刻的输出不仅与该时刻的输入有关,而 且还与该时刻电路的状态(现态)有关。

基本的时序逻辑电路包括寄存器、暂 存器、移位寄存器、计数器等。

数字逻辑课件——常用组合逻辑电路

图3-3-3 BCD输出的10线- 4线优先编码器74147 14

表3-3-4

BCD输出的10线-4线优先编码器74147的功能表

I I 1 2 YI 1835967241023

I3 I4 I5 I6 I7

I8 I9 Y3 Y2 Y1 Y0

H HH H H H HH H HH H H

L LHH L

Y 3 I8 I9

Y 2 I7 I8 I9 I6 I8 I9 I5 I8 I9 I4 I 8 I 9

Y1 I7 I8 I9 I6 I 8 I 9 I3 I 4 I 5 I 8 I 9 I2 I 4 I 5 I 8 I 9

输出 Y 0 的表达式为

Y 0 I9 I7 I 8 I 9 I5 I 6 I 8 I 9 I3 I 4 I 6 I 8 I 9 I1 I 2 I 4 I 6 I 8 I 9

在8线-3线编码器中,在某一时刻,编码器输入I0~I7中只允 许有一个为 1,否则将使编码输出Y0~Y2发生混乱。为解决

这一问题,一般都把编码器设计成优先编码器(Priority Encoder)。

4

在优先编码器中,允许同时有一个以上输入端输 入为1(即有效信号), 因为在设计优先编码器时,预先对所有编码输入 按优先顺序排了队,故当几个编码输入同时为1 时,只对其中优先级最高的一个输入进行编码。 图3-3-2给出了8线-3线优先编码器74148的逻辑 符号和逻辑图,其功能表见表3-3-2。

5421码 0011 1001 1100

2421码 余3码

0011 1100 1111 0110 1001 1100

12

二 — 十进制优先编码器74147 74147是8421 BCD码优先编码器,或称BCD输 出的10线 — 4线优先编码器,其逻辑符号和 逻辑图见图3-3-3所示,功能表见表3-3-4所 示,