集成电路版图设计基础第八章:噪声问题

集成电路信号噪声优化研究

集成电路信号噪声优化研究随着科技的不断发展,集成电路的应用越来越广泛,涉及到了众多的领域,如通信、计算机、医疗、军事等。

而集成电路信号的稳定性和可靠性则是保障这些应用能否成功实现的关键因素之一。

因此,如何优化集成电路信号中的噪声成为了研究的热点和难点。

一、认识集成电路信号噪声集成电路是一种由数百万个电子器件、电路元件和连接线引线组成的微型电子系统。

它的信号通常是微弱的,经过一系列放大、处理、传输的过程后才能被解码和使用。

然而,相应的问题就是随之而来的噪声,噪声是由一定随机分布的因素所产生的,如热噪声、量子噪声和杂散噪声等。

热噪声主要来源于芯片本身的热运动,特别是在高温环境下,噪声会不断变大。

可以通过降温、降低电阻等措施来减少噪声产生。

量子噪声是在微观粒子的尺度上产生的,它的特点是高度频繁、强烈,并且难以避免。

杂散噪声多半由外界环境干扰引起,如电磁波干扰和磁性干扰等。

这种噪声多为高频噪声,可通过隔离屏蔽、接地等方式来降低。

二、集成电路信号噪声的影响在集成电路中,噪声的存在会对电路的稳定性、可靠性和精度造成影响。

噪声越大,信噪比也就越小,电路的有效信号也就越难以提取。

同时,噪声会引起误差,导致传输数据的不准确,这对某些领域来说可能是致命的。

在数字信号中,噪声可导致误码率(BER)增加。

在模拟电路中,噪声会影响电路的精度和稳定性,甚至会引起电路振荡或失真,从而严重影响集成电路的正常使用。

三、集成电路信号噪声的优化方法在集成电路设计中,为了保证信号的稳定性和精度,在衰减和滤波技术方面,成为了集成电路噪声优化的主要方法。

其中,集成电路抗噪声设计的多通道技术,是一种通过平均、滤波等方式抑制噪声的技术。

多通道技术通过将信号分成多个频带进行处理,然后进行加权平均,从而大大降低了噪声的影响。

这种技术能够在电路噪音较大的情况下保持信号的稳定性和准确性。

同时,模拟信号滤波技术也是保证集成电路信号稳定性的主要手段。

模拟信号滤波技术分无源滤波和有源滤波两种。

集成电路设计中的电源噪声解决方案研究

集成电路设计中的电源噪声解决方案研究近年来,随着集成电路设计的不断进步,噪声问题已经成为了制约集成电路性能发挥的重要因素之一。

而在集成电路设计中,电源噪声的问题尤其突出。

因此,为了提高集成电路的性能和可靠性,研究电源噪声的解决方案是非常必要和重要的。

一、电源噪声的研究意义集成电路作为现代电子技术的核心,已经广泛应用于通信、计算机、智能家居、工业自动化等众多领域。

但是,电源噪声问题也成为了制约集成电路性能发挥的重要因素之一,因为电源噪声会直接影响集成电路功能的实现及其稳定性。

电源噪声主要是指电源线路中存在的无用信号或干扰信号,它们会与有用的电路信号混合,产生干扰、抖动、误码等问题,导致集成电路的工作不稳定。

因此,研究电源噪声的解决方案是提高集成电路性能和可靠性的一个重要手段。

二、电源噪声对集成电路的影响电源噪声主要影响集成电路的两个方面:1. 抖动和噪声电源噪声会直接导致抖动和噪声问题,使得集成电路工作不稳定,而这种抖动和噪声会导致集成电路的性能变差。

例如,当噪声信号中的高频噪声达到一定的级别时,可能会导致电路震荡,甚至崩溃。

2. 误码率电源噪声也会产生误码问题。

当误码率超过一定限制时,将会影响到通信的可靠性。

这种情形被广泛应用于通信、计算机等系统中。

三、电源噪声的解决方案为了解决集成电路中电源噪声问题,需要采取以下措施:1. 设计干净的电源线路要减少电源噪声,首先要限制电流的峰值和尽量减少共模电压的干扰。

为此,可以设计电源线路,从而减少各种噪声,如方波噪声、直流偏压、功率谐波、噪声控制带宽内的频率滤波器等等。

2. 采用适当的滤波器滤波器是一种常见的处理电源噪声的方法。

它们可以抑制电源线路中的噪声和干扰信号,防止它们进入到集成电路中,从而减少抖动和噪声问题,提高集成电路的可靠性。

3. 使用耦合器耦合器是一种处理电源噪声的重要方法。

它们可以将电源线路和集成电路进行耦合,降低电源噪声。

例如,在设计中可以使用小型的陶瓷电容器和小型的铝和钽电容器,以减少各种噪声,提高集成电路稳定性。

集成电路中电源噪声的建模与分析

集成电路中电源噪声的建模与分析集成电路,这玩意儿在咱们如今的生活里可太重要啦!从手机到电脑,从电视到汽车,哪儿都离不开它。

今天咱们就来聊聊集成电路中一个让人头疼但又特别关键的问题——电源噪声。

先跟大家分享一件我曾经碰到的事儿。

有一次,我在实验室里捣鼓一个新的集成电路项目。

一切似乎都进展得挺顺利,可就是在测试的时候,总觉得哪里不太对劲。

反复检查了好多遍,最后才发现是电源噪声在捣乱。

这小小的噪声,就像一只调皮的小老鼠,在电路里到处乱窜,把整个系统搞得乱七八糟。

那到底啥是电源噪声呢?简单来说,就是电源供应中的那些不稳定、不规则的波动。

想象一下,电路就像一个城市,电源就是给这个城市供电的电站。

如果电站输出的电一会儿强一会儿弱,一会儿高一会儿低,那城市里的各种设备能正常工作吗?肯定不行!这就是电源噪声带来的麻烦。

在集成电路里,电源噪声的产生原因有好多呢。

比如说,芯片内部的晶体管快速开关,这就像一群小朋友在教室里快速地跑来跑去,难免会磕磕碰碰,产生混乱。

还有,芯片外部的电源布线不合理,就好像城市里的电线乱拉乱接,能不出问题吗?电源噪声对集成电路的影响那可真是不容小觑。

它可能会导致信号失真,就像你听音乐的时候声音突然变得怪怪的,一点儿都不美妙。

还可能会降低系统的性能,本来你的手机能快速处理各种任务,结果因为电源噪声,变得慢吞吞的,急死人。

那怎么对电源噪声进行建模呢?这可不是一件简单的事儿。

我们得先搞清楚噪声的来源和特性,就像医生要先了解病人的病因和症状一样。

然后,选择合适的模型,有简单的,也有复杂的,得根据具体情况来定。

比如说,电阻电容模型、电感模型等等。

分析电源噪声也有很多方法。

可以通过仿真软件来模拟,看看在不同情况下噪声的表现。

也可以在实际的电路中进行测量,就像给电路做体检一样,找出问题所在。

在实际的工程应用中,为了减少电源噪声,工程师们可是想尽了办法。

比如优化电源的布局和布线,给电源加上滤波电容,就像给电路戴上了一顶稳定电压的帽子。

电子设计中常见的噪声问题及解决方法

电子设计中常见的噪声问题及解决方法在电子设计中,噪声是一个常见且影响深远的问题。

它会对系统性能造成严重影响,因此必须采取有效的方式进行解决。

在本文中,我们将讨论电子设计中常见的噪声问题以及相应的解决方法。

首先,让我们了解什么是噪声。

在电子设备中,噪声是指系统中出现的不希望的干扰信号,会导致输出信号的失真或降低信噪比。

电子设备中的噪声通常可以分为两类:外部噪声和内部噪声。

外部噪声是来自环境中的干扰,比如电源线上的电磁干扰、无线电信号等;内部噪声则是电子设备本身产生的信号干扰,比如器件本身的热噪声、晶体管的噪声等。

常见的电子设计中的噪声问题包括:热噪声、1/f 噪声、射频干扰以及电源干扰等。

热噪声是由于电阻器、晶体管等器件的热运动引起的,通常可以通过降低工作温度或选择低噪声器件来减小;1/f 噪声是一种与频率成反比的噪声,通常可以通过滤波器进行抑制;射频干扰是来自无线电频段的干扰信号,通常可以通过屏蔽、滤波等技术进行减小;电源干扰则是由电源波动等因素引入的干扰信号,可以通过滤波器、稳压器等措施进行消除。

为了解决这些噪声问题,我们可以采取一系列有效的解决方法。

首先,选择低噪声器件是很关键的,因为器件本身的噪声会影响整个系统的性能。

其次,合理布局电路板是很重要的,可以避免信号叠加引入额外的干扰。

此外,使用合适的滤波器、隔离器等器件也是很有效的方法,可以将不需要的干扰信号滤除。

在面对射频干扰时,可以采用屏蔽罩、隔离器件等技术来隔离干扰信号,保证系统的正常工作。

除了以上方法外,还可以利用数字信号处理技术来进行噪声消除。

通过滤波、降噪算法等方法,可以有效地去除信号中的噪声成分,提高系统的信噪比。

此外,还可以采用差分信号传输、差分输入放大器等技术来减小信号传输过程中的干扰,提高系统的抗干扰能力。

总的来说,电子设计中的噪声问题是一个不可忽视的挑战,但是只要采取适当的解决方法,就可以有效地减小噪声对系统性能的影响。

集成电路设计中的电源噪声抑制技术研究

集成电路设计中的电源噪声抑制技术研究在集成电路设计中,电源噪声是一个十分常见并且严峻的问题。

电源噪声指的是电路工作中电源线路噪声通过电源降压电路对电路产生的一种干扰。

这种噪声会影响电路性能,影响系统整体稳定性和可靠性。

因此,在集成电路设计和制造过程中,需要采用有效的电源噪声抑制技术,以保证设备和系统的正常运行。

一、电源噪声产生原因及影响电源噪声产生的原因主要包括两个方面,一是电源本身的特性问题,二是电源与电路的耦合问题。

电源的特性问题是指电源线路的阻抗特性,电源电容的特性以及DC-DC降压转换的效率问题等。

电路的耦合问题主要包括电源线路和电路之间的电容耦合和磁感耦合等。

电源噪声的产生会对整个电路的性能产生影响。

一方面可能会造成电路的抖动或震荡;另一方面可能会对数字信号产生误差,对模拟信号产生增加白噪声的影响。

因此,需要开发出一些电源噪声抑制技术,通过控制电源线路本身的特性问题和电路的耦合问题来扼杀噪声在产生前。

二、电源噪声抑制技术1. 降噪电源设计降噪电源设计是一种基于纹波抑制技术的电源设计,其主要思路是降低电源输出阻抗,使得电源输出的纹波噪声降低。

降噪电源设计的核心技术就是通过对于电源线路和降压电路进行优化,使其尽可能的降低输出的纹波噪声以及电源本身的纹波噪声。

在通常的降噪电源设计中,会采用一系列的电容、电感、滤波器以及稳压器等单元来构建整个电源。

而且,为了提供更高的电源质量和可靠性,还会使用一些更为复杂的降噪电源设计技术,如电源调制、电容快速响应等。

2. 噪声隔离技术在集成电路中,有些电源线路必须隔离开来,以避免电源线噪声的互相干扰。

噪声隔离技术就是一种能够将不同电源线隔离开来的技术。

在噪声隔离技术中,通常会使用电源隔离器、磁耦合器、放大器和变压器等单元。

在一些噪声隔离技术的方案中,电源线路之间会使用电容、电阻和电感等元件进行连接,以帮助控制线路的阻抗特性和干扰电流。

另外,磁耦合器和电源隔离器等单元则主要是通过电感和变压器等元件将两条电源线隔离开来,从而避免噪声产生的干扰。

集成电路版图设计基础第8章:噪声问题

利用常识解决噪声的方法

衬底可靠电位的连接: 衬底可靠电位的连接: a. 尽量把衬底与电源的接触穿孔(substrate 尽量把衬底与电源的接触穿孔 接触穿孔( contact)的位置和该位置的管子的衬底注入极 contact)的位置和该位置的管子的衬底注入极 (substrate injector)的距离缩小,距离越近越 injector)的距离缩小 距离缩小,距离越近越 好,因为这种距离的大小对衬底电位偏差影响非常 大。 b. 把衬底接触孔的数量增多,尽量多打孔,保证衬底 衬底接触孔的数量增多,尽量多打孔,保证衬底 与电源的接触电阻较小。

GND noise

100mV

GND

big fat wire

noise

0mV

school of phye

basics of ic layout design

5

利用常识解决噪声的方法

衬底噪声( 衬底噪声(substrate noise) noise)

产生原因: 产生原因: 源/漏-衬底pn结正偏导通,或者电源连线接点引入 衬底pn结正偏导通 结正偏导通,或者电源连线接点引入 串绕,使得衬底电位 衬底电位会产生抖动偏差 抖动偏差。 的串绕,使得衬底电位会产生抖动偏差。 解决方法: 解决方法: a. 轻掺杂的衬底,用保护环把敏感部分电路包围起来 轻掺杂的衬底,用保护环 保护环把敏感部分电路包围 包围起来 b. 把gnd和衬底在片内连在一起,然后由一条线连到 gnd和衬底在片内连在一起,然后由一条线连到 片外的全局地线,使得gnd和衬底的跳动一致 跳动一致,也 片外的全局地线,使得gnd和衬底的跳动一致,也 可以消除衬底噪声 场屏蔽作用:每个block外围一层金属,使每单元 c. 场屏蔽作用:每个block外围一层金属,使每单元 模块同电势 模块同电势,而且模块之间不相互影响 同电势,而且模块之间不相互影响

集成电路设计中的功率噪声抑制技术研究

集成电路设计中的功率噪声抑制技术研究一、引言在现今的电子工业中,集成电路是必不可少的组成部分。

无论是计算机、手机还是家庭电器,集成电路都扮演着重要的角色。

而随着集成度的提高和工作频率的增加,功率噪声逐渐成为了制约集成电路性能的瓶颈。

因此,对于功率噪声的抑制技术有了越来越高的要求。

本文将着重研究集成电路设计中的功率噪声抑制技术,包括功率噪声产生的原因,抑制方法以及实际应用案例等方面的内容。

二、功率噪声的产生原因功率噪声是指由于电子器件耗能而引起的信号噪声,如图1所示。

它的产生原因有多种,其中最主要的原因是器件的开关动作。

在数字电路中,开关动作产生的噪声源主要有两个,即电压源噪声和电流源噪声。

电压源噪声是由于开关器件的电容充放电引起的,而电流源噪声则是由于开关器件的电感和电源引脚电容之间的振荡引起的。

例如,当晶体管开关时,它在导通状态和截止状态之间进行切换,产生的瞬时电流会导致电源电压波动,从而导致功率噪声。

同时,在集成电路中,器件密度越高,功率噪声就越严重,因此理解和控制功率噪声是至关重要的。

三、功率噪声的抑制方法为了抑制功率噪声,现有的技术主要包括以下几种。

(一)降低开关速度通过降低开关速度,可以减缓电容充放电和电感振荡造成的电源波形变化,从而减少功率噪声的产生。

但是这种方法会影响系统的运行速度和效率,并可能导致时序错误。

(二)使用降噪电源使用降噪电源是另一种有效的方式,它可以提供平稳的电源电压,从而消除电源噪声。

但是,这种方法成本较高,并且需要占用更多的空间。

(三)加入输出电容和电感加入输出电容和电感是减少功率噪声的传统方法,降噪效果良好。

它们可以消除电源波动并保持电源电压稳定,同时消除开关产生的高频噪声,但是也会增加滞后时间和频率响应。

(四)使用回授降噪电路回授降噪电路是一种通过反馈电路抑制功率噪声的技术。

例如,在交流电路中,可以使用反馈电路来抵消电路中存在的噪声,本质是将输出信号反馈到输入端,使得输入端信号与输出端信号相等,从而抑制信号噪声。

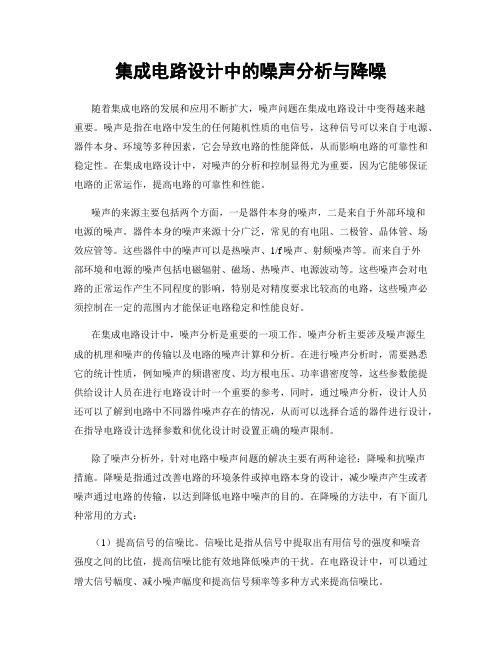

集成电路设计中的噪声分析与降噪

集成电路设计中的噪声分析与降噪随着集成电路的发展和应用不断扩大,噪声问题在集成电路设计中变得越来越重要。

噪声是指在电路中发生的任何随机性质的电信号,这种信号可以来自于电源、器件本身、环境等多种因素,它会导致电路的性能降低,从而影响电路的可靠性和稳定性。

在集成电路设计中,对噪声的分析和控制显得尤为重要,因为它能够保证电路的正常运作,提高电路的可靠性和性能。

噪声的来源主要包括两个方面,一是器件本身的噪声,二是来自于外部环境和电源的噪声。

器件本身的噪声来源十分广泛,常见的有电阻、二极管、晶体管、场效应管等。

这些器件中的噪声可以是热噪声、1/f噪声、射频噪声等。

而来自于外部环境和电源的噪声包括电磁辐射、磁场、热噪声、电源波动等。

这些噪声会对电路的正常运作产生不同程度的影响,特别是对精度要求比较高的电路,这些噪声必须控制在一定的范围内才能保证电路稳定和性能良好。

在集成电路设计中,噪声分析是重要的一项工作。

噪声分析主要涉及噪声源生成的机理和噪声的传输以及电路的噪声计算和分析。

在进行噪声分析时,需要熟悉它的统计性质,例如噪声的频谱密度、均方根电压、功率谱密度等,这些参数能提供给设计人员在进行电路设计时一个重要的参考,同时,通过噪声分析,设计人员还可以了解到电路中不同器件噪声存在的情况,从而可以选择合适的器件进行设计,在指导电路设计选择参数和优化设计时设置正确的噪声限制。

除了噪声分析外,针对电路中噪声问题的解决主要有两种途径:降噪和抗噪声措施。

降噪是指通过改善电路的环境条件或掉电路本身的设计,减少噪声产生或者噪声通过电路的传输,以达到降低电路中噪声的目的。

在降噪的方法中,有下面几种常用的方式:(1)提高信号的信噪比。

信噪比是指从信号中提取出有用信号的强度和噪音强度之间的比值,提高信噪比能有效地降低噪声的干扰。

在电路设计中,可以通过增大信号幅度、减小噪声幅度和提高信号频率等多种方式来提高信噪比。

(2)优化电路布局结构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

V+

GND V+

GND

层叠供电轨线能 得到额外的小电容

school of phye basics of ic layout design 13

导线方面的解决方法

谐波干扰:

把信号分解,会看到一个基本频率和许多谐波。 谐波通常比原有信号弱且其频率位于原有频率的倍 数上的信号。 电路的某一个谐波可能正好与你需要处理的另一个 输入信号的频率一样,必须消除这一谐波噪声。 可以采用相关噪声技术,如保护带、隔离屏蔽信号 等,来消除/减弱谐波有可能引起的干扰。

M3 M2 GND M2 GND M2 M3 GND M2 GND

signal

signals

M3

M3

surrounded by shielding

school of phye

lots of quiet signals

10

basics of ic layout design

导线方面的解决方法

差分信号:

paired lines will be hit by the same noise spikes.

school of phye basics of ic layout design

11

导线方面的解决方法

去耦供电轨线:

供电轨线上放臵尺寸很大的去耦电容。 闯入供电轨线的任何噪声首先被吸收到接地线,只 有很少的噪声能越过这个电容进入电路。

4

利用常识解决噪声的方法

衬底噪声(substrate noise)

产生原因: 源/漏-衬底pn结正偏导通,或者电源连线接点引入 的串绕,使得衬底电位会产生抖动偏差。 解决方法: a. 轻掺杂的衬底,用保护环把敏感部分电路包围起来 b. 把gnd和衬底在片内连在一起,然后由一条线连到 片外的全局地线,使得gnd和衬底的跳动一致,也 可以消除衬底噪声 c. 场屏蔽作用:每个block外围一层金属,使每单元 模块同电势,而且模块之间不相互影响

差分电路是一种用来检测两个同一来源的特殊走线 的信号之差的设计技术。两条导线自始至终并排排列。 每条线传递同样的信息,但信息的状态相反。 差分逻辑有很强的抗噪声能力。

block 1 noise block 2

signal through line B

differential A-B

signal through line A

吵闹的邻居

和祖母聊天 – 摇滚乐队 – 调小声音 – 乐队回屋 关好门窗 - 和祖母回屋 (搬家) (拒绝回屋 - 司法长官 – 定时排练 – 轮换错开)

school of phye

basics of ic layout design

2

利用常识解决噪声的方法

调小音量:

在电路中相当于减小信号摆幅。 在一个混合信号芯片中,主要是让数字部分保持安 静,即采用电压摆幅小的数字逻辑。 电压摆幅基本上不属于版图问题,但可在某些时候 也可以成为版图问题,如可以选择电压摆幅小的库。

摇滚乐队搬进他们自己的屋里:

房间提供“隔离”。 可把产生噪声的模块藏在“死亡之墙”的后面。 建立墙壁的版图技术有许多种。一个简单的方法是 用一大圈接地的衬底接触把整个模块围起来。

school of phye

basics of ic layout design

3

利用常识解决噪声的方法

摇滚乐队搬进他们自己的屋里:

basics of ic layout design

8

利用常识解决噪声的方法

搬到一个新的居住小区:

把噪声电路和安静电路远离放臵。

noisy quiet quiet noisy

school of phye

basics of ic layout design

9

导线方面的解决方法

同轴屏蔽:

信号沿内部导线传送,外层的屏蔽线接地。 外界出现的任何噪声都由接地信号线接收而不会被 内部的信号线接收。 版图中可以采用同样的方法。想办法用360度的屏 蔽包围信号线。

利用常识解决噪声的方法

导线方面的解决方法

school of phye

basics of ic layout design

1

利用常识解决噪声的方法

原因:

噪声在集成电路中可以成为一个很大的问题,特 别是当电路是一个要接收某一很弱信号的非常敏感的 电路,而它又位于一个正在进行着各种计算、控制逻 辑和频繁切换的电路旁边的时候。必须特别注意版图 和平面布局。

school of phye

basics of ic layout design

14

导线方面的解决方法

width and spacing: widening wires and increasing spacing between wires reduce coupling noise to some extent. solving inductive and capacitance noise: one approach is dedicate power and ground planes, much like in a printed circuit board. another approach is to shield noisesensitive nets (clock, analog voltage) with power and ground lines. a third approach is to use differential signaling.

V+

noise quiet

V-

高频噪声信号通过电容接 地要比冲向电路容易得多

school of phye

basics of ic layout design

12

导线方面的解决方法

层叠供电轨线:

把电源轨线和接地轨线交替排列。 这一技术本身就在轨线之间形成了额外的去耦小电 容,采用这种方法我们可以用小得多的空间来去耦供 电轨线,而不需要在电路中插入一个大电容。

如果将衬底接触的尺寸设计得很小,噪声就有可能 绕过它或从它的下面通过。一个大的接触则意味着不 会发生这种情况。 如果担心噪声问题,不要使用很细的导线。要用导 电良好的粗大导线。

GND noise

100mV 0mV

GND

big fat ws of ic layout design

school of phye

basics of ic layout design

6

利用常识解决噪声的方法

回到自己的屋里:

不仅在噪声模块周围放臵保护带,把安静模块也用 保护带围起来。 双重隔离

noisy block

quiet block

school of phye

basics of ic layout design

basics of ic layout design 5

school of phye

利用常识解决噪声的方法

衬底可靠电位的连接:

a. 尽量把衬底与电源的接触穿孔(substrate contact)的位臵和该位臵的管子的衬底注入极 (substrate injector)的距离缩小,距离越近越 好,因为这种距离的大小对衬底电位偏差影响非常 大。 b. 把衬底接触孔的数量增多,尽量多打孔,保证衬底 与电源的接触电阻较小。

7

利用常识解决噪声的方法

关闭所有的门窗:

要用保护带包围整个噪声模块,而不要留有任何缝 隙。因有些噪声会从此处溜出去。

呼叫行政长官:

使摇滚乐队同意在每周特定时间排练相当于一个设 计人员对电路的协调问题而不属于版图问题。 控制噪声电路和安静电路在不同的时间工作,轮换 错开。

school of phye

basics of ic layout design 15

school of phye

THE END OF CHAPTER EIGHT THANK YOU !!

school of phye

basics of ic layout design

16