卷积码的编码及解码Viterbi解码Word版

卷积码的编码及解码Viterbi解码Word版

卷积码的编码及解码(Viterbi 解码)一、实验目的1、了解卷积码的基本原理;2、掌握卷积码编码的电路设计方法;2、掌握卷积码 Viterbi 译码的基本方法和电路设计方法。

二、实验仪器1、移动通信实验箱一台;2、台式计算机一台;三、实验原理1.卷积码编码原理卷积码是一个有限记忆系统,它也将信息序列切割成长度 k的一个个分组,与分组码不同的是在某一分组编码时,不仅参看本时刻的分组而且参看本时刻以前的 L 个分组。

我们把 L+1 称为约束长度。

2.卷积码的译码算法(硬判决 Viterbi 译码)Viterbi译码算法是一种最大似然算法,它不是在网络图上依次比较所有可能的路径,而是接收一段,计算,比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。

Viterbi解码算法的基本步骤如下:1、从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。

对每一状态,挑选并存储一条有最大度量的部分路径及其部分度量,称此部分路径为留选(幸存)路径。

2、j增加1,把此时刻进入每一状态的所有分支度量,和同这些分支相连的前一时刻的留选路径的度量相加,得到了此时刻进入每一状态的留选路径,加以存储并删去其他所有的路径。

因此留选路径延长了一个分支。

3、若j<L+m,则重复以上步骤,否则停止,译码器得到了有最大路径度量的路径。

上面的过程可以简单的总结为“加、比、选”(也称ACS)。

四、实验步骤1、将实验箱和计算机通过串行口连接好,为实验箱上电。

2、将与实验箱相连的电脑上的学生平台程序打开。

在“实验选择”栏中选择“卷积码”实验,点击确认键。

从而进入此实验界面。

3、在实验界面上点“生成数据”,让系统生成待编码的随机比特。

也可在界面上直接双击所显示的 bit,修改其值。

4、在界面上点击下发“原始数据”,该数据将被送入单片机(或 CPLD)进行卷积编码然后经过编码的数据被送回学生平台并显示在“编码数据”栏。

DRM系统中卷积编码及Viterbi译码的实现

( . k 1z

U i r , a gh uz u e H n zo k vs

300 , h 0 C i a

2 u t cm Tl o o L . H nzo k . T S r e c C . t , ag huz ao em d

维普资讯

信 号 与 信 息 处 理

D M 系统 中卷 积 编 码 及 V tr i 码 的 实现 R i b译 e

章 宇 , 马 彬

(. 1 浙江大 学 计 算机 学 院, 江 杭 州 30 0 ; 浙 10 0

2U . T斯达康 通讯 有 限公 司 , 浙江 杭 州 3 00 ) 10 0

Absr c T e c n ou in lc dn n i r id c dn s a fe t e fr o d er rc re t n meh d, n ti d l s d n mo ie ta t h o v lto a o ig a d vt b e o ig i n e ci o w r ro o rci to a d i swiey u e i b l e v o c mmu iain d s tli o o nc to sa aelt c mmu iain I i a e , rs n t a piain i n e n c to s.n t s p p r we pe e ti h s p lc t n DRM y tm . e s f r to s gv n a o s se Th ot e me d wa ie s a wa h

p vd sa g o to o d a t o e n DRM ytm . o r ie o d me d t e lwi c d si h h s se Ke r s DRM ; u cu e o v lt n lc d s; i r e o ig y wo d p n tr d c n oui a o e vt bid c dn o e

卷积编码及Viterbi译码的低时延FPGA设计实现

卷积编码及Viterbi译码的低时延FPGA设计实现张健,吴倩文,高泽峰,周志刚(杭州电子科技大学电子信息学院袁浙江杭州310018)摘要:针对毫米波通信的高速率和低时延设计要求,设计实现1/2码率(2,1,7)卷积码的低时延译码。

采用高度并行优化实现框架、低延时的最小值选择方式,获得Viterbi硬判决译码算法的输出遥利用基于Xilinx公司的Artix7-xc7a200t芯片综合后,译码器的数据输出延时约89个时钟周期,最高工作频率可达203.92MHz遥结果表明,该译码器可支持吉比特级的数据传输速率,实现了低延时、高速率的编译码器遥关键词:毫米波通信;卷积码;Viterbi译码;system generator中图分类号:TN911.22文献标识码:A DOI:10.16157/j.issn.0258-7998.201025中文引用格式:张健袁吴倩文,高泽峰袁等.卷积编码及Viterbi译码的低时延FPGA设计实现[J].电子技术应用,2021,47 (6):96-99.英文弓I用格式:Zhang Jian,Wu Qianwen,Gao Zefeng,et al.Low-latency FPGA design and implementation of convolutional coding and Viterbi decoding[J].Application of Electronic Technique,2021,47(6):96-99.Low-latency FPGA design and implementation of convolutionalcoding and Viterbi decodingZhang Jian,Wu Qianwen,Gao Zefeng,Zhou Zhigang(School of Electronic Information,Hangzhou Dianzi University,Hangzhou310018,China)Abstract:Aiming at the high-speed and low-delay design requirements of millimeter wave communications,this paper designs low-delay decoding of convolutional codes with1/2code rate(2,1,7).A highly parallel optimization implementation framework and a low-latency minimum selection method are adopted to obtain the output of the Viterbi hard decision decoding algorithm.After synthesis using the Artix7-xc7a200t chip based on Xilinx,the data output delay of the decoder is about89clock cycles,and the highest operating frequency can reach203.92MHz.The results show that the decoder can support gigabit-level data transmission rates,and realizes a low-latency,high-rate codec.Key words:millimeter wave communication;convolutional code;Viterbi decoding;system generator0引言近年来,5G移动通信技术的发展受到人们的广泛关注,高速率、高可靠、低时延的高能效通信成为毫米波通信中的重要因素[1-2」。

卷积码的维特比译码ppt.docx

矩阵表示当m=2,A0=(l 1)T, A1=(O 1)T, A2=(l 1)T 时, 如前3个输入为110,则前6个输出为111010AAn-1 An-20 0A)2M ( m ()+ m j D + m 2 D」+ •…C (D) = c()+ c ] D+ c 2 Q + --------C⑺(£))二c Oy +c Iy D + c2y£)2+ …J = l,2,・・・,〃o状态图表示法以两个D触发器的组合值为状态,如D1D2,描述从当前状态在不同的输入时的输出及将到达的状态,每个分支上的标注为yly2, 表示当前的输出。

(2,1,2)码状态图(2丄2)截断篱状图(2儿2)码编码电路码编码电路解析对¥用建口)表示常数乘法 先霧[器,共有(m+l )*n<5个,(i=l,2,・・・,k;j=l ,2,…由入 到纟小)。

g (ij )=l 时常三每绅租與出”“木玮后去右與的峋成,#模2加法器是将与其相关的$器。

占 一 7L 乂一上丄_、丄,土E 体不仅 丕与开关K 在每一节拍中’、 : 移动n 次,每一次输® 入信息元而输出凸元。

接线。

输出码子c 是: ■1信息元 输入1^411ft犬态累加距离译出序列:00 0接受100001序列f 1011011100 A0011(X)0000译码结果分析1100000011 5 :10时间to—tl七2七3t4t 消息序列m0001发送序列U0000001101接收序列R1010000111译码序列C0|o0111101 L01\的路径返回全零状态并完成译码。

图例:输入比讐510说明:醴曲是进入屛编码器的序列,flilll 是编码器输出,是经信道传输后的译码器输入,隸烤」是译码器输出。

白色码子是编码器清零的冗余信息,沁o 窗是发生番滾的比特位。

七61111,653状态图生成过程9 0 ® 0=10状态。

卷积码的维特比译码

卷积码的维特比译码卷积编码器自身具有网格结构,基于此结构我们给出两种译码算法:Viterbi 译码算法和BCJR 译码算法。

基于某种准则,这两种算法都是最优的。

1967 年,Viterbi 提出了卷积码的Viterbi 译码算法,后来Omura 证明Viterbi 译码算法等效于在加权图中寻找最优路径问题的一个动态规划(Dynamic Programming)解决方案,随后,Forney 证明它实际上是最大似然(ML,Maximum Likelihood)译码算法,即译码器选择输出的码字通常使接收序列的条件概率最大化。

BCJR 算法是1974 年提出的,它实际上是最大后验概率(MAP,Maximum A Posteriori probability)译码算法。

这两种算法的最优化目标略有不同:在MAP 译码算法中,信息比特错误概率是最小的,而在ML 译码算法中,码字错误概率是最小的,但两种译码算法的性能在本质上是相同的。

由于Viterbi 算法实现更简单,因此在实际应用比较广泛,但在迭代译码应用中,例如逼近Shannon 限的Turbo 码,常使用BCJR 算法。

另外,在迭代译码应用中,还有一种Viterbi 算法的变种:软输出Viterbi 算法(SOV A,Soft-Output Viterbi Algorithm),它是Hagenauer 和Hoeher 在1989 年提出的。

为了理解Viterbi 译码算法,我们需要将编码器状态图按时间展开(因为状态图不能反映出时间变化情况),即在每个时间单元用一个分隔开的状态图来表示。

例如(3,1,2)非系统前馈编码器,其生成矩阵为:G(D)=[1+D1+D21+D+D2](1)图1 (a)(3,1,2)编码器(b)网格图(h=5)假定信息序列长度为h=5,则网格图包含有h+m+1=8 个时间单元,用0 到h+m=7 来标识,如图1(b)所示。

假设编码器总是从全0 态S0 开始,又回到全0 态,前m=2 个时间单元对应于编码器开始从S0“启程”,最后m=2 个时间单元对应于向S0“返航”。

matlab卷积编码与viterbi译码的实现

matlab卷积编码与viterbi译码的实现MATLAB中viterbi译码算法讨论⼤家可以再评论区交流!!!MATLAB中实现viterbi译码的函数为:convenc其中:code = convenc(msg,trellis)vitdec其中:vitdec(code,trellis,tblen,opmode,dectype)code卷积编码,trellis⽹格表,tblen回溯长度,opmode:cont、term、trunc,dectype:unquant、hard、soft;本⼈最近在做⼀个关于viterbi译码算法,最终在FPGA中实现,在FPGA中最终的实现⽅案为xillinx IP核实现。

在此之前⽤MATLAB进⾏仿真验证。

matlab程序:Tre = poly2trellis(7,[133 171]);通过poly2trellis⽣成逻辑关系图,如下图所⽰。

逻辑关系图%卷积编码:msg = [0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];code = convenc(msg,Tre);%code = [0,0,1,1,0,1,0,0,0,1,1,0,0,1,0,1,1,0,0,0,1,0,0,0,1,0,1,0,0,1,1,1,1,1,1,1,0,0,1,1,0,1,0,1,1,1,1,0];%这是通过convenc函数⽣成的卷积码%vitdec译码:%在vitdec译码过程中采⽤硬判决,通过不同的tblen和opmode来找出其中关系。

%(1) opmode = conttblen = 12;msg_dat = vitdec(code,Tre,tblen,'cont','hard');%msg_dat =[ 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 ];%通过了解到cont模式中,vitdec译码会有延迟,延迟的长度为tblen长度,所以在此对vitdec进⾏修改code_temp = [code,zeros(1,24)];msg_temp = vitdec(code_temp ,T,12,'cont','hard')msg_dat = msg_temp(13:end);%msg_dat = [ 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];%此时vitdec译码出来的数据和信源⼀样tblen = 18;code_temp = [code,zeros(1,24)];msg_temp = vitdec(code_temp ,T,12,'cont','hard')msg_dat = msg_temp(13:end);%msg_dat = [ 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0];%此时vitdec译码出来的数据和信源在后⾯最后⼀位不⼀样%(2) opmode = termtblen = 12;msg_dat = vitdec(code,Tre,tblen,'term','hard');%msg_dat = [0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 0 0 0 0 0 0 0];%此时vitdec译码出来的数据和信源⼀样前16位和信源⼀样后⾯的就出错了tblen = 18;msg_dat = vitdec(code,Tre,tblen,'term','hard');%msg_dat = [0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 0 0 0 0 0 0 0];%此时vitdec译码出来的数据和信源⼀样前16位和信源⼀样后⾯的就出错了%(3)opmode = trunctblen = 12;msg_dat = vitdec(code,Tre,tblen,'trunc','hard');%msg_dat = [ 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];%此时vitdec译码出来的数据和信源⼀样tblen = 18;msg_dat = vitdec(code,Tre,tblen,'trunc','hard');%msg_dat = [ 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];%此时vitdec译码出来的数据和信源⼀样总结:以上通过⽐较tblen和opmode模式的不同对产⽣的结果,其中cont和trunc的模式总结起来就是cont有tblen延迟,但是trunc没有。

卷积码编码器及Viterbi译码器的设计

1.

卷积码是一种性能优越的信道编码。(n ,k ,N) 表示把 k 个信息比特编成 n 个比特,N 为编码约束长度,说明编码过程中互相约束的码段个数。卷积码编码后的 n 个码元不仅与当前组的 k 个信息比特有关,而且与前 N - 1 个输入组的信息比特有关。编码过程中相互关联的码元有 N ×n 个。R = k/ n 是卷积码 的码率,码率和约束长度是衡量卷积码的两个重要参数。 卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。卷积码的纠错能力随着 N 的增加而增大,而差错率随着 N 的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[5]。

Abstract:This course design mainly resolves to a convolutional code sequence for Viterbi Viterbi decoding output, and through the Matlab software to carry on the design and simulation, and analysis of bit error rate. In curriculum design, system development platform for Windows Vista Ultimate, program design and simulation using Matlab R2007a(7.4), and finally the simulation list is consistent with theoretical analysis.

卷积码编码及其Viterbi译码的实现

’ 9 12 I 1 .2 ’ N 文献 标 识 码 A 中 图分 类 号

Th mp e n a i n o n ou in lEn o i g a tr iDe o ng e I lme t to fCo v l to a c d n nd Vie b c d i

A s r c T e c dn f o v l t n c d d pe n3 y tm a d V tr i e o ig o / aec n ouin l e e aeds u s di i b ta t h o ig o n oui o e a o td i G s s n i b c dn f 2 rt o v lt a d r i se n t s c o e e d 1 o c c h p p r o h a e o e l i g t e s s m i ih r e iin y w t h a l y t ’ r r n c ,s rio a ,d t v r o n d a e .F rt e s k f rai n y t n hg e f c c i t e sne s s m S p f ma e u vv rp t z h e e h e e o h a o ef wi a a l g n d cs n p r r p i z d i e s s m i lm nain. h e ut o pi z t n s o a o e s s m r r c d e iin ya e e i o at ae o t e t y t mpe e tt i s mi nh e o T er s l f t a i h w t t t t y t p f m ̄ e a fce c r a o mi o h bh h e e o n i rv d t s ic se h i lt n Sr s l ,w ih m y p o ie sg i c trfrn e i y t i p e nain. mp o e .I a o d su ss te s l muai ’ e ut o s hc a rvd inf a ee c sse m lme tt in e n m o

卷积码编码与译码

例: (n, k, N) = (3, 1, 3)卷积码编码器方框图设输入信息比特序列是bi-2 bi-1 bi bi+1,则当输入bi时,此编码器输出3比特ci di ei,输入和输出的关系如下:

实际应用时常用的卷积码是(2,1,7)卷积码例如:IEEE 802.11a、DVB-T的内码;(2,1,7)卷积码的编码器,如图:

(3, 1, 3)卷积码 设现在的发送信息位为1101,为了使图中移存器的信息位全部移出,在信息位后面加入3个“0”,故编码后的发送序列为111 110 010 100 001 011 000。并且假设接收序列为111 010 010 110 001 011 000,其中第4和第11个码元为错码。 由于这是一个(n, k, N) = (3, 1, 3)卷积码,发送序列的约束度N = 3,所以首先需考察nN = 9比特。第1步考察接收序列前9位“111 010 010”。由此码的网格图可见,沿路径每一级有4种状态a, b, c和d。每种状态只有两条路径可以到达。故4种状态共有8条到达路径。 现在比较网格图中的这8条路径和接收序列之间的汉明距离。

4

是

现在将到达每个状态的两条路径的汉明距离作比较,将距离小的一条路径保留,称为幸存路径。若两条路径的汉明距离相同,则可以任意保存一条。这样就剩下4条路径了,即表中第2, 4, 6和8条路径。

第2步继续考察接收序列的后继3个比特“110”。计算4条幸存路径上增加1级后的8条可能路径的汉明距离。结果如下表。 表中最小的总距离等于2,其路径是abdc+b,相应序列为111 110 010 100。它和发送序列相同,故对应发送信息位1101。 按照表中的幸存路径画出的网格图示于下图中。

序号

路径

对应序列

卷积码-Viterbi译码

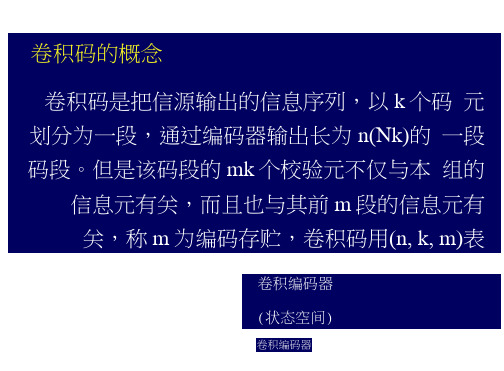

卷积码-Viterbi译码卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(n-k)个校验位仅与本码组的k个信息位有关,而与其它码组无关。

为了达到一定的纠错能力和编码效率(=k/n),分组码的码组长度n通常都比较大。

编译码时必须把整个信息码组存储起来,由此产生的延时随着n的增加而线性增加。

为了减少这个延迟,人们提出了各种解决方案,其中卷积码就是一种较好的信道编码方式。

这种编码方式同样是把k个信息比特编成n个比特,但k和n通常很小,特别适宜于以串行形式传输信息,减小了编码延时。

与分组码不同,卷积码中编码后的n个码元不仅与当前段的k个信息有关,而且也与前面(N-1)段的信息有关,编码过程中相互关联的码元为nN个。

因此,这N时间内的码元数目nN通常被称为这种码的约束长度。

卷积码的纠错能力随着N 的增加而增大,在编码器复杂程度相同的情况下,卷段积码的性能优于分组码。

另一点不同的是:分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段,把纠错性能与码的结构十分有规律地联系起来,目前大都采用计算机来搜索好码。

下面通过一个例子来简要说明卷积码的编码工作原理。

正如前面已经指出的那样,卷积码编码器在一段时间内输出的n位码,不仅与本段时间内的k位信息位有关,而且还与前面m段规定时间内的信息位有关,这里的m=N-1通常用(n,k,m)表示卷积码(注意:有些文献中也用(n,k,N)来表示卷积码)。

图1就是一个卷积码的编码器,该卷积码的n = 2,k = 1,m = 2,因此,它的约束长度nN = n×(m+1) = 2×3 = 6。

图1 (2,1,2)卷集码编码器在图1中,与为移位寄存器,它们的起始状态均为零。

、与、、之间的关系如下:(1)假如输入的信息为D = [11010],为了使信息D全部通过移位寄存器,还必须在信息位后面加3个零。

表1列出了对信息D进行卷积编码时的状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

卷积码的编码及解码(Viterbi 解码)

一、实验目的

1、了解卷积码的基本原理;

2、掌握卷积码编码的电路设计方法;

2、掌握卷积码 Viterbi 译码的基本方法和电路设计方法。

二、实验仪器

1、移动通信实验箱一台;

2、台式计算机一台;

三、实验原理

1.卷积码编码原理

卷积码是一个有限记忆系统,它也将信息序列切割成长度 k的一个个分组,与分组码不

同的是在某一分组编码时,不仅参看本时刻的分组而且参看本时刻以前的 L 个分组。

我们把 L+1 称为约束长度。

2.卷积码的译码算法(硬判决 Viterbi 译码)

Viterbi译码算法是一种最大似然算法,它不是在网络图上依次比较所有可能的路径,

而是接收一段,计算,比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。

Viterbi解码算法的基本步骤如下:

1、从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。

对每一状态,挑选并存储一条有最大度量的部分路径及

其部分度量,称此部分路径为留选(幸存)路径。

2、j增加1,把此时刻进入每一状态的所有分支度量,和同这些分支相连的前一时刻的留选路径的度量相加,得到了此时刻进入每一状态的留选路径,加以存储并删去其他所有的路径。

因此留选路径延长了一个分支。

3、若j<L+m,则重复以上步骤,否则停止,译码器得到了有最大路径度量的路径。

上面的过程可以简单的总结为“加、比、选”(也称ACS)。

四、实验步骤

1、将实验箱和计算机通过串行口连接好,为实验箱上电。

2、将与实验箱相连的电脑上的学生平台程序打开。

在“实验选择”栏中选择“卷积码”实验,点击确认键。

从而进入此实验界面。

3、在实验界面上点“生成数据”,让系统生成待编码的随机比特。

也可在界面上直接双击所显示的 bit,修改其值。

4、在界面上点击下发“原始数据”,该数据将被送入单片机(或 CPLD)进行卷积编码然

后经过编码的数据被送回学生平台并显示在“编码数据”栏。

5、学生可以在噪声一栏加入差错 bit,然后点击“加噪声”,再点击“加噪数据”,将加入噪声的信息比特下发到单片机(或 CPLD)进行 Viterbi 译码。

译码以后的数据被回显在解码数据一栏,同时,误码比特也被统计并显示。

五.实验记录与思考

(1)记录加入分散的随机差错的一次实验数据。

(2)记录加入一个突发差错但差错比特总数和 1 相同的实验数据。

3 比较上述两组数据的纠错性能,说明原因。

答:加入随机差错时的纠错性能好一些。

随机差错:信道中各码元是否出现差错,与其前、后码元是否差错无关,每个码元独立地按一定的概率产生差错。

从统计规律看,可以认为这种随机差错是由加性高斯白噪声 AWGN 引起的。

突发差错:差错成片出现,一个差错片称为一个突发差错。

突发差错总是以差错码元开头、以差错码元结尾,头尾之间并不是每个码元都错,而是码元差错概率大到超过了某个标准值。

(注:可编辑下载,若有不当之处,请指正,谢谢!)。