西工大cmos实验报告一

CMOS模拟集成电路设计与仿真标准实验报告资料

电子科技大学实验报告学生姓名:鄢传宗,梁成豪学号:2011031030010,2011031030009 指导教师:王向展实验地点:211楼606 实验时间:2014.6.4一、实验室名称:微电子技术实验室二、实验项目名称:CMOS模拟集成电路设计与仿真三、实验学时:4四、实验原理IC设计与制造的主要流程五、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:∙根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

∙学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、设计一个运算放大器电路,要求其增益大于40dB, 相位裕度大于60º,功耗小于10mW。

3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。

4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。

5、电路性能的优化与器件参数调试,要求达到预定的技术指标。

6、整理仿真数据与曲线图表,撰写并提交实验报告。

七、实验仪器设备(1)工作站或微机终端一台(2)局域网(3)EDA仿真软件 1套八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的电路结构。

并进行计算分析,确定其中各器件的参数。

调用Symbol生成命令,生成符号如下图。

3、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分析的参数设置方法。

电源电压设置:输入信号设置:建立时间测试信号设置:4、电路性能的优化与器件参数调试,要求达到预定的技术指标。

系统cmos参数设置-实验报告

计算机科学与技术系实验报告课程名称:计算机组装与维护实训实验名称:系统cmos参数设置姓名:曹蓉学号:124077031002 日期: 20141113 地点: 13机房成绩:教师:张毓福一、实验目的熟悉系统cmos参数设置。

二、实验内容1.启动BIOS设置程序2.了解系统BIOS设置的主要功能3.常用CMOS系统参数的设置了解并修改本机器系统CMOS的基本配置情况。

查看并修改系统日期、时间、硬盘、光驱、内存等硬件配置情况,并设置密码修改机器的启动顺序三、实验原理BIOS是英文"Basic Input Output System"的缩略语,直译过来后中文名称就是"基本输入输出系统"。

其实,它是一组固化到计算机内主板上一个ROM芯片上的程序,它保存着计算机最重要的基本输入输出的程序、系统设置信息、开机后自检程序和系统自启动程序。

其主要功能是为计算机提供最底层的、最直接的硬件设置和控制。

CMOS(本意是指互补金属氧化物半导体——一种大规模应用于集成电路芯片制造的原料)是微机主板上的一块可读写的RAM芯片,用来保存当前系统的硬件配置和用户对某些参数的设定。

CMOS可由主板的电池供电,即使系统掉电,信息也不会丢失。

CMOS RAM本身只是一块存储器,只有数据保存功能,而对CMOS中各项参数的设定要通过专门的程序。

四、实验设备已经组装好的计算机五、实验过程及分析1 标准CMOS设置(Standard CMOS Features)标准设置中是最基本的设置,比如日期、时间等等,2、高级BIOS特性设置(Advanced BIOS Features),其中有病毒报警开关 Virus Warning,预设置 Disabled 关闭,建议值 Enabled 打开,当试图改变系统时报警。

还有第一优先开机设备,可以更改其为u盘或是光驱来安装操作系统。

还有安全选项,设定什么情况下输入密码Security Option,预设置 Disabled,建议值 Disabled,Always每次开机均必须输入密码,否则无法开机,Setup如果要进入BIOS才需输入密码,可避免微机的设置被人乱改Disabled不设置密码,输入密码时严格区分大小写字母,如果不慎遗忘密码,可使用万能密钥AMI 芯片组使用AMI旧 Award 芯片组使用 Award,新Award 芯片组使用 Syxz。

西工大数字电路试验报告——试验五

实验五:计数器及其应用实验目的:1.熟悉常用中规模计数器的逻辑功能。

2.掌握二进制计数器和十进制计数器的工作原理和使用方法。

3.运用集成计数器构成1/N 分频器。

实验设备:数字电路试验箱,数字双踪示波器,函数信号发生器, 74LS90 及 Multisim 仿真软件。

实验原理:计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。

计数器按计数进制有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆 (双向)计数器等。

目前, TTL和 CMOS电路中计数器的种类很多,大多数都具有清零和预置功能,使用者根据器件手册就能正确地运用这些器件。

实验中用到异步清零二-五-十进制异步计数器 74LS90。

74LS90 是一块二 -五-十进制异步计数器,外形为双列直插,引脚排列如图(1) 所示,逻辑符号如图( 2)所示,图中的 NC 表示此脚为空脚,不接线,它由四个主从JK 触发器和一些附加门电路组成,其中一个触发器构成一位二进制计数器;另三个触发器RR 构成异步五进制计数器。

在 74LS90计数器电路中,设有专用置“ 0”端0(1)、0(2)和置“9”端S9(1)、S9(2)。

其中R0(1)、R0(2)为两个异步清零端,S9(1)、S9(2)为两个异步置 9 端, CP1、CP2为两个时钟输入端, Q0~Q3为计数输出端, 74LS90的功能表见表 (1),由此可知:当 R1=R2=S1=S2=0时,时钟从 CP1引入, Q0 输出为二进制;时钟从 CP2 引入, Q3 输出为五进制;时钟从 CP1 引入,而 Q0 接 CP2 ,即二进制的输出与五进制的输入相连,则 Q3Q2Q1Q0 输出为十进制( 8421BCD 码);时钟从 CP2引入,而 Q3 接 CP1 ,即五进制的输出与二进制的输入相连,则 Q0Q1Q2Q3 输出为十进制 ( 5421BCD码)。

模拟coms实验报告

模拟cmos集成电路课程实验报告反相器原理图设计专业班级姓名指导老师报告时间一.实验目的1 学会创建模型库和单元视图2 了解schematic 设计环境3 学会如何画反相器原理图二.实验内容和步骤1 调用 candence 软件运行虚拟机直接点击三角形运行的图标然后输入icfb命令调用 candence软件,此时会弹出CIW窗口2 创建工作路径库与单元视图进入candence后点击CIW窗口的 file—new—library,此时弹出对话窗口如图Name栏输入库文件名mylib(可以自定义),右侧 Technology File栏选择第二个。

点击OK弹出窗口如3-3,这时让你选择工艺库的我们选择 sto2 这个工艺库点击OK弹出窗口中在library中可以看到我们自己建的模型库 mylib3 画原理图⑴画原理图之前先了解以下几个快捷键i----插入元器件w----连线p----插入输入输出引脚q----查看器件属性f----调节合适的窗口c----复制u----撤销m----移动器件del----删除⑵添加元件n管p管的添加在Schematic Editing窗口中按下快捷键 i 点击Browse弹出Library Browse 窗口然后按图击个个选项然后点击Close,此时又弹出对 p管属性设置的窗口如图,这里 Total Width 设为1.4uM其它不变。

点击Hide此时鼠标箭头上就有了p管的symbol, n管的插入和p管类似,只需把n管的Length改为550Nm⑶添加vdd和gnd按下i点击Browse 弹出Library Browse窗口然后按图点击个个选项然后点击Close,在弹出的窗口点击Hide此时鼠标箭头上就有了 vdd的 symbol, gnd 的插入和 vdd类似。

⑷添加输入输出引脚按下p弹出窗口,在Pin Names 栏填 in,Direction栏选择input点击Hide 此时鼠标箭头上就有了输入的symbol,输出的添加和此类似只需把Direction 栏选择output,到此所有元件添加完成。

西工大数电实验报告实验一2020最新版

4

QuartusII原理图: (3)波形仿真:

数字电子技术实验

(4)记录电路输出结果

ABY 000 010 100 111

3、(要求三)用与非门实现“或”逻辑。用 MULTISIM 软件仿真后,用 FPGA 实 现电路测试逻辑功能。 (1)逻辑表达式变换过程: Y A B A·B (2)原理图(Multisim和QuartusII中绘制的原理图): Multisim原理图:

QuartusII原理图:

6

数字电子技术实验

(3)波形仿真:

(4)记录电路输出结果

ABY 000 011 101 110

5、(要求五)用门电路设计实现一位全加器,用 MULTISIM 软件仿真后,用 FPGA 实现电路测试逻辑功能。 (1)全加器的真值表:

A B C S C0 0 0 000 0 0 110 0 1 010 0 1 101 1 0 010 1 0 101 1 1 001 1 1 111

三、实验设备

(1)电脑一台; (2)数字电路实验箱; (3)数据线一根。

2

四、实验原理

要求 1: 要求 2: 要求 3:

要求 4: 要求 5:

数字电子技术实验

五、实验内容

1、(要求一)测试与非门逻辑功能。用 MULTISIM 软件仿真后,用 FPGA 实现 电路测试逻辑功能。

3

数字电子技术实验

(1)逻辑表达式变换过程:Y=(A·B)'=A'+B' (2)原理图(Multisim和QuartusII中绘制的原理图):

Multisim原理图:

QuartusII原理图:

(3)波形仿真:

(4)记录电路输出结果

ABY 001 011 101 110

西工大数字电路实验报告——实验六

实验六:计数器及其应用一.实验目的:1. 熟悉常用中规模计数器的逻辑功能。

2. 掌握时序电路一般设计方法。

3. 能够应用时序电路解决实际问题。

二.实验设备:数字电路试验箱,数字双踪示波器,函数信号发生器,74LS161,,74LS00及Multisim 仿真软件。

三. 实验原理:计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。

计数器按计数进制有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。

目前,TTL 和CMOS 电路中计数器的种类很多,大多数都具有清零和预置功能,使用者根据器件手册就能正确地运用这些器件。

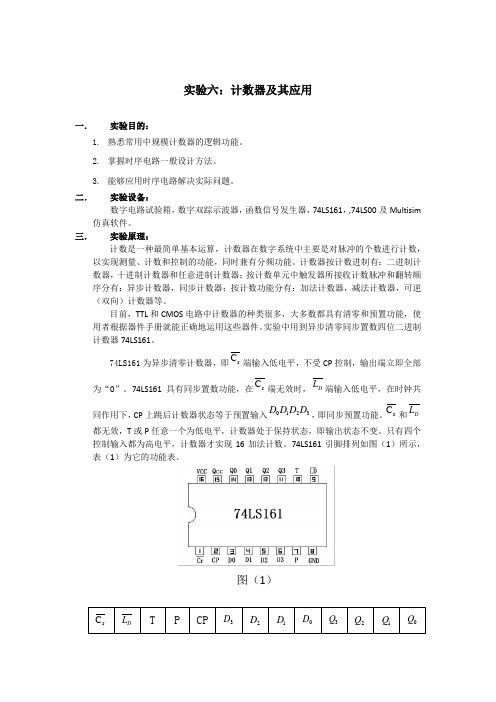

实验中用到异步清零同步置数四位二进制计数器74LS161。

74LS161为异步清零计数器,即端输入低电平,不受CP 控制,输出端立即全部为“0”。

74LS161具有同步置数功能,在端无效时,端输入低电平,在时钟共同作用下,CP 上跳后计数器状态等于预置输入,即同步预置功能。

和都无效,T 或P 任意一个为低电平,计数器处于保持状态,即输出状态不变。

只有四个控制输入都为高电平,计数器才实现16加法计数。

74LS161引脚排列如图(1)所示,表(1)为它的功能表。

图(1)r C r C D L 3210D D D D r C DL1 0 ↑ D C B A1 01 01 1 1 ↑表(1)四.实验内容:1.用74LS161和74LS00实现两种置数方式的十进制计数。

(1)异步置数法:利用芯片的预置功能,可以实现M=10进制计数器,M=16-N=10,其中N=6(二进制为0110)为预置数。

将0110送到输入端D3D2D1D0,计数器开始从0110开始计数,在CP脉冲下一直计数到1111,此时,从进位端Qc输出1,经非门送到Ld端,呈置数状态。

西工大机电学院上机实习实验报告

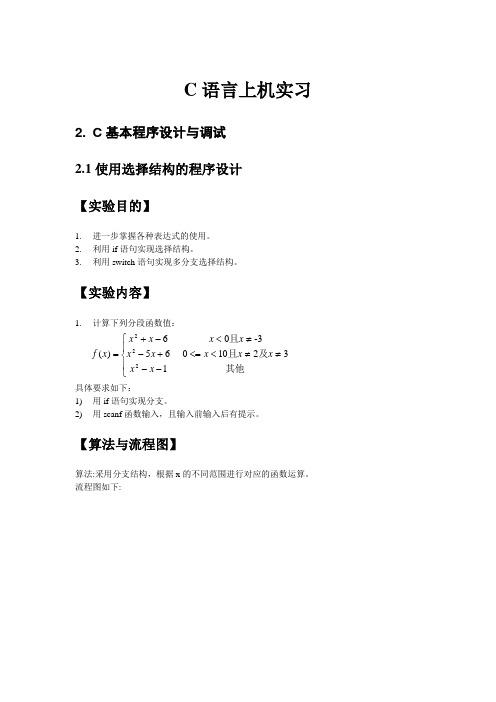

C 语言上机实习2. C 基本程序设计与调试 2.1使用选择结构的程序设计 【实验目的】1. 进一步掌握各种表达式的使用。

2. 利用if 语句实现选择结构。

3. 利用switch 语句实现多分支选择结构。

【实验内容】1. 计算下列分段函数值:其他及且且321003-01656)(222≠≠<<=≠<⎪⎩⎪⎨⎧--+--+=x x x x x x x x x x x x f具体要求如下:1) 用if 语句实现分支。

2) 用scanf 函数输入,且输入前输入后有提示。

【算法与流程图】算法:采用分支结构,根据x 的不同范围进行对应的函数运算。

流程图如下:开始x<0且x ≠-30<=x<10且x ≠3及x ≠2f(x)=x²+x-6f(x)=x²-5x+6f(x)=x²-x-1输出F(x)结束输入x否是否是【程序清单】#include <stdio.h> int main() { float x,y; printf("x="); scanf("%f",&x);if ((x<0)&&(x!=-3)){y=x*x+x-6;}else if ((x>=0)&&(x<10)&&(x!=2)&&(x!=3)){y=x*x-5*x+6;}elsey=x*x-x-1;printf("f(x)=%f",y);}【运行结果】【调试分析和体会】题目考查了选择结构分支语句。

2.2循环结构的程序设计【实验目的】1.进一步练习选择结构的程序设计及实现循环结构的三种方法。

2.练习并掌握选择结构与循环结构的嵌套,调试与修改程序。

【实验内容】1.计算并输出500以内最大的10个素数及其之和。

具体要求如下:1)输出要有文字说说明,并同时输出各素数。

西工大计算机实习报告

西⼯⼤计算机实习报告计算机实习报告⼀、趣味题彩⾊的圆环:分析图形可知,⼀共有n个同⼼圆,外⾯⼤圆n等分,然后从每个等分点作所有同⼼圆的两条切线。

如果⽤极坐标表⽰,可以很容易求解切点,代码如下所⽰:n=10; %同⼼圆数量m=40; %等分点数R=1; %外圆半径s=0:0.01*pi:2*pi; %控制圆的光滑程度的极坐标⾓度t=0:2*pi/m:2*pi; %等分点极坐标⾓度x0=R*cos(t);y0=R*sin(t); %等分点直⾓坐标color=['b','r','c','g','m','y']; %画图颜⾊lc=length(color); %颜⾊数量长度,超出后从头开始for i=1:n %开始同⼼圆循环r=R/n*i; %当前同⼼圆半径a=acos(r/R); %切线与圆⼼线⾓度(弧度制)x1=r*cos(t-a);y1=r*sin(t-a); %任意等分点相对当前同⼼圆的第⼀个切点x2=r*cos(t+a);y2=r*sin(t+a); %任意等分点相对当前同⼼圆的第⼆个切点plot(r*cos(s),r*sin(s),color(mod(i,lc)+1));hold on; %画同⼼圆for j=1:m %对每⼀个等分点循环plot([x0(j),x1(j)],[y0(j),y1(j)],color(mod(i,lc)+1));hold on;%第⼀条切线plot([x0(j),x2(j)],[y0(j),y2(j)],color(mod(i,lc)+1)); hold on; %第⼆条切线endendaxsi equal; %横纵坐标⽐例⼀致实验绘图结果如下图所⽰:⼆、算法题求⽆向图的最短路径(Dijkstra算法):实验原理分析、原理及代码如下所⽰(此实验代码不仅包含了实验所要求的求带权⽆向图最短路径,我还拓展了求有向、⽆向、带权有向图最短路径的内容):#include#includeusing namespace std;#define wuqiong 0class tu{public:int chazhao(int);//查找void zjdingdian(int x);//增加顶点tu();void zengjia();//控制增加弧边和点void zjhubian();//增加弧边void bianli();//控制遍历void shendu(int );//深度void guangdu(int );//⼴度void jindui(int );//进队列int chudui();//出对了bool pankong();//判空//上⾯所有的函数与邻接矩阵有关void zxgouzao();//初始化与最⼩路劲有关的东东void zxshuchu();//求S中的最⼩路劲private: int kind; //类图;int length; // 顶点个数int *dingdian; //顶点int *juzhen; //矩阵int num;//最⼤顶点数⽬int* visted;//访问情况int *duilie;//模拟队列int duichang;//队列长度//上⾯所有的变量与邻接矩阵有关int *s;//存放当前顶点int slength;//当前顶点的长度int* dist;//存放最⼩路劲int* pre;//存放路劲;int* final;//存放顶点};tu::tu()//初始化图{cout<<"请输⼊图的种类1:有向.2:⽆向.3:带权有向.4:带权⽆向"<>kind;cout<<"请输⼊图的顶点数⽬"<cin>>num;dingdian = new int[num];//为顶点分配内存保存juzhen = new int[num*num];//产⽣矩阵if(kind==1||kind==2)//为⽆权图初始化矩阵{for(int i =0;ijuzhen[i] = 0;}else//有权图初始化矩阵{for(int i =0;ijuzhen[i] = wuqiong;}length = 0;}//增加顶点void tu::zjdingdian(int x){if(chazhao(x)!=-1||length==num)cout<<"图内有此顶点或图内⽆空间可插⼊,插⼊失败"< else{dingdian[length] = x;length++;}}//增加边void tu::zjhubian(){int i;//弧头int j;//弧尾if(kind==1||kind==2)//⽆权图{cout<<"请输⼊弧的头和尾"<cin>>i>>j;if(kind == 1)//有向图{juzhen[i*num+j]=1;}else//⽆向图,两边同时取值{juzhen[i*num+j]=1;juzhen[j*num+i]=1;}}else//权值,同上,将1改为K(权值)即可{int k;cin>>i>>j>>k;if(kind == 3){juzhen[i*num+j]=k;}else{juzhen[i*num+j]=k;juzhen[j*num+i]=k;}}}//查找,将该数所在位置返回,若⽆则返回-1 int tu::chazhao(int x){for(int i =0;iif(x == i)return i;return -1;}//控制遍历函数void tu::bianli()//遍历函数{cout<<"该图的邻接矩阵为:";int i;int j;for(i =0;i{cout<for(j=0;jcout<}cout<visted = new int[length];//为设置访问状态定义内存空间cout<<"深度搜索:";for(i =0;ishendu(0);//将0作为0点运⽤深度访问函数cout<cout<<"⼴度搜索:";for(i =0;ivisted[i]=0;duilie = new int[length+1];duilie[0]=-1;//队列初始化duichang = 0;guangdu(0);//将0作为0点运⽤⼴度访问函数}//深度遍历void tu::shendu(int x)//采⽤递归的⼿法{int p;visted[x] = 1;//访问后置1防⽌重复访问cout<p = x*length+1;while(p%length!=0){if(juzhen[p]!=0&&visted[p%length]!=1) shendu(p%length);}}//⼴度遍历void tu::guangdu(int x){int p;visted[x] = 1;cout<p = length*x+1;while(p%length!=0)//没有遍历属于根节点的后代的所有兄弟结点加⼊到队列中(这样可以先进先出,后来的⼦代加⼊后也是先输出⽗亲结点){if(juzhen[p]!=0&&visted[p%length]!=1){visted[p%length] = 1;//判断是否已经加⼊队列或访问jindui(p%length);}p++;//进⾏下⼀个判断}while(pankong())//加⼊所有的⼦代兄弟节点后现在出队列并且访问,访问的⽅式⼀致会访问后优先加⼊其⼦代结点然后出队列访问{guangdu(chudui());}}//进队列,在队头插⼊⼀个函数,这个出队⼊队为了⼴度输出void tu::jindui(int x){duilie[duichang+1] = -1;duilie[duichang] = x;duichang++;}//出队列,将队列中的最后⼀个数返回int tu::chudui(){j = duilie[0];for(int i=0;iduilie[i] = duilie[i+1];duichang--;return j;}//判空函数,函数为空的时候返回0bool tu::pankong(){if(duichang == 0)return false;elsereturn true;}//控制增加函数void tu::zengjia(){int j ;for(int i =0;izjdingdian(i);cout<<"请输⼊需要增加的弧数(最少"<>j;cout<<"请输⼊弧的头和尾和权值"<for(i=0;i{//cout<<"插⼊第"<zjhubian();}}/***算法思想:依次递增序列求出最⼩路劲,⾸先将顶点加⼊到S当中(本程序默认为0号顶点),然后⽤dist数组保存到每⼀个顶点的最⼩路径长度**dist起始为顶点到其他顶点的权值(到⾃⾝为0,到⽆弧顶点为⽆穷⼤)**1:然后每次取v0-vk(k属于V-S)最⼩的路劲长度,取完之后将Vk加⼊S当中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

模拟CMOS集成电路实验一一、PPT示例执行示例中的仿真程序,给出仿真结果。

并在NMOS的栅源电压为1.2V时,PMOS源栅电压等于1.2V时,分别仿真得出二者漏电流特性曲线。

这种情况下,手工计算出对于NMOS,当VDS=1V时漏电流、跨导的值;对于PMOS VSD=1V 时漏电流、跨导的值。

并与仿真结果比较。

沟道长度设置为1u,观察器件的漏电流有怎样的变化?A.示例MOS管IV 漏电流特性曲线1. Hspice仿真SP文件如下:.title MOS IV characters**************model NMOS************************.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************.MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)**************************************************************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5uM2 DP GP SP BP PMOS W=1u L=0.5u**************source****************************VDSN DN SN 0VGSN GN SN 0VSN SN 0 0VBN BN 0 0VSDP SP DP 0VSGP SP GP 0VSP SP 0 3.3VBP BP 0 3.3**************analysis**************************.DC VDSN 0 3.3 0.05 sweep VGSN 0 3 0.5.DC VSDP 3.3 0 0.05 sweep VGSN 0 3 0.5.probe i(M1) i(M2) lx7(M1) lx7(M2) .end2.仿真图B. NMOS的栅源电压为1.2V,PMOS源栅电压等于1.2V, 漏电流特性曲线1. Hspice仿真SP文件.title MOS IV characters**************model NMOS************************.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************.MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)**************************************************************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5uM2 DP GP SP BP PMOS W=1u L=0.5u**************source****************************VDSN DN SN 0VGSN GN SN 1.2VSN SN 0 0VBN BN 0 0VSDP SP DP 0VSGP SP GP 1.2VSP SP 0 3.3VBP BP 0 3.3**************analysis**************************.DC VDSN 0 3.3 0.05.DC VSDP 3.3 0 0.05.probe i(M1) i(M2).end2.仿真图3.手工计算与分析○1对于NMOS :7.0,350u 9.02,45.01.00=====TH n F V ,,φγλ当GS V =1.2V ,DS V =1V 时,NMOS 工作在饱和区,则有:21()(1)2'D n OX GS TH DS W I C V V V L μλ=-+ ()2mNMOS n OX GS TH n NMOS W W g C V V I L L μμ=-=其中:TH V =FSB F TH V V φφγ220-++ 代入参数可计算得:454.32.1710NMOS mNMOS I A g S μ-=⎧⎨=⨯⎩○2对于PMOS :8.0,8.02,4.0,100u 2.00-=====TH F p V φγλ, SG V =1.2V,SD V =1V 时,PMOS 工作在饱和区,则:()20.5(1)PMOS p OX GS TH DS W I C V V V L μλ=--+()2mPMOS p OX GS TH p PMOS W W g C V V I L L μμ=-=代入参数计算可得:511.55.7610PMOS mNMOS I A g Sμ-=-⎧⎨=⨯⎩C.沟道长度设置为1u, 漏电流特性曲线二、课本习题2.5a.图略1.手工计算与分析:λ=0.1,γ=0.45, 2F φ=0.9,0TH V =0.7V GS =3-x V ,V DS =3-x V ,V SB =x V ,TH V =F SB F TH V V φφγ220-++①当0)9.09.0(45.07.03>-+---=-X X TH G S V V V V 时,即X V <1.97时,M1工作在饱和区:DS TH GS ox n X V V V LW C I )1()(u 212λ+-=)1.13.3()9.09.045.03.2(u 212X X X ox n V V V LW C --+--= g m =D oxn I L W C u 2=x ox n I L W C u 2 ○2 x V >1.97时, M1管将处于截止状态;x I =0; m g =0。

2.分析草图:3.Hspice 仿真SP 文件.title MOS IV characters**************model NMOS************************ .MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1 +TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2 +TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)**************************************************************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5u**************source*****************VDN DN 0 3VGN GN 0 3VSN SN 0 0VBN BN 0 0**************analysis******************.DC VSN 0 1.5 0.05.probe i(M1) lx7(M1).end4.仿真图b .图略1.手工计算与分析λ=0.1,γ=0.45, 2F φ=0.9,0TH V =0.7○1 当1X V V <时,源漏颠倒,M1管工作在线性区,则有: 1.9GS X V V =-;1DS X V V =-21[2()]2X n ox GS TH DS DS W I C V V V V Lμ=---])1()1)(2.1(2[u 212X X X ox n V V V L W C -----=)4.1)(1(u 21X X ox n V V L W C ---= (1)X m n ox X GS I W g C V V Lμ∂==-∂ ○2 当 1 1.2X V V V <<时, M1管工作在线性区,则有:1DS X S X V V V V =-=-;V V GS 9.019.1=-=2211[()][0.4(1)(1)]22X n ox GS TH DS DS n ox X X W W I u C V V V V u C V V L L=--=--- 21{[()]}(1)2m n ox GS TH DS DS n ox DS n ox X GS W W W g u C V V V V u C V u C V V L L L ∂=--==-∂ ○3 当 1.2V V ≥时,M1管工作在饱和区,则: 21()0.022X n ox GS TH n ox W W I u C V V u C L L=-= ()0.2m n ox GS TH n ox W W g u C V V u C L L=-=2.分析草图3.Hspice仿真.title MOS IV characters**************model NMOS************************ .MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1 +TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2 +TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ **************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5u*****************source*****************VDN DN 0 0VGN GN 0 1.9VSN SN 0 1VBN BN 0 0******************analysis******************.DC VDN 0 3 0.05.probe i(M1) lx7(M1).end4.仿真图仿真图与分析草图出现差异,原因在于:当考虑衬底偏置效应时,当1>X V 时,γ=0.45, 2F φ=0.9,0TH V =0.7, TH V =F SB F TH V V φφγ220-++V 89.0)9.019.0(45.07.0=-++= 则有:0=X I 0g =m ,波形如下图所示:c.图略1.手工计算与分析λ=0.1,γ=0.45, 2F φ=0.9,0TH V =0.7○1 当x V <0.3V 时,源漏倒置,M1管工作在饱和区,则: 1; 1.9GS X DS X V V V V =-=-;2211()(0.3)22X n ox GS TH n ox X W W I u C V V u C V L L =--=--)3.0()3.0(-u =g n -=-x ox n x ox m V L W C u V L W C○2当 0.3X V V >时,M1将处于截止状态; x I =0, m g =0.2.分析草图3.Hspice 仿真SP 文件.title MOS IV characters**************model NMOS************************.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************.MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2 +TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ **************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5u*****************source*****************VDN DN 0 0VGN GN 0 1VSN SN 0 1.9VBN BN 0 0******************analysis******************.DC VDN 0 3 0.05.probe i(M1) lx7(M1).end4.仿真图d.图略1.手工计算与分析8.0,8.02,4.0,2.00-====TH F V φγλ①当8.10<<X V V 时,源漏倒置,M2管工作在饱和区,则:0.9; 1.9GS DS X V V V V =-=-210.01()22X p ox GS TH p ox W W I u C V V u C L L=--=- ()0.1m p ox GS TH p ox W W g u C V V u C L L=--=- ②.当V V V X 9.18.1<<时,M2管进入线性区,则:0.9; 1.9GS DS X V V V V =-=-2211[2()][0.2( 1.9)( 1.9)]22X p ox GS TH DS DS p ox X X W W I u C V V V V u C V V L L=---=----( 1.9)X m p ox DS p ox X GS I W W g u C V u C V V L L ∂===-∂③时,当V V V X 39.1<<M2管工作在线性区,则: XD S X G S V V V V -=-=9.1,12211[2()][2(1.8)(1.9)(1.9)]22X p ox GS TH DS DS p ox X X X W W I u C V V V V u C V V V L L=--=----(1.9)X m p ox DS p ox X GS I W W g u C V u C V V L L ∂==-=--∂)9.1(ox -=X p V L W C u2..分析草图3. Hspice仿真SP文件.title MOS IV characters**************model NMOS************************ .MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1 +TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2 +TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ **************netlist***************************M2 DP GP SP BP PMOS W=1u L=0.5u*****************source*****************VSP SP 0 0VGP GP 0 1VDP DP 0 1.9VBP BP 0 3******************analysis******************.DC VSP 0 3 0.05.probe i(M2) lx7(M2).end4.仿真图e.图略1.手工计算与分析λ=0.1,γ=0.45, 2F φ=0.9,0TH V =0.70.5DS V =,0.9GS V =,1SB X V V =-=TH V F SB F TH V V φφγ220-++)9.0|9.1|(45.07.0--+=X V ○1 )9.0|9.1|(45.02.0---=-≥X TH G S D S V V V V 时,即 1.82X V V ≤, M1管工作在饱和区;2211()[0.20.45(|1.9|0.9)]22X n ox GS TH n ox X W W I u C V V u C V L L=-=--- ()[0.20.45(|1.9|0.9)]m n ox GS TH n ox X W W g u C V V u C V L L=-=--- ○2 0.20.45(|1.9|0.9)D S G S T H X V V V V <-=---时, 1.82X V V >,M1管工作在线性区;211[2()][0.050.45(|1.9|0.9)]22X n ox GS TH DS DS n ox X W W I u C V V V V u C V L L=--=-+--12X m n ox DS n ox GS I W W g u C V u C V L L∂===∂ 2.分析草图3. Hspice 仿真SP 文件.title MOS IV characters**************model NMOS************************ .MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)**************************************************************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5u*****************source***************** VDN DN 0 1.5VGN GN 0 1.9VSN SN 0 1VBN BN 0 0******************analysis****************** .DC VBN 0 3 0.05.probe i(M1) lx7(M1).end4.仿真图。