西工大-数电实验-第二次实验-实验报告

数字电路实验二实验报告

实验二门电路逻辑变换一.实验目的1 学会门电路逻辑变换的基本方法。

2 掌握虚拟实验逻辑转换器的使用方法。

二.实验设备安装有Multsim10软件的个人电脑。

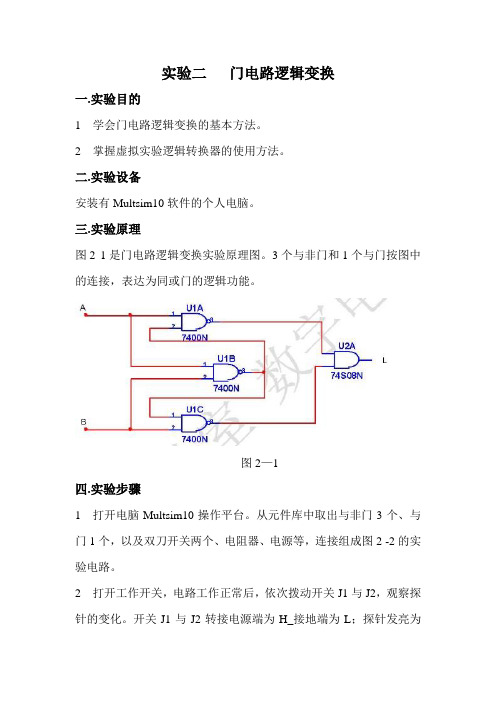

三.实验原理图2 1是门电路逻辑变换实验原理图。

3个与非门和1个与门按图中的连接,表达为同或门的逻辑功能。

图2—1四.实验步骤1 打开电脑Multsim10操作平台。

从元件库中取出与非门3个、与门1个,以及双刀开关两个、电阻器、电源等,连接组成图2 -2的实验电路。

2 打开工作开关,电路工作正常后,依次拨动开关J1与J2,观察探针的变化。

开关J1与J2转接电源端为H_接地端为L;探针发亮为H_熄灭为L,将观察结果填入表2- 1。

表2-1J1 J2 探针L L HL H LH L LH H H图2—21)J1接电源,J2接地2)J1接地,J2接电源3)J1接地,J2接地4)J1接电源,J2接电源3将表2- 1变换为如下表2-2的真值表。

开关J1为A,J2为B,H为“1”,L为“0”;探针x1为F发亮为“1”,熄灭为“0”。

表2-2A B F0 0 10 1 01 0 01 1 14 按上述图2-2写出逻辑表达式为BAF,根据真值表及=BA∙+∙逻辑表达式判断,它是一个同或门电路。

5 逻辑转换器的使用重新设置Multisim仿真工作界面,运用逻辑转换器,转换出逻辑表达式为BF+=的门电路逻辑图,然后配置开关、探针等,并将电ABA路仿真运转验证,列出实验验证结果(例如上述表2-1)。

应注意,在逻辑转换器中,逻辑表达式有不同,要用“’”表示求反,例如用A’来表示A的求反即A,其它类似。

1)点击simulate-----instruments------logic converter,打开逻辑转换仪。

2)设计出逻辑函数表达式为:B=,如图1所示。

F+ABA3)点击右边第五个图标,把逻辑表达式转换为与,或非门电路,如图2所示。

4)点击右边第六个图标,把逻辑表达式转换为与非门电路,如图3所示。

新版西电微机原理第二次上机实验报告-新版-精选.pdf

西电微机原理第二次上机实验报告学号:姓名:一、实验目的1.熟练掌握汇编语言程序设计的方法及上机步骤。

2.掌握算术运算中,十进制数调整指令的应用。

3.掌握子程序的设计方法。

4.掌握DOS功能的调用方法。

二、实验仪器586微机 1台三、实验内容编写求十进制数12678532与21736543之和的程序,并将和以十进制数的形式送屏幕显示。

编程要求与提示:[1] 两个加数均以压缩(组合)十进制数形式存放在ADD1和ADD2为首址的存贮器单元。

[2] 和以压缩十进制数的形式存入SUM以下单元。

[3] 将和送到屏幕显示部分功能的实现采用子程序的形式。

[4] 实验步骤如下:a. 用全屏幕编辑软件建立源程序。

b.用masm.exe汇编程序对源程序进行汇编,形成目标程序。

c. 用link.exe连接程序对目标程序进行连接形成可执行文件。

d. 用DEBUG对连接通过的可执行程序进行调试。

四、实验内容对应的源程序及流程源程序如下:STACK SEGMENT STACKDB 10H DUP(00)STACK ENDSDATA SEGMENTADD1 DB 12H,67H,85H,32HADD2 DB 21H,73H,65H,43HSUM DB 4H DUP(?)DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,ES:DATA,SS:STACKSTART:MOV AX, DATAMOV DS, AXMOV AX, DATAMOV ES, AXMOV AX,STACKMOV SS,AXLEA SI, ADD1[3]LEA BX, ADD2[3]LEA DI,SUM[3]MOV CX,4CLCL1:MOV AL,[SI]ADC AL,[BX]DAAMOV [DI],ALDEC SIDEC BXDEC DILOOP L1CALL DISPAL; ------------EXITPROC:MOV AH,4CH ;结束程序MOV AH,1INT 21H; ------------DISPAL PROC NEARPUSH AXPUSH BXPUSH CXPUSH DXPUSH DILEA DI,SUMMOV CX,4DISPAL2:MOV AL,[DI]SHR AL,1SHR AL,1SHR AL,1SHR AL,1MOV AH,2MOV DL,ALADD DL,30HINT 21HMOV AL,[DI]AND AL,0FHMOV AH,2MOV DL,ALADD DL,30HINT 21HINC DILOOP DISPAL2POP DIPOP DXPOP CXPOP BXPOP AXRETDISPAL ENDPCODE ENDSEND START运行结果如下:五、问题讨论1.在以十进制数形式参加运算的程序设计中,应注意那些问题。

数电实验报告实验

一、实验目的1. 理解和掌握数字电路的基本原理和设计方法。

2. 培养动手能力和实验技能。

3. 提高分析问题和解决问题的能力。

二、实验原理数字电路是一种以二进制为基础的电路,其基本元件是逻辑门和触发器。

本实验主要涉及以下几种逻辑门:与门、或门、非门、异或门、同或门、与非门、或非门等。

1. 与门(AND Gate):当所有输入端都为高电平时,输出才为高电平。

2. 或门(OR Gate):当至少一个输入端为高电平时,输出为高电平。

3. 非门(NOT Gate):对输入信号取反。

4. 异或门(XOR Gate):当输入端信号不同时,输出为高电平。

5. 同或门(NOR Gate):当输入端信号相同时,输出为高电平。

6. 与非门(NAND Gate):与门和非门的组合。

7. 或非门(NOR Gate):或门和非门的组合。

三、实验器材1. 数字电路实验箱2. 逻辑门芯片3. 电源4. 连接线5. 测试仪器四、实验步骤1. 组成基本逻辑门电路:根据实验原理,搭建与门、或门、非门、异或门、同或门、与非门、或非门等基本逻辑门电路。

2. 测试电路功能:使用测试仪器对搭建的电路进行测试,验证电路是否满足基本逻辑功能。

3. 组成组合逻辑电路:根据实验要求,搭建组合逻辑电路,如全加器、半加器、译码器、编码器等。

4. 测试组合逻辑电路:使用测试仪器对搭建的组合逻辑电路进行测试,验证电路是否满足设计要求。

5. 组成时序逻辑电路:根据实验要求,搭建时序逻辑电路,如触发器、计数器、寄存器等。

6. 测试时序逻辑电路:使用测试仪器对搭建的时序逻辑电路进行测试,验证电路是否满足设计要求。

五、实验结果与分析1. 基本逻辑门电路测试结果:根据测试数据,搭建的与门、或门、非门、异或门、同或门、与非门、或非门等基本逻辑门电路均满足设计要求。

2. 组合逻辑电路测试结果:根据测试数据,搭建的全加器、半加器、译码器、编码器等组合逻辑电路均满足设计要求。

西工大_数电实验_第二次实验_实验报告

数电实验2一.实验目的1.学习并掌握硬件描述语言(VHDL 或 Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。

2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求1:编写一个异或门逻辑电路,编译程序如下。

1)用 QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:编写一个将二进制码转换成 0-F 的七段码译码器。

1)用 QuartusII 波形仿真验证;2)下载到 DE0 开发板,利用开发板上的数码管验证。

要求3:编写一个计数器。

1)用QuartusII 波形仿真验证;2)下载到 DE0 开发板验证。

要求4:编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz。

1)下载到 DE0 开发板验证。

(提示:利用 DE0 板上已有的 50M 晶振作为输入信号,通过开发板上两个的 LED 灯观察输出信号)。

2)电路框图如下:扩展内容:利用已经实现的 VHDL 模块文件,采用原理图方法,实现 0-F 计数自动循环显示,频率 10Hz。

(提示:如何将 VHDL 模块文件在逻辑原理图中应用,参考参考内容 5)四.实验原理1.实验1实现异或门逻辑电路,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EXORGATE ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END EXORGATE;ARCHITECTURE fwm OF EXORGATE ISBEGINC<=A XOR B;END;2.实验2实现一个将二进制码转换成0-F的七段译码器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevendecoder ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevendecoder;ARCHITECTURE fwm OF sevendecoder ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示 0WHEN"0001"=>dis_out<="1111001";--显示 1WHEN"0010"=>dis_out<="0100100";--显示 2WHEN"0011"=>dis_out<="0110000";--显示 3WHEN"0100"=>dis_out<="0011001";--显示 4WHEN"0101"=>dis_out<="0010010";--显示 5WHEN"0110"=>dis_out<="0000010";--显示 6WHEN"0111"=>dis_out<="1111000";--显示 7WHEN"1000"=>dis_out<="0000000";--显示 8WHEN"1001"=>dis_out<="0010000";--显示 9WHEN"1010"=>dis_out<="0001000";--显示 AWHEN"1011"=>dis_out<="0000011";--显示 bWHEN"1100"=>dis_out<="1000110";--显示 CWHEN"1101"=>dis_out<="0100001";--显示 dWHEN"1110"=>dis_out<="0000110";--显示 EWHEN"1111"=>dis_out<="0001110";--显示 FWHEN OTHERS=> dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;3.实验3完成一个计数器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT ( clk,RST : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); --四位计数COUT : OUT STD_LOGIC); --进位位END counter;ARCHITECTURE fwm OF counter ISSIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINPROCESS(clk,RST)BEGINIF RST = '0' THEN Q1<=(OTHERS => '0'); COUT<= '0';ELSIF clk'EVENT AND clk='1' THENQ1<=Q1+1;COUT<= '0';IF Q1 >= "1001" THEN Q1<=(OTHERS => '0'); COUT<= '1';END IF;END IF;END PROCESS;DOUT<=Q1 ;END fwm;4.实验4编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fpq ISPORT(clk:IN STD_LOGIC;clk_out,clk_out1:OUT STD_LOGIC);END fpq;ARCHITECTURE fwm OF fpq ISCONSTANT m : INTEGER:= 25000000; --50M 分频到 1Hz 时=25000000。

西工大模电实验实验二:集成运算放大器

集成运算放大器

一、实验目的

(1)了解并掌握由运算放大器组成的比例、加法、减法和积分等基本运算电路的功能。

(2)掌握集成运算放大器的基本应用,为综合应用奠定基础。

(3)进一步熟悉仿真软件的使用。

二、实验原理

集成运放是一种具有高电压放大倍数的直接耦合器件。

当外部接入有不同的线性或非线性元器件组成的输入负反馈电路时,可以灵活的实现各种函数关系,在线性应用方面,可组成加法、减法、比例。

积分、微分、对数等模拟运算电路。

在大多数情况下,将运放视为理想的,即在一般讨论中,以下三条基本结论是普遍使用的:

1)开环电压增益∞=u A

2)运放的两个输入端电压近似相等,即-V V =+,称为“虚短”。

3)运放的同相和反相两个输入端的电流可视为零,即0I I -==+,称为“虚断”。

应用理想运放的三条基本原则,可简化运放电路计算,得出本次实验结论。

三、实验内容及步骤(一)计算机仿真

【减法电路】

【加法电路】

(二)实验室操作部分

实验硬件电路图及示波器结果图示:1.反向比例运算电路:

2.加法电路:

3.减法电路

四、实验分析

(1)误差分析:本次试验结果接近理论值,误差很小,主要由于仿真计算和电阻的误差所致,较好地完成实验。

(2)实验中的思考:1.如果输入三角波,根据数学积分结果是一个抛物线,进行仿真

得到相似的结果。

2.如果反向加法电路均输入正弦波,当满足下述条件时候,才能

得到稳定的正弦波:净输入的两种正弦波在相位上要满足

φA-φB=2nπ

3.注意集成块的针脚位置与方向,注意电流大小。

西北工业大学数电实验报告1

实验1 TTL集成逻辑门参数测试学号:姓名:日期:组号:一、实验目的:(1)加深了解TTL逻辑门的参数意义。

(2)掌握TTL逻辑门电路的主要参数及测量方法。

(3)认识各种电路及掌握空闲端处理方法。

二、实验设备:数字电路实验箱,数字双踪示波器,函数信号发生器,数字万用表,74LS00,电位器,电阻。

三、实验原理:门电路是数字逻辑电路的基本组成单元,目前使用最普遍的双极型数字集成电路是TTL 逻辑门电路。

TTL集成电路的使用规则:(1)插集成块时,要认清定位标记,不得插反。

(2)使用电源电压范围为+4.5V~+5.5V。

实验中要求使用Vcc=+5V。

电源极性不允许接错。

(3)空闲输入端处理方法。

悬空,相当于正逻辑“1”,一般小规模集成电路的数据输入端允许悬空处理。

但易受外界干扰,导致电路逻辑功能不正常。

因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

(4)输入端通过电阻接地,电阻值的大小将直接影响电路所处状态。

(5)输出端不允许并联使用(三态门和OC门除外),否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

(6)输出端不允许直接接电源Vcc,不允许直接接地,否则会损坏器件。

四、实验内容:1、TTL信号的产生2、与非门的测试3、用74LS00实现逻辑函数:F=ABF=A+BF=A○+B五、实验结果:F=AB=AB∙1A∙∙B∙1F=A+B=1∙∙B∙ABF=A○+B=A AB。

西安工业大学模电仿真实验2实验报告

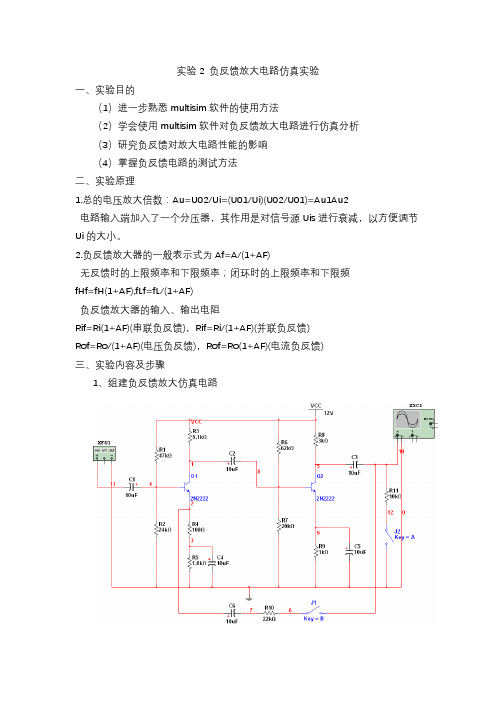

实验2 负反馈放大电路仿真实验一、实验目的(1)进一步熟悉multisim软件的使用方法(2)学会使用multisim软件对负反馈放大电路进行仿真分析(3)研究负反馈对放大电路性能的影响(4)掌握负反馈电路的测试方法二、实验原理1.总的电压放大倍数:Au=U02/Ui=(U01/Ui)(U02/U01)=Au1Au2电路输入端加入了一个分压器,其作用是对信号源Uis进行衰减,以方便调节Ui的大小。

2.负反馈放大器的一般表示式为Af=A/(1+AF)无反馈时的上限频率和下限频率;闭环时的上限频率和下限频fHf=fH(1+AF),fLf=fL/(1+AF)负反馈放大器的输入、输出电阻Rif=Ri(1+AF)(串联负反馈),Rif=Ri/(1+AF)(并联负反馈)Rof=Ro/(1+AF)(电压负反馈),Rof=Ro(1+AF)(电流负反馈)三、实验内容及步骤1、组建负反馈放大仿真电路2、静态工作点测试(1)输入1KHz,有效值1mV(或者峰值1.414vP)的正弦交流信号,用示波器监测电路开环、负载开路情况下的波形不失真。

波形图:(2)利用直流工作点分析法(DC Operating Point Analysis)来分析和计算电路Q点,分析数据并记录在表1中。

表1 静态工作点数据三极管Q1 三极管Q2V b(V))V c(V))V e(V) V b(V))V c(V))V e(V)8.52 1.42 0.75 8.08 3.37 2.683、负反馈放大电路开环、闭环放大倍数的测试调用示波器监测输出端波形,调用交流毫伏表(用万用表的交流档代替)测量表2中相关数据,并计算。

(1)开环电路测试(2)闭环电路测试(3)ΔA/A=(Auo-AuL)/Auo4、负反馈对放大电路的频率特性的影响(1)调出“波特分析仪”,并连入电路中。

(2)使用读数指针读出电路在开环、闭环下的上下限频率,将数据记录在表3中。

四、思考题试分析负反馈的引入对放大电路性能的影响?1. 增大Rp的电阻值,将使三极管的静态工作点下移,造成三极管对输入信号的下班波相应的动态范围不足,造成输出失真。

西工大 数字集成电路实验二、反相器(下)

数字集成电路实验报告西北工业大学2014年5月12日星期一实验二、反相器(下)三、分析如下电路,解答下面的问题。

上面的电路用两种方式实现了反相器。

左图只使用了NMOS,右图则使用了CMOS(NMOS 和PMOS)。

试完成:ΦF=‐0.3V1.仿真得到两个电路的VTC 图形黄色的线条表示的是第一个反相器的电压传输特性曲线,红色的线条表示的是第二个电压传输特性曲线。

2.计算两种电路的VOH,VOL及VM。

可参考波形确定管子的工作状态。

答:对于第一个电路构成的反相器而言当vin = 0的时候,M1截止,M2导通,输出电压vout = 2.5-0.43 = 2.07V 即 V V OH 07.2=当vin = 2.5V 的时候,M1、M2均导通,且M1处于线性区,M2处于饱和区(速度饱和),通过两个 管子的电流相等,所以有]2/)[()(]2/)[()(2111'222'DS DS TH GS M DSTA DSTA TH DD M DSAT V V V V L W K I V V V V L W K I -⨯-⨯⨯=-⨯-⨯⨯=由于存在体效应M2的阈值电压变为)22(0F SB F T T V V V φφγ-+-+= 其中out SB V V =解得=OL V 0.287V接着计算开关阈值M V ,此时,输入等于输出,判定M1与M2都处于饱和区。

]2/)[()(]2/)[()(2111'12222'2DSSAT DSAT TH GS M n D DSAT DSAT TH GS M n DSATM V V V V LW K I V V V V LW K I -⨯-⨯⨯=-⨯-⨯⨯= 而且OUT IN SB M V V V V ===求得V 995.0=M V而对于CMOS 反相器来说当vin = 0的时候,V V OH 5.2=当vin = 2.5V 的时候,0=OL V接着计算开关阈值M V ,此时,输入等于输出,判定M3与M4都处于饱和区。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数电实验2一.实验目的1.学习并掌握硬件描述语言(VHDL 或 Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。

2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求1:编写一个异或门逻辑电路,编译程序如下。

1)用 QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:编写一个将二进制码转换成 0-F 的七段码译码器。

1)用 QuartusII 波形仿真验证;2)下载到 DE0 开发板,利用开发板上的数码管验证。

要求3:编写一个计数器。

1)用QuartusII 波形仿真验证;2)下载到 DE0 开发板验证。

要求4:编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz。

1)下载到 DE0 开发板验证。

(提示:利用 DE0 板上已有的 50M 晶振作为输入信号,通过开发板上两个的 LED 灯观察输出信号)。

2)电路框图如下:扩展内容:利用已经实现的 VHDL 模块文件,采用原理图方法,实现 0-F 计数自动循环显示,频率 10Hz。

(提示:如何将 VHDL 模块文件在逻辑原理图中应用,参考参考内容 5)四.实验原理1.实验1实现异或门逻辑电路,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EXORGATE ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END EXORGATE;ARCHITECTURE fwm OF EXORGATE ISBEGINC<=A XOR B;END;2.实验2实现一个将二进制码转换成0-F的七段译码器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevendecoder ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevendecoder;ARCHITECTURE fwm OF sevendecoder ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示 0WHEN"0001"=>dis_out<="1111001";--显示 1WHEN"0010"=>dis_out<="0100100";--显示 2WHEN"0011"=>dis_out<="0110000";--显示 3WHEN"0100"=>dis_out<="0011001";--显示 4WHEN"0101"=>dis_out<="0010010";--显示 5WHEN"0110"=>dis_out<="0000010";--显示 6WHEN"0111"=>dis_out<="1111000";--显示 7WHEN"1000"=>dis_out<="0000000";--显示 8WHEN"1001"=>dis_out<="0010000";--显示 9WHEN"1010"=>dis_out<="0001000";--显示 AWHEN"1011"=>dis_out<="0000011";--显示 bWHEN"1100"=>dis_out<="1000110";--显示 CWHEN"1101"=>dis_out<="0100001";--显示 dWHEN"1110"=>dis_out<="0000110";--显示 EWHEN"1111"=>dis_out<="0001110";--显示 FWHEN OTHERS=> dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;3.实验3完成一个计数器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT ( clk,RST : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); --四位计数COUT : OUT STD_LOGIC); --进位位END counter;ARCHITECTURE fwm OF counter ISSIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINPROCESS(clk,RST)BEGINIF RST = '0' THEN Q1<=(OTHERS => '0'); COUT<= '0';ELSIF clk'EVENT AND clk='1' THENQ1<=Q1+1;COUT<= '0';IF Q1 >= "1001" THEN Q1<=(OTHERS => '0'); COUT<= '1';END IF;END IF;END PROCESS;DOUT<=Q1 ;END fwm;4.实验4编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fpq ISPORT(clk:IN STD_LOGIC;clk_out,clk_out1:OUT STD_LOGIC);END fpq;ARCHITECTURE fwm OF fpq ISCONSTANT m : INTEGER:= 25000000; --50M 分频到 1Hz 时=25000000。

CONSTANT m1 : INTEGER:= 2500000; --5M 分频到 10Hz 时=2500000。

SIGNAL tmp :STD_LOGIC;SIGNAL tmp1 :STD_LOGIC;BEGINPROCESS(clk, tmp)VARIABLE cout : INTEGER:=0;BEGINIF clk'EVENT AND clk='1' THENcout:=cout+1; --计数器+1IF cout<=m THEN tmp<='0'; --计数小于等于 25000000,输出 0ELSIF cout<m*2 THEN tmp<='1'; --计数小于 50000000,输出 1ELSE cout:=0; --计数器清零END IF;END IF;END PROCESS;clk_out<=tmp; --50M分频器输出PROCESS(clk, tmp1)VARIABLE cout1 : INTEGER:=0;BEGINIF clk'EVENT AND clk='1' THENcout1:=cout1+1; --计数器+1IF cout1<=m1 THEN tmp1<='0'; --计数小于等于 2500000,输出 0 ELSIF cout1<m1*2 THEN tmp1<='1'; --计数小于 5000000,输出 1 ELSE cout1:=0; --计数器清零END IF;END IF;END PROCESS;clk_out1<=tmp1; --5M分频器输出END fwm;五:拓展内容首先需要一个分频器分频得到10Hz的时钟信号LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tuozhan ISPORT(clk:IN STD_LOGIC;clk_out1:OUT STD_LOGIC);END tuozhan;ARCHITECTURE fwm OF tuozhan IS--CONSTANT m : INTEGER:= 25000000; --50M 分频到 1Hz 时=25000000。

CONSTANT m1 : INTEGER:= 2500000; --5M 分频到 10Hz 时=2500000。

SIGNAL tmp :STD_LOGIC;SIGNAL tmp1 :STD_LOGIC;BEGINPROCESS(clk, tmp1)VARIABLE cout1 : INTEGER:=0;BEGINIF clk'EVENT AND clk='1' THENcout1:=cout1+1; --计数器+1IF cout1<=m1 THEN tmp1<='0'; --计数小于等于 2500000,输出 0 ELSIF cout1<m1*2 THEN tmp1<='1'; --计数小于 5000000,输出 1ELSE cout1:=0; --计数器清零END IF;END IF;END PROCESS;clk_out1<=tmp1; --5M分频器输出END fwm;然后需要一个计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder ISPORT (clk:IN STD_LOGIC;--接收10HZ的时钟信号dis_out:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END decoder;ARCHITECTURE fwm OF decoder ISBEGINPROCESS(clk)VARIABLE count : INTEGER:=0;BEGINCASE count ISWHEN 0 =>dis_out<="0000";WHEN 1 =>dis_out<="0001";WHEN 2 =>dis_out<="0010";WHEN 3 =>dis_out<="0011";WHEN 4 =>dis_out<="0100";WHEN 5 =>dis_out<="0101";WHEN 6 =>dis_out<="0110";WHEN 7 =>dis_out<="0111";WHEN 8 =>dis_out<="1000";WHEN 9 =>dis_out<="1001";WHEN 10 =>dis_out<="1010";WHEN 11 =>dis_out<="1011";WHEN 12 =>dis_out<="1100";WHEN 13 =>dis_out<="1101";WHEN 14 =>dis_out<="1110";WHEN 15 =>dis_out<="1111";WHEN OTHERS=>count:=0;END CASE;IF clk'EVENT AND clk='1' THENcount:=count+1;END IF;END PROCESS;END fwm;最后使用七段译码器译码为七段码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevendecoder ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0); dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END sevendecoder;ARCHITECTURE fwm OF sevendecoder ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示 0 WHEN"0001"=>dis_out<="1111001";--显示 1 WHEN"0010"=>dis_out<="0100100";--显示 2 WHEN"0011"=>dis_out<="0110000";--显示 3 WHEN"0100"=>dis_out<="0011001";--显示 4 WHEN"0101"=>dis_out<="0010010";--显示 5 WHEN"0110"=>dis_out<="0000010";--显示 6 WHEN"0111"=>dis_out<="1111000";--显示 7 WHEN"1000"=>dis_out<="0000000";--显示 8 WHEN"1001"=>dis_out<="0010000";--显示 9 WHEN"1010"=>dis_out<="0001000";--显示 A WHEN"1011"=>dis_out<="0000011";--显示 b WHEN"1100"=>dis_out<="1000110";--显示 C WHEN"1101"=>dis_out<="0100001";--显示 d WHEN"1110"=>dis_out<="0000110";--显示 E WHEN"1111"=>dis_out<="0001110";--显示 FWHEN OTHERS=> dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;五.实验结果实验1:VHDL源代码输入波形仿真配置针脚在计算机上完成模拟实验之后,重新进行编译,然后将程序下载到DE0开发板上并对异或门逻辑电路进行验证。