西北工业大学数电实验报告一Quartus和 Multisim

北理工数电仿真实验 (2)

本科实验报告实验名称: 一、QuartusII9、1 软件的使用二、模十状态机与 7 段译码器显示三、数字钟的设计与仿真课程名称:数电仿真实验实验时间:任课教师:实验地点:实验教师:√原理验证实验类型:□ 综合设计学生姓名:□ 自主创新学号/班级:组号:学院:同组搭档:专业:成绩:实验一 QuartusII9、1软件的使用一、实验目的:一、通过实现书上的例子,掌握QUARTUSII9、1软件的使用;二、编程实现3-8译码电路以掌握VerilogHDL语言组合逻辑的设计以及QUARTUSII9、1软件的使用。

二、实验步骤:1、程序;module ex4(input clk, load, en,input [3:0] qin,output reg [7:0] seg);reg [3:0] qout;always @ (posedge clk or posedge load) beginif (load)qout <= qin;elseif ( en )if (qout == 4'b1001)qout <= 4'b0000;elseqout <= qout +1 ;elseqout <= qout ;endalways @ (qout) begincase (qout)0:seg <= 7'b1000000;1:seg <= 7'b1111001;2:seg <= 7'b0100100;3:seg <= 7'b0110000;4:seg <= 7'b0011001;5:seg <= 7'b0010010;6:seg <= 7'b0000010;7:seg <= 7'b1111000;8:seg <= 7'b0000000;9:seg <= 7'b0010000;default:seg <= 7'b0001000;endcaseendendmodule2、功能图3、操作步骤(1)、建立 Verilog HDL 文件先建立一个工作目录文件,创建一个新项目并对项目命名:对参数设置点击Finish完成创建:(2)、新建文件:点击 File—>New,弹出对话框后选择 Verilog HDL File,然后进行编写代码。

西北工业大学模拟电子技术基础实验报告材料

模拟电子技术基础实验实验报告一、共射放大电路1.实验目的(1)掌握用Multisim 13仿真软件分析单极放大电路主要性能指标的方法。

(2)熟悉常用电子仪器的使用方法,熟悉基本电子元器件的作用。

(3)学会并熟悉“先静态后动态”的电子线路的基本调试方法。

(4)分析静态工作点对放大器性能的影响,学会调试放大器的静态工作点。

(5)掌握放大器电压放大倍数、输入电阻、输出电阻及最大不失真输出电压的测试方法。

(6)测量放大电路的频率特性。

2.实验内容(1)电路仿真1.1 静态工作点选择根据XSC1的显示,按如下方法进行操作:当滑动变阻器R7设置为11%时,有最大不失真电压。

1.2 静态工作点测量将交流电源置零,用万用表测量静态工作点。

1.3 电压放大倍数测量加入1kHz,100mV正弦波信号。

测量R L= ∞时输入输出电压有效值大小。

测量L R= 2kΩ时输入输出电压有效值大小。

1.4输入输出电阻测量输入电阻测量。

根据可计算得到输入电阻。

输出电阻测量。

根据可得到输出电阻。

1.5动态参数结果汇总(2)实验室实测2.1 静态工作点实测2.2 动态参数实测3.总结与讨论(1)共射组态放大器会使输入输出电压反相。

(2)L R会影响输出电阻、放大倍数。

二、集成运算放大器1.实验目的(1)加深对集成运算放大器的基本应用电路和性能参数的理解。

(2)了解集成运算放大器的特点,掌握集成运算放大器的正确使用方法和基本应用电路。

(3) 掌握由运算放大器组成的比例、加法、减法、积分和微分等基本运算电路的功能。

(4)进一步熟悉仿真软件的使用。

2.实验内容 (1)电路仿真集成运放是一种具有高电压放大倍数的直接耦合器件。

当外部接入有不同的线性或非线性元器件组成的输入负反馈电路时,可以灵活的实现各种函数关系 ,在线性应用方面,可组成加法、减法、比例。

积分、微分、对数等模拟运算电路。

在大多数情况下,将运放视为理想的,即在一般讨论中,以下三条基本结论是普遍使用的:开环电压增益∞=u A运放的两个输入端电压近似相等,即-V V =+,称为“虚短”。

西工大数电实验报告

计数器及其应用班级:10031101班 学号:2011302645 姓名: 王康同组成员:肖辉(2011302647)一、 实验目的1. 熟悉常用中规模计数器的逻辑功能。

2. 掌握二进制计数器和十进制计数器的工作原理和使用方法。

3. 运用集成计数器构成1/N 分频器。

二、 实验设备数字电路试验箱、函数信号发生器、数字双踪示波器、74LS90三、 实验原理计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。

计数器按计数进制有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。

目前,TTL 和CMOS 电路中计数器的种类很多,大多数都具有清零和预置功能,使用者根据器件手册就能正确地运用这些器件。

实验中用到异步清零二-五-十进制异步计数器74LS90。

74LS90是一块二-五-十进制异步计数器,外形为双列直插,引脚排列如图(1)所示,逻辑符号如图(2)所示,图中的NC 表示此脚为空脚,不接线,它由四个主从JK 触发器和一些附加门电路组成,其中一个触发器构成一位二进制计数器;另三个触发器构成异步五进制计数器。

在74LS90计数器电路中,设有专用置“0”端)1(0R 、)2(0R 和置“9”端)1(9S 、)2(9S 。

其中)1(0R 、)2(0R 为两个异步清零端,)1(9S 、)2(9S 为两个异步置9端,CP1、CP2为两个时钟输入端,Q0~Q3为计数输出端,74LS90的功能表见表(1),由此可知:当R1=R2=S1=S2=0时,时钟从CP1引入,Q0输出为二进制;时钟从CP2引入,Q3输出为五进制;时钟从CP1引入,而Q0接CP2 ,即二进制的输出与五进制的输入相连,则Q3Q2Q1Q0输出为十进制(8421BCD码);时钟从CP2引入,而Q3接CP1 ,即五进制的输出与二进制的输入相连,则Q0Q1Q2Q3输出为十进制(5421BCD码)。

西北工业大学数电实验报告1

实验1 TTL集成逻辑门参数测试学号:姓名:日期:组号:一、实验目的:(1)加深了解TTL逻辑门的参数意义。

(2)掌握TTL逻辑门电路的主要参数及测量方法。

(3)认识各种电路及掌握空闲端处理方法。

二、实验设备:数字电路实验箱,数字双踪示波器,函数信号发生器,数字万用表,74LS00,电位器,电阻。

三、实验原理:门电路是数字逻辑电路的基本组成单元,目前使用最普遍的双极型数字集成电路是TTL 逻辑门电路。

TTL集成电路的使用规则:(1)插集成块时,要认清定位标记,不得插反。

(2)使用电源电压范围为+4.5V~+5.5V。

实验中要求使用Vcc=+5V。

电源极性不允许接错。

(3)空闲输入端处理方法。

悬空,相当于正逻辑“1”,一般小规模集成电路的数据输入端允许悬空处理。

但易受外界干扰,导致电路逻辑功能不正常。

因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

(4)输入端通过电阻接地,电阻值的大小将直接影响电路所处状态。

(5)输出端不允许并联使用(三态门和OC门除外),否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

(6)输出端不允许直接接电源Vcc,不允许直接接地,否则会损坏器件。

四、实验内容:1、TTL信号的产生2、与非门的测试3、用74LS00实现逻辑函数:F=ABF=A+BF=A○+B五、实验结果:F=AB=AB∙1A∙∙B∙1F=A+B=1∙∙B∙ABF=A○+B=A AB。

数电quartus实验报告

可编程逻辑器件FPGA实验一组合逻辑电路设计1、掌握中规模数字集成器件的逻辑功能及使用方法2、熟悉组合逻辑电路的设计方法3、了解数字可编程器件的应用设计4、学会QUARTUS软件的基本使用方法二.实验器材1、软件:QUARTUSII2、硬件:DE-2实验板,PC机三.实验原理利用74283芯片进行加减法运算,(M控制加减法,结果为负数时CO和M的异或输出为1,接二极管亮)并再利用另外一个74283芯片将运算得到的补码输出转换为原码。

接着利用7485数据比较器进行数据比较(与9比较),当输出小于9时,利用7485 的AGBO的输出为低电平控制十位输出为0,并控制个位输出为原码输出减0的结果;当输出大于9时AGBO输出为高电平,其可控制十位输出为1,个位输出为原码输出减10的结果。

最后十位输出和个位均接7447进行显示。

四.实验内容1、设计一个两组四位二进制数的加减运算显示电路。

要求:一个控制加减运算的功能按键;两数相加的绝对值不大于15;用两个七段数码管显示算术运算结果(0~15);当运算结果为负数时,红色发光二极管亮。

在QUARTUSII中进行:(1)电路设计(2)功能仿真(3)时序仿真2、下载DE-2板验证设计结果。

五.实验总结1、实验故障及解决方法①电脑无法连接DE-2板可能是数据线的问题。

②DE-2板无法使用更换DE-2板。

③输出结果不对仔细检查并修改电路设计,必要时寻求同学或老师的帮助。

2、实验体会完成实验的重点是理解实验内容要求,并通过对quartus ii 的学习,根据自己思路自行设计或者和同学共同设计电路原理图。

六.思考题1、当运算结果大于15时,显示译码电路如何设计?可以将运算结果输出用7485与15比较,把AGBO输出加非门后再与VCC与门输入两个数码管的BIN端。

当结果大于15时,两个数码管全灭,结果小于等于15时,不受影响。

2、如何实现两个一位十进制数的加减运算电路?讲十进制转化为四位二进制就可以用上述电路原理图进行加减法运算。

数电第一次实验报告_西工大

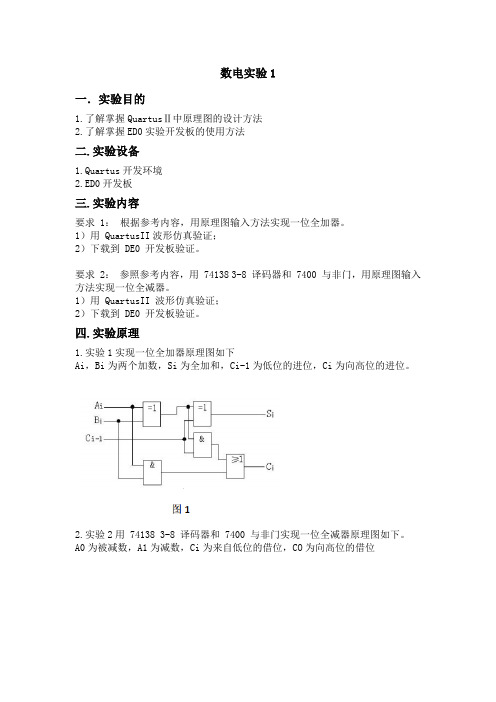

数电实验1一.实验目的1.了解掌握QuartusⅡ中原理图的设计方法2.了解掌握ED0实验开发板的使用方法二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求 1:根据参考内容,用原理图输入方法实现一位全加器。

1)用 QuartusII波形仿真验证;2)下载到 DE0 开发板验证。

要求 2:参照参考内容,用 74138 3-8 译码器和 7400 与非门,用原理图输入方法实现一位全减器。

1)用 QuartusII 波形仿真验证;2)下载到 DE0 开发板验证。

四.实验原理1.实验1实现一位全加器原理图如下Ai,Bi为两个加数,Si为全加和,Ci-1为低位的进位,Ci为向高位的进位。

2.实验2用 74138 3-8 译码器和 7400 与非门实现一位全减器原理图如下。

A0为被减数,A1为减数,Ci为来自低位的借位,CO为向高位的借位五.实验结果实验1:原理图输入波形仿真配置针脚在计算机上完成模拟实验之后,重新进行编译,然后将程序下载到DE0开发板上并对全加器进行验证。

验证结果无误。

实验2:原理图输入波形仿真六.故障排除&实验心得实验中,我们最大的问题就在于如何构建整个系统。

整个实验都是比较基本的一些语句和一些简单门电路的综合使用。

我们进一步的了解了整个系统的构建和编译过程,使我们对VHDL语句和Quartus的使用有了进一步的认识。

个人认为,VHDL语言不够简洁,有些表示比较麻烦。

这次实验首次让我们将数电理论运用到实践,增强了我们对于全加器和全减器的理解和运用,为我们将来的学习和工作提供了良好的基础。

北邮数电实验报告

北京邮电大学实验报告实验名称: 数电电路与逻辑设计实验学院:信息与通信工程学院班 级: 姓 名: 学 号: 班内序号:日期:一. 实验一:QuartusII 原理图输入法设计1. 实验名称和实验任务要求(1)用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块 元。

(2)用(1)中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号入信号。

(3)用3线-8线译码器(74LS138)和逻辑门设计实现函数F=A B C +A B C +AB C +A B C 。

2.实验原理图及波形图(1)半加器(2)全加器(3)74LS383.仿真波形图分析(1)半加器:输入为a,b,输出S,CO(进位)。

当ab都为0时,半加和s=0,进位端co=0。

当ab都为1时,半加和s=0,进位端co=1。

当a=1,b=0或a=0,b=1时,半加和s=1,进位端co=0。

(2)全加器:输入a,b,输出S,CO(进位),ci(低进位)。

当a=0,b=0,ci=0,输出s=0,co=0。

当a=0,b=1或a=1,b=0又ci=0,输出s=1,co=0。

当a=0,b=0,ci=1,输出s=1,co=0。

(3)74LS138输入A,B,C,输出为3。

四个输出对应F中的四个最小项,Y0、Y2、Y4、Y7,以实现函数功能。

二.实验二:用VHDL设计与实现组合逻辑电路1.实验名称和实验任务要求(1)用VHDL语言设计实现一个共阴极7段数码管译码器,仿真验证其功能。

要求用拨码开关设定输入信号,7段数码管显示输出信号。

(2)用VHDL语言设计实现一个8421码转换为余3码的代码转换器,仿真验证其功能。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

(3)用VHDL语言设计实现一个4位二进制奇校验器,输入奇数个’1’时,输出为’1’,否则输出’0’,仿真验证其功能。

西北工业大学_数字电子技术基础_实验报告_实验3

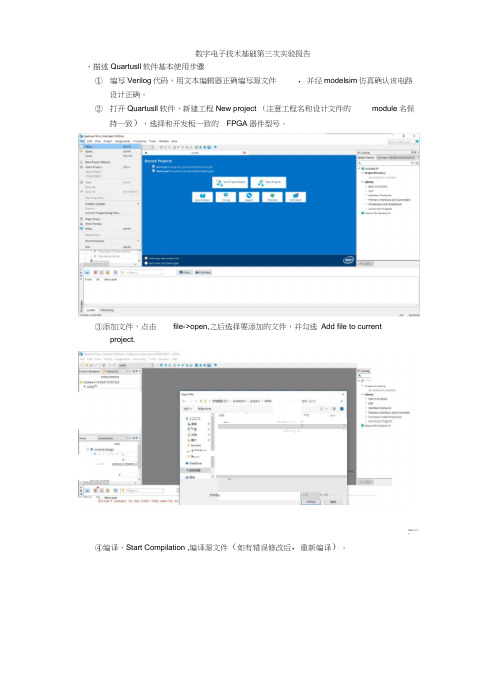

数字电子技术基础第三次实验报告、描述Quartusll 软件基本使用步骤① 编写Verilog 代码,用文本编辑器正确编写源文件,并经modelsim 仿真确认该电路设计正确。

② 打开Quartusll 软件,新建工程New project (注意工程名和设计文件的module 名保持一致),选择和开发板一致的 FPGA 器件型号。

■■pww n④编译,Start Compilation ,编译源文件(如有错误修改后,重新编译)。

I —f 1 UuM-JI 工 HfiaMi■sm •MITmHL 1 】it A**5KiiatiT^u^ri :i&1 u■审3T1H・”峠if-Ik r irM "小"=③添加文件,点击file->open,之后选择要添加的文件,并勾选 Add file to currentproject.■ 5r-w in¥ 口X.I M■tWIR fetawej. MtamM* E«Maa4inrv*nn♦ 1 Tl n .■EGvi I IPHIWIVE RHF 4- xsfflECA-ihaW MniWmUAf⑤查看电路结构,使用 Tool->RTL viewer 工具查看电路图结构,是否和预期设计一致。

rp M. Oi* >1 JiMiMdaOML <j| Al-O*ih| La ■D/»i -ii !Hbi.urmpM-羽r 嘴U 电Of■ >lir¥i-*U ■屮剑 f*lM W"M*h 1 $TW<tEQuartus Primer*rfw 杠 w* ■ « ■■! I Q » i 恆G|4OV :I4J ■忙ffl草* F■*■1.设计一款时钟上升沿触发的 D 寄存器TilbfilUL.X.■I:(■■i!|*ij JHft* I i ■i E. duqa.,卜r|il.A, -K^'M la^34r vf (r«i H >«ra w wl as-Kif i*d mich Wp CMIM* e faharwl HKhinu. 3.' thd d&a ip*H¥l: MW mRM_LEL HDCTE^DIS' *ih tnvr 05T tc- r vtw. llivl 4 nt* 111 Hi >4 -Mji lltf ¥111 4 igf IhB 4■Z.7UZ - unri J ■»I fi i■- w rnr I U I FIV J mtnt- , ■ w ^aanr* fi Ir ■KdP-ir'iiH/prnrlM*!1I, *.题目代码以及波形分析a)编写模块源码module flipflop(D,Clock,Q);in put D,Clock;output reg Q;always@(posedge Clock) Q=D;en dmoduleb) 测试模块'timescale 1n s/1psmodule tb_flipflop;reg Clock_test;reg D_test;wire Q_test; in itial Clock_test=0;always #20 Clock_test=~Clock_test; in itial D_test=0;always #77 D_test=~D_test;flipflop UUT_flipflop(.CIock(Clock_test),.D(D_test),.Q(Q_test)); en dmodulec) 仿真后的波形截图 input D0,D1,Sel,Clock;output reg Q;d) 综合后的RTL 图形2. 设计一款4bBit 具有并行加载功能的移位寄存器编写模块源码a) 编写模块源码module muxdff(D0,D1,Sel,Clock,Q);每当时钟上升沿到来时,触发器把 D 的信号传给Q1 -MlB ! L IVh :> 柏"甲^革曲神甲 翹甘I 『■申 £^4HtfTAiw i||jI ** E - - M ■ < J ■: < '«Ihl^fcp :- *□-refDwire D;assign D=Sel?D1:D0;always@(posedge Clock)Q<=D;endmodulemodule shift4(R,L,w,Clock,Q);input [3:0]R;input L,w,Clock;output wire [3:0]Q;muxdff Stage3(w,R[3],L,Clock,Q[3]);muxdff Stage2(Q[3],R[2],L,Clock,Q[2]);muxdff Stage1(Q[2],R[1],L,Clock,Q[1]);muxdff Stage0(Q[1],R[0],L,Clock,Q[0]); endmodule b) 测试模块'timescale 1n s/1psmodule tb_shift4;reg Clock_test;reg L_test;reg w_test;reg [3:0]R_test;wire [3:0]Q_test;initialClock_test=0;always #10 Clock_test=~Clock_test;initialbeginL_test=1;#14L_test=0;//always #14 L_test=~L_test; endinitialw_test=0;always #13 w_test=~w_test;initialR_test=4'b1010;shift4 UUT_shift4(.CIock(Clock_test),.L(L_test),.w(w_test),.R(R_test),.Q(Q_test)); en dmoduleL 为0时并行加载,数组 R 为加载时的输入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子技术基础

实验报告

题目:实验一 TTL集成门电路逻辑变换

小组成员:

小组成员:

实验一TTL集成门电路逻辑变换

一、实验目的

通过完成所要求的实验内容,来熟练掌握运用TTL集成门电路逻辑变换的基本原理,充分了解 Multisim 软件的仿真技术和QuartusII 软件的绘制原理图、编译程序、波形仿真等功能及将程序写入开发板的全体流程步骤,深入学习数字电路在实践运用中所面临的场景,进而为后续对数字电路更深层次的使用及实验打下良好铺垫。

二、实验要求

要求一:测试与非门逻辑功能。

用MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能

要求二:用与非门实现“与”逻辑。

用 MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能

要求三:用与非门实现“或”逻辑。

用 MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能

要求四:用与非门实现“异或”逻辑。

用 MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能

要求五:用门电路设计实现一位全加器。

用MULTISIM软件仿真后,再用 FPGA 实现电路测试逻辑功能

三、实验设备

(1)电脑一台;

(2)数字电路实验箱;

(3)数据线一根。

四、实验原理

Multisim 的模拟电路编程原理

Quartus II的模拟电路编译、波形仿真及目标器件写入的基本应用数字电路逻辑表达式转换的基本知识

五、实验内容

1、(要求一)

(1)逻辑表达式变换过程

(2)原理图(Multisim和QuartusII中绘制的原理图):

(3)波形仿真:

(4)记录电路输出结果

A B Y

0 0 1

0 1 1

1 0 1

1 1 0

2、(要求二)

(1)逻辑表达式变换过程

(2)原理图(Multisim和QuartusII中绘制的原理图):

(3)波形仿真:

(4)记录电路输出结果

A B Y

0 0 0

0 1 0

1 0 0

1 1 1

3、(要求三)

(1)逻辑表达式变换过程

(2)原理图(Multisim和QuartusII中绘制的原理图):(3)波形仿真:

(4)记录电路输出结果

A B Y

0 0 0

0 1 1

1 0 1

1 1 1

4、(要求四)

(1)逻辑表达式变换过程

(2)原理图(Multisim和QuartusII中绘制的原理图):(3)波形仿真:

(4)记录电路输出结果

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

5、(要求五)

(1)全加器的真值表

(2)最简逻辑表达式推导

(3)原理图(Multisim和QuartusII中绘制的原理图):(4)波形仿真:

(5)记录电路输出结果

A B C S C0

0 0 0 0 0

0 0 1 0 1

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 0 0

六、实验过程中的问题

1.软件使用过程中一直有着繁琐的不规范的使用步骤和流程

2.写入目标器件时步骤不当,严重拖累实验过程

七、心得体会

1.模拟过程中学会了Multisim 和 Quartus 的基本用法,能够自主学习和运用课程中的知识去解决现实问题

2.在解决问题的过程中虽然遇到了障碍以及问题,但是在我和我队友的一起努力下,最终终于解决了问题,体现了团队合作的重要性。