集成电路测试3

PD666–3S3说明书

PD666–3S3说明书

直接式接法:1、2内部短接为火线的进线,3为火线的出线,4为零线进,5为零线出;互感式接法:1为电流进线,3为电流出线,2为空,4为火线进,5为零线出。

具体要看表计接线盒背面的接线图。

电感、电容、电阻参数测量仪,不仅能自动判断元件性质,而且能将符号图形显示出来,并显示出其值。

还能测量Q、D、Z、Lp、Ls、Cp、Cs、Kp、Ks等参数,且显示出等效电路图形。

集成电路测试仪可对TI1、PM0S、CM0S数字集成电路功能和参数进行测试,还可判断抹去字的芯片型号及对集成电路在线功能测试、在线状态测试。

扩展资料

万用表由表头、测量电路及转换开关等三个主要部分组成。

万用表是电子测试领域最基本的工具,也是一种使用广泛的测试仪器。

万用表又叫多用表、三用表(A,V,Ω也即电流,电压,电阻三用)、复用表、万能表,万用表分为指针式万用表和数字万用表,还有一种带示波器功能的示波万用表,是一种多功能、多量程的测量仪表。

一般万用表可测量直流电流、直流电压、交流电压、电阻和音频电平等。

数字集成电路习题(第三章)

0. Explain qualitatively

4

Chapter 3 Problem Set a. Write down the equations (and only those) which are needed to determine the voltage at node X. Do NOT plug in any values yet. Neglect short channel effects and assume that λp = 0. b. Draw the (approximative) load lines for both MOS transistor and resistor. Mark some of the significant points. c. Determine the required width of the transistor (for L = 0.25µm) such that X equals 1.5 V. d. We have, so far, assumed that M1 is a long-channel device. Redraw the load lines assuming that M1 is velocity-saturated. Will the voltage at X rise or fall?

Table 0.2 Measurements taken from the MOS device, at different terminal voltages.

Measurement number 1 2 3 4 5 6 7 8.

VGS (V) -2.5 1 -0.7 -2.0 -2.5 -2.5 -2.5

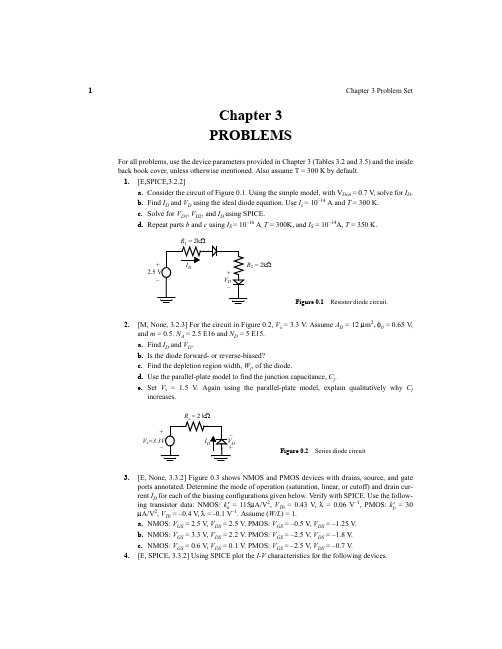

R1 = 2kΩ + 2.5 V – ID R2 = 2kΩ

集成电路测试课程

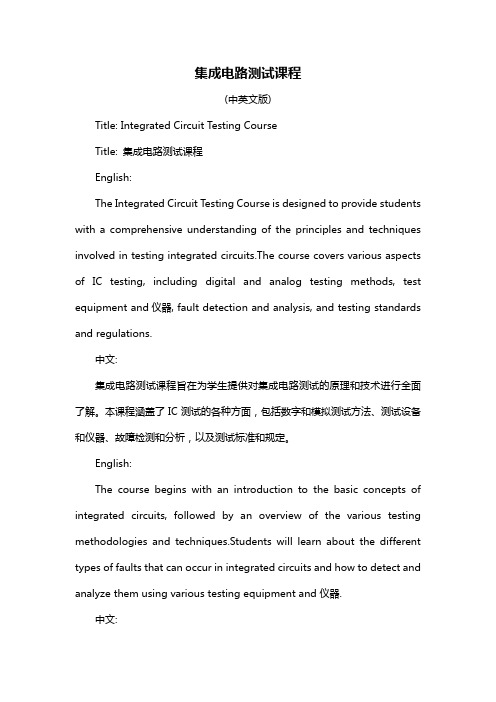

集成电路测试课程(中英文版)Title: Integrated Circuit Testing CourseTitle: 集成电路测试课程English:The Integrated Circuit Testing Course is designed to provide students with a comprehensive understanding of the principles and techniques involved in testing integrated circuits.The course covers various aspects of IC testing, including digital and analog testing methods, test equipment and仪器, fault detection and analysis, and testing standards and regulations.中文:集成电路测试课程旨在为学生提供对集成电路测试的原理和技术进行全面了解。

本课程涵盖了IC测试的各种方面,包括数字和模拟测试方法、测试设备和仪器、故障检测和分析,以及测试标准和规定。

English:The course begins with an introduction to the basic concepts of integrated circuits, followed by an overview of the various testing methodologies and techniques.Students will learn about the different types of faults that can occur in integrated circuits and how to detect and analyze them using various testing equipment and仪器.中文:课程从对集成电路基本概念的介绍开始,然后概述了各种测试方法和技巧。

(完整word版)《半导体集成电路》考试题目及参考答案

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性 开门/关门电平 逻辑摆幅 过渡区宽度 输入短路电流 输入漏电流静态功耗 瞬态延迟时间 瞬态存储时间 瞬态上升时间 瞬态下降时间瞬时导通时间2. 分析四管标准TTL 与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

集成电路测试基本原理

集成电路测试基本原理

集成电路测试的基本原理是:被测电路DUT(Device Under Test)可作为一个已知功能的实体,测试依据原始输入X和网络功能集F(X),确定原始输出回应Y,并分析Y是否表达了电路网络的实际输出。

因此,测试的基本任务是生成测试输入,而测试系统的基本任务则是将测试输人应用于被测器件,并分析其输出的正确性。

测试过程中,测试系统首先生成输入定时波形信号施加到被测器件的原始输入管脚,第二步是从被测器件的原始输出管脚采样输出回应,最后经过分析处理得到测试结果。

集成电路测试的作用包括:

1. 检测:确定被测器件DUT是否具有或者不具有某些故障。

2. 诊断:识别表现于DUT的特性故障。

3. 器件特性的描述:确定和校正设计和/或者测试中的错误。

4. 失效模式分析(FMA):确定引起DUT缺陷制造中的错误。

以上信息仅供参考,如有需要,建议咨询专业技术人员。

集成电路储存温度测试标准

集成电路储存温度测试标准

集成电路储存温度测试标准通常包括高温测试、低温测试和温度循环测试。

1. 高温测试:高温测试的目的是模拟集成电路在高温环境下的性能表现。

通常,高温测试的温度设定在85℃或125℃以上,具体温度根据不同的产品和应用需求而定。

在高温测试中,集成电路需要在设定的温度下保持稳定,以确保在正常工作条件下不会出现性能下降或故障。

2. 低温测试:低温测试的目的是模拟集成电路在低温环境下的性能表现。

通常,低温测试的温度设定在-55℃或更低,具体温度根据不同的产品和应用需求而定。

在低温测试中,集成电路需要在设定的温度下保持稳定,以确保在正常工作条件下不会出现性能下降或故障。

3. 温度循环测试:温度循环测试的目的是模拟集成电路在不同温度环境下的性能表现。

在温度循环测试中,集成电路需要在高低温之间循环,以检验其性能的稳定性和可靠性。

通常,温度循环测试的次数根据不同的产品和应用需求而定,但通常不少于50次。

总的来说,集成电路储存温度测试标准是为了确保集成电路在各种温度条件下都能保持稳定的性能表现,以确保产品的可靠性和稳定性。

mos数字集成电路的测试方法 标准

mos数字集成电路的测试方法标准

MOS数字集成电路的测试方法主要包括以下几种:

直流测试:通过在MOS管的栅极施加一个直流电源,观察漏极电流的变化来判断MOS管的工作状态。

这种方法主要用于测试MOS管的静态工作性能,如漏源电压、泄漏电流等。

交流测试:通过在MOS管的栅极施加一个交流信号,观察漏极电压的变化来判断MOS管的工作状态。

这种方法主要用于测试MOS管的动态工作性能,如开关速度、功耗等。

在MOS数字集成电路的测试中,还需要遵循一些标准,以确保测试结果的准确性和可靠性。

这些标准包括:

测试条件的一致性:在进行测试时,需要保证测试条件的一致性,包括测试温度、测试电压、测试频率等。

这样才能保证不同批次的产品之间的可比性。

测试设备的精度和稳定性:测试设备需要具有高精度和稳定性,以确保测试结果的准确性和可靠性。

测试程序的一致性:在进行测试时,需要按照规定的测试程序进行操作,避免因操作不当导致测试结果的偏差。

测试数据的记录和分析:在进行测试时,需要对测试数据进行记录和分析,以便及时发现产品存在的问题并进行改进。

总之,MOS数字集成电路的测试方法需要遵循一定的标准,以确保测试结果的准确性和可靠性。

同时,还需要注意测试条件的一致性、测试设备的精度和稳定性、测试程序的一致性以及测试数据的记录和

分析等方面的问题。

数电实验实验三、四

12.3 数据选择器 2.3.1 实验目的1.测试集成数据选择器74151的逻辑功能。

2.用74151构成大、小月份检查电路。

3.用74151构成比较2个4位二进制数是否相等的电路。

2.3.2 实验设备与器件1.74151型8选1数据选择器1块 2.7404型六反相器1块 2.3.3 实验原理数据选择器从多路输入数据中选择其中的一路数据送到电路的输出端。

数据选择器分为4选1数据选择器和8选1数据选择器。

74151是8选1数据选择器,数据输入端0D ~7D 是8位二进制数,2A 1A 0A 是地址输入端,Y 和Y 是一位互补的数据输出端,S 是控制端。

其管脚如图2-3-1所示,逻辑功能如表2-3-1所示。

74151的逻辑表达式是:)A A A (D )A A A (D )A A A (D )A A A (D Y 0123012201210120+++=)A A A (D )A A A (D )A A A (D )A A A (D 0127012601250124++++图2-3-1 74151管脚图逻辑开关LED图2-3-2 74151逻辑功能测试图D0D1D2D3D4D5D6D7A2A1A0YVCC GNDYS74151432115141312161011798562表2-3-1 74151功能表2.3.4预习要求1. 理解数据选择器的工作原理,掌握四选一数据选择器和八选一数据选择器的逻辑表达式。

2. 查找八选一数据选择器74151的管脚图。

3. 写出大、小月检查电路的设计方法,要求是:用4位二进制数0123A A A A 表示一年中的十二个月,从0000~1100为1月到12月,其余为无关状态;用Y 表示大小月份,Y=0为月小(二月也是小),Y=1为月大(7月和8月都是月大)。

4.用两片74151设计一个判断两个2位二进制数是否相等的电路。

5.根据实验内容的要求,完成有关实验电路的设计,拟好实验步骤。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.2 良率

3.3 测量品质的缺陷等级

缺陷级别:在通过测数来表 示(ppm)。

EX3.1

There are some parameters of two different process of a chip. The expected sale of this chip between 100,000 and 500,000. can you figure out the cost of per chip with 65nm and 90nm process. Everyone can choose a different production between 100,000 and 500,000.

Yield

3.1 测试经济学

十倍法则: 如果一个芯片故障没有在芯片测试时发 现,那么在PCB级别发现故障的成本就是 芯片级别的10倍。 如果一个PCB故障没有在电路板测试时 被发现,那么在系统级别发现错误的成本 将是PCB级别的10倍。

3.2 良率

良率(yield) = 好的芯片数目/生产出来的总的芯片数 圆片良率:一个圆片上的好芯片的平均数

第三章 测试经济学和产品质量

3.1 测试经济学 3.2 良率 3.3 测量品质的缺陷等级

3.1 测试经济学

总成本(TC) = 固定成本(FC) +可变成本(VC)

平均成本(AC) = 总成本/产量

Total Cost

Cost per IC

Variable cost

Die Cost

Wafer Size