UHF RFID芯片 AS3990-AS3991芯片资料

UHF常用芯片汇总

UHF常用芯片汇总以下是一些常用的UHF(Ultra High Frequency)芯片的汇总,这些芯片主要用于无线通信和RFID(Radio Frequency Identification)应用。

1. Impinj Monza系列Impinj Monza系列芯片是全球最著名的UHF RFID芯片之一、这个系列提供了高性能、高度集成、低功耗的解决方案。

Monza系列的芯片通常用于物联网、零售、物流和库存管理等领域。

2.NXPUCODE系列NXPUCODE系列芯片是业界最常见的UHFRFID芯片之一、这个系列的芯片具有卓越的性能和可靠性,支持多协议,能够满足不同应用的需求。

UCODE芯片广泛应用于零售、物流、运输和电子票务等领域。

3. Alien Higgs系列Alien Higgs系列芯片是另一个广受欢迎的UHF RFID芯片。

这个系列的芯片采用先进的射频和数字电路技术,具有高度集成、低功耗和高性能的特点。

Higgs芯片常用于零售、制造业、医疗和物流等领域。

4. STMicroelectronics ST25系列ST25系列芯片由STMicroelectronics推出,是一款多功能的UHF RFID芯片。

该系列的芯片具有高度集成、低功耗和优秀性能等特点。

ST25系列芯片广泛应用于物联网、安全识别、物流和库存管理等领域。

5. TI Tag-it系列TI Tag-it系列芯片是德州仪器(Texas Instruments)推出的UHF RFID芯片。

这个系列的芯片具有高度集成、低功耗和高性能的特点,能够满足不同应用领域的需求。

Tag-it芯片常用于物流、库存管理和电子车牌等领域。

6. Smartrac Frog系列7. SensThys SensArray系列SensThys SensArray系列芯片是一种集成射频前端和数字电路的UHF RFID芯片。

这个系列的芯片具有高度灵活性和可扩展性,适用于不同射频环境下的部署和应用。

UHF频段的RFID应用介绍

UHF频段的RFID应用介绍从全国第二代身份证、上海特奥会RFID应用、北京机场RFID行李传递系统、广深铁路RFID车票应用到深圳图书馆RFID应用等,RFID开始变得无处不在。

但在应用过程中,RFID却遭遇过不同程度的挫折。

12月7日,记者就此问题采访了RFID网络化应用解决方案提供商REV A公司亚太区总经理司马聪博士。

RFID就是用无线方法做身份识别的技术,其遭受的挫折来自于它的特殊性。

很多频段都可以使用RFID,但真正在工业化上实现了标准化的RFID使用的一些主要频段有几种:低频段的有125千赫兹,高一些的有13.56兆赫兹、433兆赫兹频段,UHF是800兆赫到900兆赫的频段,往上还有2.4G和5.8G的频段,而在RFID应用中,13.56兆赫兹频段的应用占据了每年业务总量一半以上。

这是在我们身边应用最普遍的一个频段,一卡通和二代身份证就是在这个频段。

司马聪说。

因为需要接触距离比较短,所以上下公交车时,人们需要把卡贴在读写器上,去机场自助办理登机牌,也需要把身份证贴在机器的自动读取区。

13.56兆赫的应用已经非常成熟,而UHF频段则成为一个新的挑战市场。

虽然业内普遍乐观,认为UHF频段的RFID应用会增到相当大的份额,但在推广中遇到不少挫折和挑战,主要反映在几大方面:第一方面,RFID系统根据不同的需求,需要不同的标签、不同的读写器,不仅产品的型号不同,生产厂商也可能不一样,这需要应用系统必须是异构平台,异构平台一定要有系统集成商通过一个整体的解决方案把不同厂商的产品集成在一起,这就是一个很大的挑战。

第二方面,在UHF频段应用中,标签被读写的距离比较远,大约从几米到几十米不等,在超市、库房等比较复杂的生产环境里面,一般会有多个天线放在场地里面,哪个天线用什么样的频段?标签接收哪个天线的信号?怎么控制它?天线之间还可能产生干扰,这都存在问题,这些问题不解决,就不可能准确的读出RFID 的数据。

uhf芯片

uhf芯片UHF芯片(Ultra High Frequency chip)是一种高频电子标签芯片,广泛应用于无线射频识别(RFID)技术中。

它具有高频率、长距离传输和多标签同时识别等特点,因此被广泛用于物流管理、库存控制、门禁系统、支付系统等各个领域。

UHF芯片由于其高频率的特点,能够实现长距离的读写操作。

通常使用860-960MHz的频段,这种频率能够穿透物体并实现长距离的数据传输。

相比之下,低频和高频RFID芯片的识别距离较短,因此UHF芯片在大型仓库和物流等需要远距离识别的场景中表现出色。

此外,UHF芯片还具有多标签同时识别的能力,这是由于其高频率的特性造成的。

在一定范围内,UHF读写器能够同时读取和识别多个UHF芯片,大大提高了读取效率和系统的可扩展性。

这种特性使得UHF芯片在高密度场景,如人群管理、车辆进出等应用中表现出色。

UHF芯片还具有数据存储和传输的功能。

每个UHF芯片中都有一块存储器,可以存储一定量的信息,如产品名称、批次号、生产日期等。

通过UHF读写器,可以实现对芯片中存储的数据的读取和写入操作。

这种功能使得UHF芯片在物流管理和库存控制等领域中非常实用,能够追踪产品的信息和状态,并实现自动化管理。

UHF芯片的应用领域非常广泛。

在物流管理方面,UHF芯片能够实现物品的追踪和定位,大大提高了物流效率和准确性。

在库存控制方面,UHF芯片能够实时记录产品的进出库情况,方便库存管理和货物跟踪。

在门禁系统中,UHF芯片可以用于人员身份认证和进出门禁区域的控制。

在支付系统中,UHF芯片可以用于无接触支付,提供更便捷的支付方式。

总的来说,UHF芯片作为一种高频电子标签芯片,在物流管理、库存控制、门禁系统、支付系统等领域发挥了重要作用。

其高频率、长距离传输和多标签同时识别等特点使得UHF芯片成为了无线射频识别技术中的重要组成部分,为我们的生活带来了诸多便利。

R1000,AS3990介绍

R1000进展(2008-08-05) - Administrator - 最近更新 (2008-09-07) Impinj Indy R1000芯片将改变UHF RFID应用现状近年来,由于采用了不同行业和应用的多项技术,超高频无源标签的性能和标准制定方面都有了很大的进步。

然而,标签读写器方面的改革却进展很缓慢。

但这种局面将很快被一项高科技技术所改变。

一、技术革新的意义目前UHF阅读器尺寸相对较大,大多相当于一台平板电脑的体积,并且成本高达2,000美元之多。

这部分是由于材料清单中有高达200美元的收发器模块所致,而这些模块由超过100个分立的元件设计而成。

采用新型Impinj Indy R1000芯片,阅读器可能会低至500美元,并且具有一个大的PCMCIA卡那样的接口。

该产品适用于UHF频段,集成有现有读写器中90%的离散元件。

并且,其体积仅为8x8mm,最大功耗仅为1.5W左右。

更低的功耗等级意味着R1000使手持外设能通过2.5W燯SB连接到笔记本电脑以获取电源。

这样RFID读写器和打印机制造商就可以缩小读写器的外型大小并改善他们产品的能源效率。

现有的UHF频段读写器产品普遍价格昂贵,结构复杂,产品研发工作的技术准入要求较高,在一定程度上抑制了UHF频段RFID产品整体市场的发展。

而Impinj Indy燫1000芯片产品的推出,将能够深刻改变UHF频段的RFID产品市场:牋 1.犛捎赗1000芯片的功能集成性特点,UHF频段读写器的技术门槛、产品换代周期以及传统厂商的先发优势都将被大幅降低。

国内众多的电子产品制造企业可以利用自身的成本优势与研发特定行业市场产品的经验,加入UHF频段读写器的厂商队列,并丰富UHF频段RFID产品应用领域。

牋 2.犛捎赗1000芯片体积小、功耗低的特点,UHF频段RFID读写功能可集成在PDA、电脑外设内,读写器设备将会向便携化、小型化的趋势发展。

牋 3.犛捎赗1000芯片成本较低的特点,用户引入RFID系统的投资金额均被降低,困扰UHF频段RFID应用发展的成本问题将在一定程度上得以缓解。

RIID硬件原理及其实现

组合模式

Registers 12, 14, 15, 16, and 17 are three bytes deep. They can be accessed by Continuous address mode only. The least significant byte is accessed first. It is possible to access only deep register in a single communication stream。

Continuous address mode

Cont mode=1, the first data that follows the address is written (or read) to (from) the given address. For each additional data, the address is incremented by one.

Start = start condition Adr = address with Cont bit low Adrc = address with the Cont bit high Cmd = command byte Data = data byte StopSgl = stop condition for termination of the command or non-continuous address mode StopCont = stop condition for termination of the continuous address mode

AS3992与R2000对比 详解AS3992与R2000性能差异

AS3992与R2000对比详解AS3992与R2000性能差异本文主要介绍的是关于AS3992与R2000的对比情况,并详细描述了AS3992与R2000之间性能及其特性的不同。

AS3992超高频的RFID读取芯片,接收灵敏度达到-86DB,同时支持IEC18000-6B通信协议。

采用64引脚QFN封装(9mm x9mm)。

芯片的集成度非常高,在发射端主要集成锁相环、压控振荡器、混频器、调制器以及功率放大电路,同时还支持协议处理的数字部分,为了满足不同需要,用户还可以通过编程选择外部放大电路;在接收端主要集成了低噪声放大器、混频器、中频放大器以及解调电路;另外,为降低功耗,芯片支持多种用电模式,同时还可以为外部控制器及其他部件提供1.5~3.3V的电压;可选的协议处理单元,等,这些都极大的简化了射频外围电路的设计,内部的协议处理也大大方便了应用开发。

如图所示,该芯片主要分为射频模块和MCU接口模块、射频芯片与单片机通过串口或并口通信,接受和执行单片机的指令。

传输数据时,数据或指令的书面24b fif0登记通过MCU接口模块。

芯片上的数据进行一系列处理,包括组装框架根据ISO / iec_18000-6c通信协议,加入帧头和CRC校验码、编码、调制和放大。

根据需要,还可以choose_external 功率放大。

最后,通过天线向外辐射射频模数转换处理,解码后的数据到单片机中进行处理,一些事宜和OSCO连接到20MHz的晶体振荡器。

R2000R2000芯片是一款高性能UHF频段的超高频读写器芯片,它集成了混频器、增益滤波器、压控振荡器、锁相环、模数/数模转换器等模拟前端,并且内置了ISO/IEC 18000 6C 的完整协议处理系统。

外部控制器仅需通过8位并口或者SPI口即可实现对R2000芯片的所有通信和控制。

超高频载波信号的通信频率为840 MHz~960 MHz,R2000芯片集成了VCO、预分频器、主除法器、参考除法器、鉴相器和电荷泵,外围电路只要提供一个环路滤波器即可组成一个完整的锁相环(PLL)电路。

射频识别技术UHF-RFID

EPC简介

• EPC的全称是Electronic Product Code, 中文 称为产品电子代码。EPC的载体是RFID电子 标签,并借助互联网来实现信息的传递。 EPC旨在为每一件单品建立全球的、开放的 标识标准,实现全球范围内对单件产品的 跟踪与追溯,从而有效提高供应链管理水 平、降低物流成本。EPC是一个完整的、复 杂的、综合的系统。

• UHF标签电路采用ASK和PSK的调制方式,将编码信息发送给阅读器,实现了 阅读器和标签之间的双向通讯。

1 0 0 1

s t

Ts

t

载波

t

2ASK

t

1 0 0பைடு நூலகம்1 1

PSK

Ts

t

6

UHF-RFID工作原理

• 相互认证通过之后,阅读器会向电子标签发出读、写、锁定、kill、盘存等 操作指令。

• 用户存储器

该存贮区用于存贮用户自定义的数据。用户可以对该存贮区进行该、写操 作。 该存贮器的长度由各个电子标签的生产厂商确定。每个生产厂商提供的电 子标签,其用户存贮区的长度会不同。存贮长度大的电子标签会贵一些。 用户应根据自身应用的需要,来选择相关长度的电子标签,以减低标签的 成本。

18

EPC标签

• EPC存储器

EPC存储器用于存贮电子标签的EPC号、PC(协议-控制字)以及这部份 的CRC-16校验码。 其中:CRC-16:存贮地址为00,共2个字节16位,CRC-16为本存贮体中存 贮内容的CRC校验码。 PC:电子标签的协议-控制字,存贮地址为10,共2个字节16位。 PC表明本电子标签的控制信息,包括如下内容: PC为2个字节,16位,其每位的定义为:

26

高频电路阻抗匹配

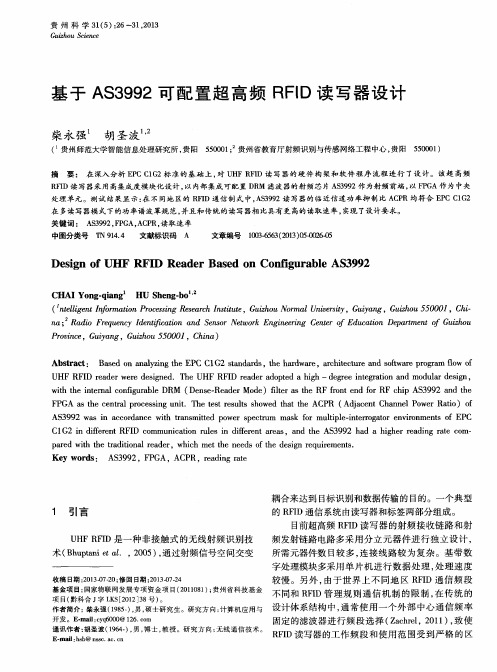

基于AS3992可配置超高频RFID读写器设计

关键词 : A S 3 9 9 2 , F P G A, A C P R, 读 取 速 率 中 图分类 号 T N 9 1 4 . 4 文献标 识 码 A 文章 编 号 1 0 0 3 - 6 5 6 3 ( 2 0 1 3 ) 0 5 - I X 1 2 6 - 0 5

De s i g n o f UH F RFI D Re a d e r Ba s e d o n Co n ig f ur a bl e AS 3 9 9 2

处理单元。测试结果显 示: 在 不同地 区的 R F I D通信制式 中, A S 3 9 9 2读 写器的I 晦近信道功 率抑制 比 A C P R均符合 E P C C 1 G 2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AS3990/AS3991UHF RFID Single Chip Reader EPC Class1 Gen2 CompatibleD a ta S h e e t1 General DescriptionThe AS3990/AS3991 UHF reader chip is an integrated analog front end and protocol handling systems for a ISO18000-6C 900MHz RFID reader system.Equipped with built-in programming options, the device is suitable for a wide range of UHF RFID applications. The R901G includes improved on-board VCO and internal PA.The reader configuration is achieved by selecting the desired protocol in control registers. Direct access to all control registers allows fine tuning of different reader parameters.Parallel or serial interface can be selected forcommunication between the host system (MCU) and the reader IC. When hardware coders and decoders are used for transmission and reception, data is transferred via 24 bytes FIFO register.In case of direct transmission or reception, coders and decoders are bypassed and the host system can service the analog front end in real time.The transmitter generates 20dBm output power into 50Ω load and is capable of ASK or PR-ASK modulation. The integrated supply voltage regulators ensure supply rejection of the complete reader system.The transmission system comprises low level datacoding. Automatic generation of FrameSync, Preamble, and CRC is supported.The receiver system allows AM and PM demodulation. The receiver also comprises automatic gain control option (patent pending) and selectable gain and signal bandwidth to cover a range of input link frequency and bit rate options.The signal strength of AM and PM modulation is measured and can be accessed in RSSI register.The receiver output is selectable between digitized sub-carrier signal and any of integrated sub-carrierdecoders. Selected decoders deliver bit stream and data clock as outputs.The receiver system also comprises framing system. This system performs the CRC check and organizes the data in bytes. Framed data is accessible to the host system through a 24 byte FIFO register.To support external MCU and other circuitry a 3.3V regulated supply and clock outputs are available. The regulated supply has 20mA current capability.The AS3990/AS3991 is available in a 64-pin QFN (9mm x 9mm), ensuring the smallest possible footprint.2 Key FeaturesISO18000-6C (EPC Gen2) full protocol support ISO18000-6A,B compatibility in direct mode Integrated low level transmission coding Integrated low level decoders Integrated data framing Integrated CRC checkingParallel 8-bit or serial 4-pin SPI interface to MCUusing 24 bytes FIFOVoltage range for communication to MCU between1.8V and 5.5VSelectable clock output for MCUIntegrated supply voltage regulator (20mA), whichcan be used to supply MCU and other external circuitryIntegrated supply voltage regulator for the RF outputstage, providing rejection to supply noiseInternal power amplifier (20dBm) for short rangeapplicationsModulator using ASK or PR-ASK modulation Adjustable ASK modulation index AM & PM demodulation ensuring no“communication holes” with automatic I/Q selectionBuilt-in reception low-pass and high-pass filters having selectable corner frequenciesSelectable reception gain Reception automatic gain controlAD converter for measuring TX power usingexternal RF power detectorDA converter for controlling external power amplifier Frequency hopping supportOn-board VCO and PLL covering complete RFIDfrequency range 840MHz to 960MHzOscillator using 20MHz crystal Power down, standby and active mode Can be powered by USB with no need for stepconversion3 ApplicationsThe device is an ideal solution for UHF RFID readersystems and hand-held UHF RFID readers.Figure 1. Block DiagramContents1 General Description (1)2 Key Features (1)3 Applications (1)4 Pin Assignments (5)Pin Descriptions (5)5 Absolute Maximum Ratings (8)6 Electrical Characteristics (9)7 Detailed Description (11)Supply (11)Power Modes (12)Host Communication (13)VCO and PLL (13)VCO and External RF Source (13)PLL (13)Chip Status Control (14)Protocol Control (14)Option Registers Preset (14)Transmitter (14)Normal Mode (14)Direct Mode (16)Modulator (17)Amplifier (17)Receiver (18)Input Mixer (18)RX Filter (18)RX Gain (19)Received Signal Strength Indicator (RSSI) (19)Reflected RF Level Indicator (19)Normal Mode (19)Direct Mode (21)Normal Mode With Mixer DC Level Output And Enable RX Output Available (21)ADC / DAC (21)DA Converter (21)AD Converter (22)Reference Oscillator (22)8 Application Information (23)Configuration Registers Address Space (23)Main Configuration Registers (24)Control Registers - Low Level Configuration Registers (25)Status Registers (30)Test Registers (32)PLL, Modulator, DAC, and ADC Registers (33)RX Length Registers (37)FIFO Control Registers (38)Direct Commands (39)Idle (80) (40)Soft Init (83) (40)Hop to Main Frequency (84) (40)Hop to Auxiliary Frequency (85) (40)Trigger AD Conversion (87) (40)Reset FIFO (8F) (40)Transmission With CRC (90) (40)Transmission With CRC Expecting Header Bit (91) (40)Transmission Without CRC (92) (41)Delayed Transmission With CRC (93) (41)Delayed Transmission Without CRC (94) (41)Block RX (96) (41)Enable RX (97) (41)EPC GEN2 Specific Commands (41)Query (98) (41)QueryRep (99) (41)QueryAdjustUp (9A) (41)QueryAdjustNic (9B) (41)QueryAdjustDown (9C) (42)ACK (9D) (42)NAK (9E) (42)ReqRN (9F) (42)Reader Communication Interface (42)Parallel Interface Communication (44)Serial Interface Communication (46)Timing Diagrams (47)Timing Parameters (48)FIFO (48)9 Package Drawings and Markings (49)10 Ordering Information (50)4 Pin AssignmentsPin DescriptionsTable 1. Pin DescriptionsPin Name Pin Number Pin Type Description COMN_A1BIDConnect de-coupling capacitor to VDD_5LFI COMP_B2BIDCOMN_B3BIDDAC4OUT DAC output for external amplifier support, Output Resistance of DAC pin is 1kΩVDD_5LFI5SUPI Positive supply for LF input stage, connect to VDD_MIX VSS6SUPI SubstrateMIX_INP7INP Differential mixer positive inputVSS8SUPI SubstrateMIX_INN9INP Differential mixer negative inputMIXS_IN10INP Single ended mixer inputVSN_MIX11SUPI Mixer negative supplyCBIB12BID Internal node de-coupling capacitor to GNDVDD_MIX13SUPO Mixer positive supply, internally regulated to 4.8VCBV514BID Internal node de-coupling capacitor to VDD_MIXVDD_TXPAB15SUPI Power Amplifier Bias positive supply. Connect to VDD_MIX VEXT 16SUPI Main positive supply input (5…5.5V)VEXT217SUPI PA positive supply regulator input (2.5… 5.5V)VDD_RF 18SUPO PA positive supply regulator output, internally regulated to 2…3.5V VDD_B 19SUPO PA buffer positive supply. Internally regulated to 3.4V RFOUTP_1201OUT PA positive RF outputRFOUT1 and RFOUT2 must be tied togetherRFOUTP_2211OUT VSN_1221SUPI PA negative supplyVSN_2231SUPI VSN_3241SUPI VSN_4251SUPI VSN_5261SUPI RFOUTN_1271OUT PA negative RF output or used in single ended mode.RFOUT1 and RFOUT2 must be tied together RFOUTN_2281OUT VSN_D 29SUPO Digital negative supplyOAD230BID Analog or digital received signal output and MCU support mode sense inputOAD 31BID Analog or digital received signal output RFONX 32OUT Low power linear negative RF output (~0dBm)RFOPX 33OUT Low power linear positive RF output (~0dBm)VDD_RFP 34SUPO RF path positive supply, internally regulated to 3.4V VSN_RFP 35SUPI RF path negative supply OSCI 36INP Crystal oscillator inputOSCO 37BID Crystal oscillator output or external 20MHz clock input VDD_D 38SUPO Digital part positive supply, internally regulated to 3.4V EN 39INP Enable input IRQ 40OUT Interrupt outputIO041BID I/O pin for parallel communication IO142BID IO243BID I/O pin for parallel communicationEnableRX input in case of direct mode IO344BID I/O pin for parallel communicationModulation input in case of direct modeIO445BID I/O pin for parallel communicationSlave select in case of serial communication (SPI)IO546BIDI/O pin for parallel communicationSub-carrier output in case of direct modeTable 1. Pin Descriptions Pin Name Pin NumberPin Type DescriptionNotes:1. BID: Bidirectional pin2. INP: Input pin3. OUT: Output pin4. SUPI: Supply Input pin5. SUPO: Supply Output pin .IO647BIDI/O pin for parallel communication.MISO in case of serial communication (SPI)Sub-carrier output in case of direct mode IO748BID I/O pin for parallel communication.MOSI in case of serial communication (SPI)CLSYS 49OUT Clock output for MCU operationCLK 50INP Clock input for MCU communication (parallel and serial)VDD_IO 51SUPI Positive supply for peripheral communication, connect to host positive supplyCD252BID Internal node de-coupling capacitor CD153BID AGD 54BID Analog reference voltage VSN_A 55SUPI Analog part negative supplyEXT_IN 56INP RF input in case external VCO is used VSN_CP 57SUPI Charge pump negative supplyADC 58IN ADC input for external power detector support VDD_A 59SUPO Analog part positive supply, internally regulated to 3.4V VCO 60INP VCO inputVOSC 61BID Internal node de-coupling capacitor CP 62OUT Charge pump outputVDDLF 63SUPI Positive supply for LF processing, internally regulated to 3.4COMP_A 64BID Internal node, connect de-coupling capacitor to VDD_5LFI EXP_PAD65SUPIExposed paddle, must be tied to GND1.Internal Power amplifier is not available on AS3990.Table 1. Pin Descriptions Pin Name Pin NumberPin Type DescriptionData Sheet - A b s o l u te M a x i m u m R a ti n g s5 Absolute Maximum RatingsStresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in ElectricalCharacteristics on page 9 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Table 2. Absolute Maximum RatingsParameter MinMax Units CommentsSupply voltage, V EXT 5.5V Positive voltage other pads V S ± 0.3V Negative voltage other pads-0.3V Output current, I O±100mA Maximum junction temperature T J 125ºC The maximum junction temperature for continuous operation is limited by packageconstraints.Storage temperature range, T stg-55+150ºCLead temperature 1,6 mm (1/16 inch)from case for 10 seconds260ºCThe reflow peak soldering temperature(body temperature) is specified according IPC/JEDEC J-STD-020C“Moisture/Reflow Sensitivity Classification for non-hermetic Solid State Surface Mount Devices”.ESD rating11.This integrated circuit can be damaged by ESD. We recommend that all integrated circuits are handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet the published specifications. RF integrated circuits are also more susceptible to damage due to use of smaller protection devices on the RF pins, which are needed for low capacitive load on these pins.IO pins, HBM 2kV RF pins, HBM1kV6 Electrical CharacteristicsV EXT = 5.3V, typical values at 25ºC, unless otherwise noted.Table 3. Electrical CharacteristicsSymbol Parameter Conditions Min Typ Max UnitsI VEXT Supply current without PAdriver currentV EXT Consumption80mAI VEXT+I VEXT2Supply Current for AS3991 andinternal PA11.Internal PA is available on AS3991only.V EXT2 Consumption,V EXT2 = 2.5V310mAI STBY Standby current3mAI PD Supply current in power-downmode All system disabled includingsupply voltage regulators20100µA210V AGD AGD voltage 1.5 1.6 1.7V V POR Power on reset voltage (POR) 1.4 2.0 2.5VV VDD Regulated supply for internalcircuitry and for external MCU 3.2 3.4 3.6VV DD RF Regulated supply for internalPA 1.92 2.1VV VDD MIX1Regulated supply for mixers, bitvext_low=LThe difference between theexternal supply and the regulatedvoltage is higher than 250mV4.5 4.85.1VV VDD MIX2Regulated supply for mixers, bitvext_low=HThe difference between theexternal supply and the regulatedvoltage is higher than 250mV3.5 3.7 3.9VP PSSR Rejection of external supplynoise on the supply regulatorsThe difference between theexternal supply and the regulatedvoltage is higher than 250mV26dBP RFAUX Auxiliary output power0dBm P RFOUT Internal PA output power120dBm R RFIN RFIN input resistance100ΩV SENS Input sensitivity-66dBm 1dB CP Input 1dB compression point10dBm IP3Third order intercept point21dBm T REC Recovery time after modulation Maximum LF selected10µs Logic Input/OutputMax. CLK frequency1MHz V LOW Input logic low0.2V DD_IO V HIGH Input logic high0.8V DD_IO R IO Output resistance IO0…IO7low_io = H for VDD_IO<2.7V400800ΩR CL SYS Output resistance CL SYS low_io = H for VDD_IO<2.7V200ΩTable 4. Recommended Operating ConditionsSymbol Parameter Conditions Min Typ Max Units Supply Voltage 5.0 5.3 5.5V Supply voltage (bit vext_lowset) 4.1VT J Operating virtual junctiontemperature range-40125ºC T AMB Ambient temperature-4085ºC Rth junction to exposed die padº/W7 Detailed DescriptionThe RFID reader IC comprises complete analog and digital functionality for reader operation including transmitter and receiver section with complete EPC Gen2 or ISO18000-6C digital protocol support. To integrate as many components as possible, the device also comprises an on-board PLL section with integrated VCO, supply section, DAC and ADC section, and host interface section. In order to cover a wide range of possibilities, there is also Configuration registers section that configures operation of all blocks.For operation, the device needs to be correctly supplied via. VEXT and VEXT2 pins and enabled via. EN pin (Refer Supply on page 11 for connecting to supply and Power Modes on page 12 about operation of the EN pin). At power-up the configuration registers are preset to a default operation mode. The preset values are described in the Configuration Registers Address Space on page 23 below each register description table. It is possible to access and change registers to choose other options.The communication between the reader and the transponder follows the reader talk first method. After power-up and configuring IC, the host system starts communication by turning on the RF field by setting option bit rf_on in the ‘Chip status control register’ (00) (see Table 13) and transmitting the first protocol command (Select in EPC Gen2). Transmitting and receiving is possible in the following two modes:1. Normal Data Mode: In this mode, the TX and RX data is transferred through the FIFO register and all protocoldata processing is done internally.2. Direct Data Mode: In this mode, the data processing is done by the host system.SupplyThe effective supply system of the chip decreases the influence of the supply noise and interference and thus improves de-coupling between different building blocks. A set of 3.4V regulators is used for supplying the reference block, AD and DA converters, low frequency receiver cells, the RF part, and digital part. It is possible to use the digital part supply VDD_D for supplying the external MCU with a current consumption up to 20mA. The input pin for the regulators is VEXT. The output pins for regulators are VDD_A, VDD_LF, VDD_D, VDD_RFP and VDD_B. Each of the pins require stabilizing capacitors to connected ground (2.2…10µF and 10…100nF) in parallel. Depending on quality of the capacitors, 100pF could be required.An additional 4.8V regulator is used for the input RF mixers supply. The input of this regulator is VEXT, output is VDD_MIX pin. For correct operation of the 4.8V regulator, the VEXT voltage needs to be between 5.3V and 5.5V. VDD_MIX needs de-coupling capacitors to VDD_MIX like other VDD pins.In case lower VEXT supply voltage is used (down to 4.1V), two option bits have to be set to optimize the chip performance to the lower supply. The vext_low in the ‘TRcal high and misc register’ (05) bit decreases VDD_MIX voltage to 3.7V to maintain the regulators PSSR and the ir<1> bit in the ‘RX special setting 2’ (0A) adapts mixer’s internal operating point to lower supply. Adaptation to low supply is implemented in differential mixer only. The consequence of the decreased supply is lower mixer’s input range.VDD_5LFI and VDD_TXPAB pins are supply input pins and should be connected to VDD_MIX. The internal 20dBm power amplifier 1has an internal regulator from 2…3.5V. The output voltage selection is done by reg2v1:0 option bits in the ‘Regulator and IO control register’ (0B) (see Table 24).The input pin is VEXT2 and output is VDD_RF. For optimum noise rejection performance, the input voltage at VEXT2 pin needs to be at least 0.5V above the regulated supply output. Connecting VEXT2 directly to VEXT is possible only at the expense of increasing IC’s power dissipation and decreasing the maximum operating temperature.A separate I/O supply pin (VDD_IO) is used to supply the internal level shifters for communication interface to the host system (MCU). VDD_IO should be connected to MCU supply to ensure proper communication between the chip and MCU. In case the MCU is supplied by VDD_D from the reader IC also VDD_IO should be connected to VDD_D.Power ModesThe chip has three power modes.Power Down Mode: The power down mode is activated by EN pin low (EN=L). For correct operation, the OAD2pin should not be connected.Normal Mode: The normal mode is entered by EN=H. In this case all supply regulators, reference voltage system,crystal oscillator, RF oscillator and PLL are enabled. After the crystal oscillator stabilizes, the CLSYS clock becomes active (default frequency is 5MHz) and the chip is ready to move to transmit or receive operation.Standby Mode: The standby mode is entered from normal mode by option bit stby=H. In the standby mode theregulators, reference voltage system, and crystal oscillator are operating in low power mode; but the PLL,transmitter output stages and receiver are switched off. All the register settings are kept while switching between standby and normal mode.Power Down with MCU Support mode intends to support the MCU if the majority of the reader IC is in power down. This mode is enabled by connecting 10k Ω resistor between OAD2 pin and ground. During EN=L period, the VDD_D regulator is enabled in low power mode and the CLSYS frequency is 60kHz typically.It is also possible to trigger temporary normal mode from power down mode (EN=L) by pulling shortly the OAD2 pin low via 10k Ω or less. After the crystal oscillator is stable and the CLSYS clock output is active, the chip waits for approximately 200µs and then changes back to the power down mode. Using this function, the superior system can wake up the reader IC and MCU that are both in the power down mode. If the MCU during 200µs period finds out that the RFID system must react, it confirms the normal mode by setting EN high.1.Internal PA is available on AS3991only.Table 5. AS3990/AS3991 Power ModesPower mode EN OAD2Std by Power down L -X Power down SYSCLK of 60kHz L 10k to GNDX Normal power HX X Stand by XH Listen modeL 10k and falling edgeXHost CommunicationAn 8-bit parallel interface (pins IO0 to IO7) with two control signals (CLK, IRQ) forms the main communication system. It can also be changed (by hardwiring some of the 8 I/O pins) to a serial interface. The data handling is done by a 24 byte FIFO register used in both directions, transmission and reception. For more details, refer Reader Communication Interface on page 42.The signal level for communication between the host system (MCU) is defined by the supply voltage connected to VDD_IO pin. Communication is possible in wide range between 1.8V and 5.5V. In case the pull-up output resistance at VDD_IO below 2.7V is to high, it can be decreased by setting option bit vdd_io_low in the ‘TRcal High and Misc register’ (05). In case the MCU is supplied from the reader IC, then both the MCU supply and VDD_IO pin need to be connected to VDD_D.CLSYS output level is defined by the VDD_IO voltage. It is also possible to configure CLSYS to open drain N-MOS output by setting the option bit open_dr in the in the ‘TRcal high and misc register’ (05), (see Table 18). This function can be used to decrease amplitude and harmonic content of the CLSYS signal and decrease the cross-talk effects that could corrupt operation of other parts of the circuit.VCO and PLLThe PLL section is composed of a voltage control oscillator (VCO), prescaler, main and reference divider, phase-frequency detector, charge pump, and loop filter. All building blocks excluding the loop filter are completely integrated. Operating range is 860MHz to 960MHz.VCO and External RF SourceInstead of the internal PLL signal, an external RF source can be used. The external source needs to be connected to EXT_IN pin and option bit eext_in in the ‘PLL A/B divider auxiliary register‘ (17) (see Table 36) needs to be set high. The EXT_IN input optimum level is 0dBm with a DC level between 0V and 2V.It is also possible to use external VCO and internal PLL circuitry. In this case, the output of the external VCO (0dBm) needs to be connected to EXT_IN, option bits eext_in and epresc in the ‘PLL A/B divider auxiliary register’ (17) both need to be set high. The charge pump output pin CP needs to be connected to the external loop filter input and loop filter output to the external VCO input. This configuration is useful in case the application demands better phase noise performance than the completely integrated oscillator offers.The internal on-board VCO is completely integrated including the variable capacitor and inductor. The control input is pin VCO; input range is between 0 and 3.3V. The option bits eosc<2:0> in the ‘CLSYS, analog out and CP control’ (14) (Table 33) can be used for oscillator noise and current consumption optimization. Option bit lev_vco in the ‘PLL A/B divider auxiliary register’ (17) (see Table 36) is used to optimize the internal VCO output level to other RF circuitry demands. VCO and CP pin valid range is between 0.5V and 2.9V.AS3991 and above have internal VCO set to a frequency range around 1800MHz, later internally divided by two for decreasing the VCO pulling effect. The tuning curve of 1800MHz VCO is divided into 16 segments to decrease VCO gain and attain lowest possible phase noise.Configuration of the 1800MHz VCO tuning range can be manual using option bits vco_r<3:0> in the ‘CL_SYS, analog out and CP control’ register (14) or automatic using L-H transition on option bit auto in the same register. The device allows measurement of the VCO voltage using option bit mvco and reading out the 4 bits result of the automatic segment selection procedure, both in the same register.PLLThe divide by 32/33 prescaler is controlled by the main divider. The main divider ratio is defined by the ‘PLL A/B divider main register’ (16). The low ten bits in the three bytes deep register define A value and the next ten bits define B value. The A and B values define the main divider division ratio to N=B*32+A*33. The reference clock is selectable by RefFreq<2:0> bits in the ‘PLL R, A/B divider main register’ (16) (see Table 35). The available values are 500 kHz, 250 kHz, 200 kHz, 100 kHz, 50 kHz, 25 kHz. Charge pump current is selectable between 150µA and 1200µA using option bits cp1:0 in the ‘CL_SYS, analog out and CP control register’ (14) (see Table 33). The cp<3> is used to change the polarity (direction) of the charge pump output.The frequency hopping is supported by direct commands ‘Hop to main frequency’ (84) and ‘Hop to auxiliary frequency’ (85). The hopping is controlled by host system (MCU) using two configuration registers for two frequencies. Before enabling the RF field, the host system needs to configure the PLL by writing the ‘CL_SYS, analog out and PLL register’ (09) and the ‘PLL R, A/B divider main’ (16) registers. Any time during operating at the first selected frequency, the external system can configure the three bytes deep ‘PLL A/B divider auxiliary (17)’ register.Hopping to the second frequency is triggered, if direct command ‘Hop to auxiliary frequency’ is sent. Hop to the third frequency is similar: the register ‘PLL A/B divider main (16)’ can be written any time the external system has free resources and actual hop is triggered by direct command ‘Hop to main frequency’.Chip Status ControlIn the ‘Chip status control register’ (00) (see Table 13), main functionality of the chip is defined. By setting the rf_on bit in the ’Chip control register’ (00), the transmit and receive part are enabled. The initial RF field ramp-up is defined with the Tari1:0 option bits in the ‘Protocol control register’ (01) (see Table 14). It is also possible to slow down the initial RF field ramp by option bits trfon1:0 in the ‘Modulator control register’ (15) (see Table 34). The available values are 100µs, 200µs, and 400µs.The host system can check whether the field ramp-up is finished via the rf_ok bit in the ‘AGC and internal status register’ (0E) (see Table 27), which is set high when ramp-up is finished. By setting the rf_on bit low, the field will ramp-down similarly to the ramp-up transient. It is also possible to enable receiver operation by setting rec_on bit. Theagc_on and agl_on bits enables the (Automatic Gain Control) AGC and (Automatic Gain Leveling) AGL functionality, dac_on enables DA converter, bit direct enables the direct data mode, and stby bit moves chip to the stand-by power mode.Protocol ControlIn the ‘Protocol control register’ (01) (see Table 14), the main protocol parameters are selected (Tari value and RX coding for EPC Gen2 protocol). The Gen2 Protocol is configured by setting Prot<1:0> bits to low. The dir_mode<6> bit defines type of output signals in case the direct mode is used. The rx_crc_n<7> bit high defines reception in case the user does not want to check CRC internally. In this case, the CRC is not checked but is just passed to the FIFO like other data bytes. In the EPC Gen2, this function is useful in case of truncated EPC reply where the ‘CRC’ transponder transmits is not valid CRC calculated over actual transmitted data.Option Registers PresetAfter power up (EN low to high transition), the option registers are preset to values that allow default reader operation. Default transmission uses Tari 25µs, PW length is 0.5Tari, TX one length is 2 Tari, and RTcal is 133µs. Default reception uses FM0 coding with long preamble, link frequency 160kHz. Default operation is set to internal PLL with internal VCO, differential input mixers, low power output (RFOPX, RFONX), and DSB-ASK transmit modulation. TransmitterTransmitter section comprises of protocol processing digital part, shaping, modulator and amplifier circuitry. The RF carrier is modulated with the transmit data and amplified for transmission.Normal ModeIn normal mode, all signal processing (protocol coding, adding preamble or frame-sync and CRC, signal shaping, and modulation) is done internally.The external system (MCU) triggers the transmission and loads the transmit data into the FIFO register. The transmission is started by sending the transmit command followed by information on the number of bytes that should be transmitted and the data. The number of bytes needs to be written in the ‘TX length’ registers and the data to the FIFO register. Both can be done by a single continuous write. The transmission actually starts when the first data byte is written into the FIFO.The second possibility is to start transmission with one of the direct Gen2 commands (Query, QueryRep, QueryAdjust, ACK, NAK, ReqRN). In this case, the transmission is started after receiving the command.In case the transmission data length is longer than the size of the FIFO, the host system (MCU) should initially fill the FIFO register with up to 24 bytes. The reader chip starts transmission and sends an interrupt request when only 3 bytes are left in the FIFO. When interrupt is received, the host system needs to read the ‘IRQ status register’ (0C) (see Table 25). By reading this register, the host system is notified by the cause of the interrupt and the same reading also clears the interrupt. In case the cause of the interrupt is low FIFO level and the host system did not put all data to the FIFO, the remaining data needs to be sent to FIFO, again according to the available FIFO size. In case all transmission data was already sent to the FIFO, the host system waits until the transmission runs out. At the end of the transmit operation, the external system is notified by another interrupt request with a flag in the IRQ register that signals the end of transmission.。