PCM编解码芯片中低成本低功耗SAR ADC设计

基于新型电容阵列切换方式的10位低功耗SAR ADC

基于新型电容阵列切换方式的10位低功耗SAR ADC孙甜甜【摘要】文中提出了一种10位低功耗逐次逼近(Successive-Approximation-Register,SAR)模/数转换器(Analog-to-Digital Converter,ADC),内部数/模转换网络采用一种新型的电容阵列开关切换方式,通过分段电容阵列、时序初始化和子参考电压来降低能耗,相比传统结构电容阵列的转换能耗减小了97.6%,单位电容数量减小了87%.整个ADC采用65 nm CMOS工艺进行设计,当采样频率为50 KS/s,输入正弦波信号频率为1.5 kHz左右时,ADC的有效位数(Effective Number of Bits,ENOB)为9.91位,总功耗低于450 nW,面积为136μm×176μm,非常适合植入式生物医疗电子的应用.%A 10-bit low power SAR (Successive-Approximation-Register, SAR) ADC (Analog-to-Digital Converter, ADC) is proposed in this paper. The internal digital-to-analog conversion is designed with an improved capacitive switching scheme. By using split-capacitor array, sequence initialization and sub-reference voltage, the switching energy is reduced by 97.6% and the number of the unit capacitor is reduced by 87%, compared with the traditional structure. The 10-bit ADC is designed based on a 65nm CMOS process. When 1.5 kHz fully-differential input signals are sampled at 50 KS/s sampling rate , the ENOB of the ADC is 9.91. The power consumption of this ADC is less than 450nW , and the area is 136μm × 176μm, making this proposed ADC very suitable to implantable bioelectronics.【期刊名称】《电子设计工程》【年(卷),期】2017(025)002【总页数】5页(P80-84)【关键词】模/数转换器;逐次逼近;新型电容开关切换技术;分段电容;低功耗【作者】孙甜甜【作者单位】西安邮电大学电子工程学院,陕西西安 710121【正文语种】中文【中图分类】TP302目前集成电路特征尺寸已经减小到纳米级,片上系统(System-on-Chip,SoC)的集成度也大幅提高。

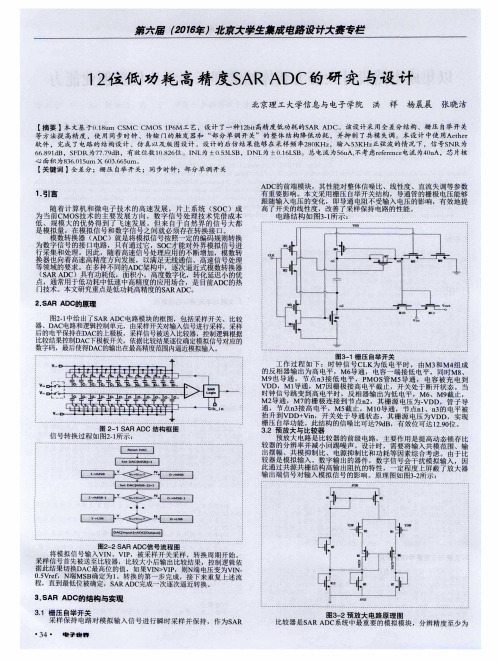

12位低功耗高精度SAR ADC的研究与设计

【 关键 词 】 全 差分 ;栅 压 自举 开关 ;同步 时钟 ;部 分单调 开 关

一 一 椭 一 ~ 溯 ~ 一 一 一 吨 一 毗 一 黼 一 狮 够 一 渤 ~ 一 慌 ~ 一 髓

图3 — 1栅压 自举开关

舭 一 ~ 一 一 一 m 触 一 一 ~ 舢 一 一 ~ 棚 恤 雌 糊 一 潞 觥 一 பைடு நூலகம்

图2 — 1 S A l AD i C结构框 图

信 号转 换过 程 如 图2 . 1 所示 :

预放 大 电路 是 比较 器 的前 级 电路 ,主要 作 用是 提 高动态 锁存 比 较器 的分 辨 率并 减小 回踢 噪 声 。设计 时 ,需要将 输 入共 模 范 围、输 出摆 幅 、共模 抑 制 比、 电源抑 制 比和 功耗 等 因素综 合 考虑 。 由于 比 较器 是模 拟输 入 、数 字输 出 的器件 ,数字 信号会 干 扰模 拟输 入 , 因 此通 过共 源共 栅 结构 高输 出 阻抗 的特 性 ,一定 程度 上屏 蔽 了放 大器 输 出端信 号对输 入 模拟 信号 的影 响 。原理 图如 图3 — 2 所示:

方 法提 高精 度 。使 用 同 步 时钟 、传输 门的 触 发 器和 “ 部 分 单调 开 关” 的 整体 结 构 降 低 功耗 ,并 抑 制 了共 模 失 调 。 本设 计 中使 用A e t h e r 软 件 ,完成 了电路 的结 构设 计 、仿 真 以及版 图设 计 。设 计 的后 仿 结 果 能够 在采 样 频 率2 8 0 K Hz ,输 入5 3 K Hz 正 弦波 的 情 况下 ,信 号S NI K  ̄ 6 6 . 8 9 1 d B.S F D R为7 7 . 7 9 d E,有效位 数 1 ( ) . 8 2 6 位 。I NL 为 ±( 1 5 3 L S B,DNL d d / ±( ) . 1 6 L S B。总 电流 为5 6 u A , 不考 虑r e f e r e n c e 电流 为4 0 u A,芯 片核

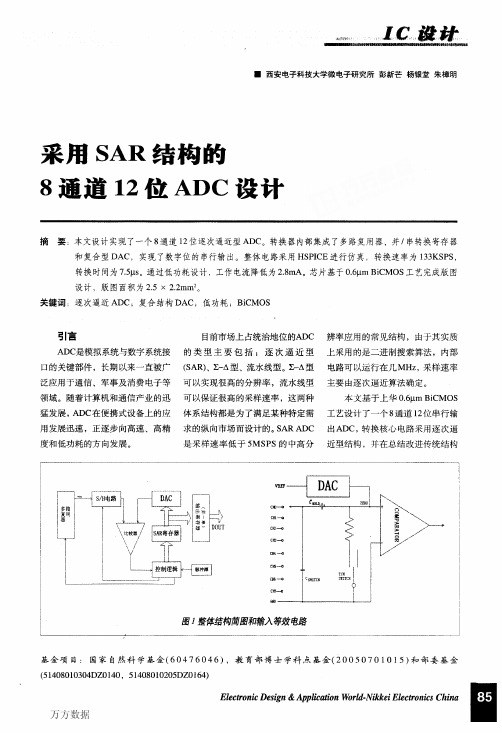

采用SAR结构的8通道12位ADC设计

一

采用SAR结构的8通道12位ADC设计

作者: 作者单位: 刊名:

英文刊名: 年,卷(期): 被引用次数:

彭新芒, 杨银堂, 朱樟明 西安电子科技大学微电子研究所

电子设计应用 ELECTRONIC DESIGN & APPLICATION WORLD FOR DESIGN AND APPLICATION ENGINEERS 2006,(11) 0次

以随着位数的增加,其所需元器件 的数量会呈几何级数增加,这是它 的缺点。单独用这种结构来做一个 DAc的情况比较少见,但是它却在 8位以下的sAR ADC中常用到。电 容电荷型DAc的优点是精度较高, 但缺点是面积大,对寄生电容敏 感,而且还需要两相时钟,增加了 设计制造的复杂度。

基于CMOS工艺的低功耗SAR ADC设计

基于CMOS工艺的低功耗SAR ADC设计基于CMOS工艺的低功耗SAR ADC设计摘要:随着物联网、5G通信等应用不断发展,对于低功耗高精度的模拟-数字转换器(ADC)需求也日益增加。

本文主要研究了基于CMOS工艺的低功耗逐次逼近型(SAR)ADC设计。

首先介绍了ADC的基本原理和工作模式,然后详细讲解了SAR ADC的原理及其与其他ADC的对比。

接着提出了低功耗的设计方法,包括降低比较器功耗、减小电容和最优控制电压等。

最后,以55nm CMOS工艺为例,设计了一个12位分辨率、采样率100kS/s的SAR ADC,并进行了仿真验证。

结果表明,该ADC的功耗仅为305nW,相较于传统的SAR ADC设计,具有显著的功耗优势。

因此,该设计方法可为减少ADC功耗提供一个重要的思路。

关键词:ADC;SAR ADC;CMOS工艺;低功耗;比较器;电容1. 引言模拟-数字转换器是一类重要的电路,主要用于将模拟信号转换为数字信号。

在现代电子技术应用中,模拟-数字转换器广泛应用于通信、控制、传感等领域。

其目的是将不同方法和源产生的不同物理变量转化为统一的数字信号,实现数字化处理和信息通信。

随着技术的发展,对于低功耗高精度的模拟-数字转换器(ADC)需求也越来越大。

低功耗的ADC不仅能延长电池寿命,还能减少热的产生,从而有利于系统可靠性和稳定性。

而逐次逼近型(SAR)ADC则是一种逐步逼近法的ADC,具有采样速度快、抗噪声能力强、结构简单等优点,因此成为了低功耗ADC设计的主流。

本文的主要研究内容是基于CMOS工艺的低功耗SAR ADC设计。

首先介绍了ADC的基本原理和工作模式,然后详细讲解了SAR ADC的原理及其与其他ADC的对比。

接着提出了低功耗的设计方法,包括降低比较器功耗、减小电容和最优控制电压等。

最后,以55nm CMOS工艺为例,设计了一个12位分辨率、采样率100kS/s的SAR ADC,并进行了仿真验证。

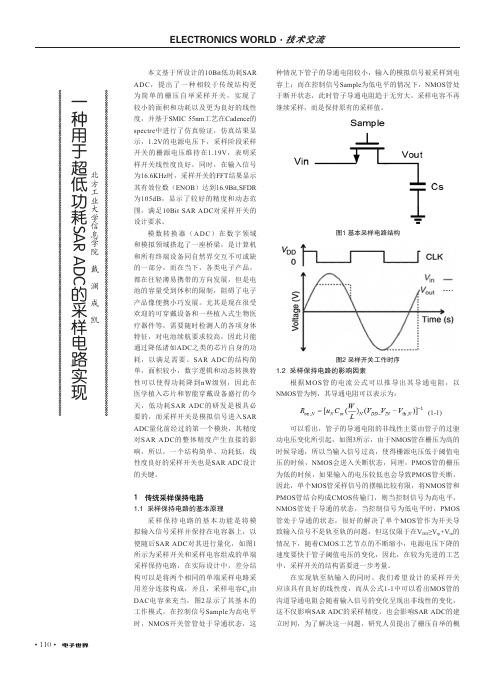

一种用于超低功耗SAR ADC的采样电路实现

• 110•本文基于所设计的10Bit 低功耗SAR ADC ,提出了一种相较于传统结构更为简单的栅压自举采样开关,实现了较小的面积和功耗以及更为良好的线性度,并基于SMIC 55nm 工艺在Cadence 的spectre 中进行了仿真验证,仿真结果显示,1.2V 的电源电压下,采样阶段采样开关的栅源电压维持在1.19V ,表明采样开关线性度良好,同时,在输入信号为16.6KHz 时,采样开关的FFT 结果显示其有效位数(ENOB )达到16.9Bit,SFDR 为105dB ,显示了较好的精度和动态范围,满足10Bit SAR ADC 对采样开关的设计要求。

模数转换器(ADC )在数字领域和模拟领域搭起了一座桥梁,是计算机和所有终端设备同自然界交互不可或缺的一部分,而在当下,各类电子产品,都在往轻薄易携带的方向发展,但是电池的容量受到体积的限制,阻碍了电子产品像便携小巧发展。

尤其是现在很受欢迎的可穿戴设备和一些植入式生物医疗器件等,需要随时检测人的各项身体特征,对电池续航要求较高,因此只能通过降低诸如ADC 之类的芯片自身的功耗,以满足需要。

SAR ADC 的结构简单,面积较小,数字逻辑和动态转换特性可以使得功耗降到nW 级别,因此在医学植入芯片和智能穿戴设备盛行的今天,低功耗SAR ADC 的研发是极具必要的,而采样开关是模拟信号进入SAR ADC 量化前经过的第一个模块,其精度对SAR ADC 的整体精度产生直接的影响,所以,一个结构简单、功耗低,线性度良好的采样开关也是SAR ADC 设计的关键。

1 传统采样保持电路1.1 采样保持电路的基本原理采样保持电路的基本功能是将模拟输入信号采样并保持在电容器上,以便随后SAR ADC 对其进行量化,如图1所示为采样开关和采样电容组成的单端采样保持电路,在实际设计中,差分结构可以是将两个相同的单端采样电路采用差分连接构成,并且,采样电容C S 由DAC 电容来充当,图2显示了其基本的工作模式,在控制信号Sample 为高电平时,NMOS 开关管管处于导通状态,这种情况下管子的导通电阻较小,输入的模拟信号被采样到电容上;而在控制信号Sample 为低电平的情况下,NMOS 管处于断开状态,此时管子导通电阻趋于无穷大,采样电容不再继续采样,而是保持原有的采样值。

10位700MS-s单通道高速SAR ADC的设计

10位700MS-s单通道高速SAR ADC的设计10位700MS/s单通道高速SAR ADC的设计随着现代通信技术和多媒体应用的迅速发展,对于高速模数转换器(ADC)的需求也越来越大。

高速ADC作为数字信号处理链中的重要组成部分,对于数据的快速和准确转换至关重要。

本文将介绍一个经过优化和设计的10位700MS/s单通道高速逐次逼近器型(SAR)ADC。

首先,我们需要了解SAR ADC的基本工作原理。

SAR ADC 是一种逐次逼近式的ADC,其通过逐位逼近法将模拟信号转换为数字信号。

它的工作原理是通过比较输入信号与DAC输出信号的大小,然后根据比较结果进行逐步逼近,直到得到最终数字输出。

SAR ADC由比较器、数字逻辑和DAC(数字模拟转换器)组成。

为了达到高速转换的要求,我们首先需要高速的比较器。

比较器的速度主要受限于其增益带宽积(GBW)和噪声功耗比(NPB)两个指标。

为了提高比较器的速度性能,我们选用了高GBW的CMOS比较器作为基础结构,并采用了合适的增益控制电路和偏置电路,以提高其速度和减小误差。

其次,数字逻辑部分需要能够支持高速数据处理。

为了实现700MS/s的转换速度,我们采用了并行多通道处理的方法,即将输入信号分为多个通道进行同时处理,然后再将结果合并得到最终输出。

这样不仅提高了转换速度,还减小了数字逻辑的复杂度。

同时,为了进一步优化逻辑电路,我们采用了流水线架构和并行计算的方法,提高了整体性能和效率。

最后,DAC部分需要有足够高的精度和速度。

为了达到10位的精度要求,我们选用了高分辨率的DAC结构,并采用了优化的校准算法和电路设计,以提高传输精度和抗噪性能。

同时,为了减小DAC的开关功耗和电流波动对转换速度的影响,我们采用了低功耗的开关电路和合适的电源管理策略。

在硬件实现方面,我们将所有模块进行了综合布局和优化,以降低集成电路的面积和功耗,并提高整体性能。

为了进一步减小噪声和时序问题,我们采用了合适的线路布局和功率供给策略。

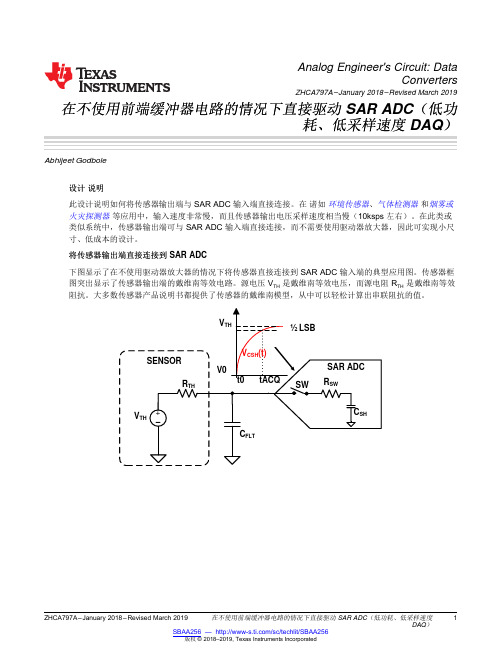

不使用前端缓冲器电路的情况下直接驱动 SAR ADC(低功耗、低采样速度 DAQ)说明书

1ZHCA797A–January 2018–Revised March 2019在不使用前端缓冲器电路的情况下直接驱动SAR ADC (低功耗、低采样速度DAQ )Analog Engineer's Circuit:DataConvertersZHCA797A–January 2018–Revised March 2019在不使用前端缓冲器电路的情况下直接驱动SAR ADC (低功耗、低采样速度DAQ )Abhijeet Godbole设计说明此设计说明如何将传感器输出端与SAR ADC 输入端直接连接。

在诸如环境传感器、气体检测器和烟雾或火灾探测器等应用中,输入速度非常慢,而且传感器输出电压采样速度相当慢(10ksps 左右)。

在此类或类似系统中,传感器输出端可与SAR ADC 输入端直接连接,而不需要使用驱动器放大器,因此可实现小尺寸、低成本的设计。

将传感器输出端直接连接到SAR ADC下图显示了在不使用驱动器放大器的情况下将传感器直接连接到SAR ADC 输入端的典型应用图。

传感器框图突出显示了传感器输出端的戴维南等效电路。

源电压V TH 是戴维南等效电压,而源电阻R TH 是戴维南等效阻抗。

大多数传感器产品说明书都提供了传感器的戴维南模型,从中可以轻松计算出串联阻抗的值。

2ZHCA797A–January 2018–Revised March 2019在不使用前端缓冲器电路的情况下直接驱动SAR ADC (低功耗、低采样速度DAQ )规格参数计算值仿真值测得值瞬态ADC 输入趋稳误差<0.5LSB <100.5µV 36.24µV 不适用阶跃输入满量程 3.15V 3.15V 3.14978输入源阻抗(R TH )10k Ω10k Ω10.01k Ω滤波电容值(C FLT )680pF 680pF 不适用ADC 采样速度10ksps10ksps10ksps设计注意事项1.确定输入信号的源阻抗。

应用于生物电信号检测的低功耗SAR ADC电路设计

第 11期 陈 磊,等:应用于生物电信号检测的低功耗 SARADC电路设计 65

Байду номын сангаас

三个部分,图 1为 10位 SARADC的结构示意图。其中电 容网络作为采样保持电路和 DAC电容阵列,因此 ADC不 需要单独的采 样 保 持 电 路,为 了 获 得 好 的 精 确 度,ADC采 用全差分结构。假如 Vip>Vin,则 DACP(比 较 器 正 端 输 入)的电压大于 DACN(比较器负端输入)的电压,比较器 输出为 1,反之输出为 0,得到最高位数字码;然后通过数字 逻辑控制 DAC电容二进制切换,改变权重,比较器开始二 次比较,得到次高位数字码。该过程一直重复直到 LSB被 判决。最后,将每步切换的结果并行同步输出,完成采样值 的数据转换。

64 传感器与微系统(TransducerandMicrosystemTechnologies) 2020年 第 39卷 第 11期 DOI:10.13873/J.1000—9787(2020)11—0064—03

应用于生物电信号检测的低功耗 SARADC电路设计

陈 磊,李天望

0 引 言 近几年来,应用在生物医学上的便携式、可穿戴式以及

植入式无线传感设备正在快速发展,而这些可移动小型化 的检测系统需要有 很 强 的 续 航 能 力。 模 数 转 换 器 (ADC) 将采集到的模拟信号转换为数字信号,是监测系统最核心 的模块之一[1,2]。生物电信号采集系统中的 ADC采样频率 通常低于 1MHz以下,需要 8~12位的中等精度和极低的 功耗。由于逐次逼近型模数转换器(SARADC)通常被用 在中速和中等分辨率下,具备低功耗、面积小和随着工艺的 进步,功耗变得更小的优势,因此成为低功耗生物医学电信 号检测系统的最优选择。