基于测频原理的频率计

《等精度频率计》课件

分析等精度频率计测量误差的主要来源,如信号源的频率稳定度、 计数器的计数误差等。

误差传递

研究误差在测量过程中的传递规律,为减小误差提供依据。

误差补偿

根据误差ห้องสมุดไป่ตู้析结果,采取相应的补偿措施,减小等精度频率计的测量 误差。

04

等精度频率计的性能测 试与评估

测试环境与设备

测试环境

实验室环境,确保电源稳定、温度适 宜、湿度适中。

应用领域拓展

通信领域

等精度频率计在通信领域的应用越来越广泛,如信号发生器、频 谱分析仪等。

测量测试

等精度频率计在测量测试领域的应用也越来越广泛,如时间频率测 量、电子元件测试等。

物联网领域

等精度频率计在物联网领域的应用也越来越广泛,如智能家居、智 能农业等。

未来发展方向

更高精度

随着科技的发展,对频率计的测量精度要求越来越高,未来等精 度频率计将向更高精度方向发展。

02

它采用等精度测量技术,消除了传统频率计由于时基不稳定而

引起的测量误差。

等精度频率计具有广泛的应用,如电子测量、通信、雷达、导

03

航等领域。

等精度频率计的原理

等精度频率计基于等精度测频 原理,采用高稳定的晶体振荡 器作为时基,对输入信号进行

计数和测量。

它通过计数输入信号在一定 时间内的周期数,再根据时 基的频率计算出输入信号的

宽测量范围

等精度频率计能够测量低频信 号和高频信号,测量范围较广 。

可扩展性

等精度频率计可以与其他测量 仪器进行集成,实现更复杂的 测量功能。

02

等精度频率计的应用

测量信号频率

测量信号频率是等精度频率计的基本 应用,它可以准确测量各种信号源的 频率,包括正弦波、方波、脉冲波等 。

数字频率计的原理

1.数字频率计的原理

所谓频率,就是周期性信号在单位时间 (1s) 内变化的次数.若在一定时间间隔T内测得这个周期性信号的重复变化次数为N,则其频率可表示为 fx=N/T 。

因此,可以将信号放大整形后由计数器累计单位时间内的信号个数,然后经译码、显示输出测量结果,这是所谓的测频法。

可见数字频率计主要由放大整形电路、闸门电路、计数器电路、锁存器、时基电路、逻辑控制、译码显示电路几部分组成,

图1 总体结构图

从原理图可知,被测信号Vx经放大整形电路变成计数器所要求的脉冲信号Ⅰ,其频率与被测信号的频率fx相同。

时基电路提供标准时间基准信号Ⅱ,具有固定宽度T的方波时基信号II作为闸门的一个输入端,控制闸门的开放时间,被测信号I从闸门另一端输入,被测信号频率为fx,闸门宽度T,若在闸门时间内计数器计得的脉冲个数为N,则被测信号频率fx=N/THz。

可见,闸门时间T决定量程,通过闸门时基选择开关选择,选择T大一些,测量准确度就高一些,T小一些,则测量准确度就低.根据被测频率选择闸门时间来控制量程.在整个电路中,时基电路是关键,闸门信号脉冲宽度是否精确直接决定了测量结果是否精确.逻辑控制电路的作用有两个:一是产生锁存脉冲Ⅳ,使显示器上的数字稳定;二是产生清“0”脉冲Ⅴ,使计数器每次测量从零开始计数。

单片机频率计原理

单片机频率计原理单片机频率计是一种利用单片机进行频率测量的设备。

其原理是通过测量输入信号的周期或频率来计算频率值。

单片机频率计的原理可以简单分为两个主要步骤:信号捕获和频率计算。

首先,信号捕获阶段,单片机需要从外部接收输入信号。

通常情况下,输入信号会经过一个条件放大器,然后进入单片机的输入引脚。

为了确保精确度,输入信号通常需要经过一个低通滤波器,以去除高频噪声。

一旦输入信号进入单片机,接下来就是频率计算阶段。

单片机通过计算输入信号的周期或频率,得出频率值。

常见的计算方法有两种:使用计数器和使用定时器。

使用计数器的方法是通过使用单片机的计数器来测量输入信号的周期或频率。

计数器接收到输入信号后开始计数,直到计数值达到某个预设值或经过一个特定时间长度。

然后,计数器的值将被读取并转换为频率值。

由于计数器的位数有限,所以测量范围也是有限的。

使用定时器的方法是利用单片机的定时器来测量输入信号的周期或频率。

定时器会根据输入信号的上升沿或下降沿来开始和停止计时。

通过测量定时器的值,可以计算出输入信号的周期或频率。

相比于计数器方法,定时器方法相对更精确,也更适合测量高频信号。

无论是计数器方法还是定时器方法,最终都需要将计数器或定时器的值进行一系列的转换以得到最终的频率值。

转换方式可以通过公式计算,也可以通过查表的方式来获得。

在转换过程中,需要考虑到单片机的时钟频率和计数器或定时器的分辨率等因素,以确保测量结果的准确性。

此外,为了提高测量的稳定性和准确性,单片机频率计通常还会采用一些增强技术。

例如,可以使用外部参考时钟来优化计时精度。

还可以进行信号预处理,如去除噪声和滤波等,以提高测量信号的质量。

总结起来,单片机频率计通过测量输入信号的周期或频率来计算频率值。

其中,信号捕获阶段主要是对输入信号进行处理,而频率计算阶段则是通过计数器或定时器来测量信号的周期或频率,并将其转换为最终的频率值。

通过合理的设计和优化,单片机频率计可以实现准确、稳定和高精度的频率测量功能。

频率计的基本原理及应用

频率计的基本原理及应用频率计是一种可以测量并显示信号频率的仪器,广泛应用于各种行业中。

它的基本原理是通过对信号进行计数和计时并在计算机内进行处理,从而得出信号的频率。

频率计的工作原理频率计的工作原理分为两个方面:一个是信号的计数,另一个是对计时的处理。

在信号计数部分,频率计将输入信号转换为方波,然后将方波输入到一个计数器中,计数器对方波的每一周期进行计数,从而得到信号的频率。

在计时的处理部分,频率计将每个周期的时间戳存储在寄存器中,并按照一定的算法对时间戳进行处理,从而得出信号的频率。

频率计的精度和稳定性与计时部分的精度和稳定性有关。

一般情况下,计时部分采用定时器或计数器,计时精度达到微秒级别。

频率计的基本应用频率计广泛用于各种行业中,在电子、通信、机械、化工等领域都有重要的应用。

下面分别介绍一些主要的应用。

在电子领域中的应用频率计在电子领域中主要应用于信号测试、信号分析和频率合成中。

例如,测试电子设备的工作频率、分析信号的频谱分布、合成一定频率的信号等。

在通信领域中的应用频率计在通信领域中主要应用于信号收发和频率的稳定性测试。

例如,测试无线电设备的工作频率、测量电话信号的频率、测试卫星信号的频率等。

在机械领域中的应用频率计在机械领域中主要用于转速的测量和控制。

例如,测试轴承的转速、测试风扇的转速、测试电机的转速等。

在化工领域中的应用频率计在化工领域中主要用于流量的测量和控制。

例如,测试流量计的频率输出、控制泵的流量、测试管道内网站的流量等。

频率计的优缺点频率计的优点很明显,首先,它的精度高、稳定性好,可以满足各种场合的测量需求;其次,频率计采用数字技术,易于自动化和集成,提高了工作的效率和可靠性。

然而,频率计的缺点也十分明显,它的测量范围和最大测量频率有限,一般在数百兆赫兹以内,无法测量高频和微弱信号;此外,频率计受到环境温度和电源噪声等因素的影响,影响其稳定性和准确性。

结语总体来说,频率计是一种非常重要的测量仪器,在各种行业中都有重要的应用。

等精度数字频率计

等精度数字频率计测量方式:一、测频原理所谓“频率”,确实是周期性信号在单位时刻转变的次数。

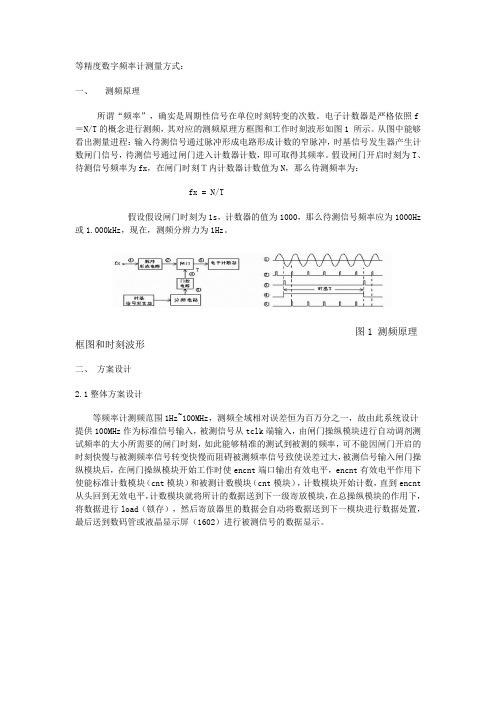

电子计数器是严格依照f =N/T的概念进行测频,其对应的测频原理方框图和工作时刻波形如图1 所示。

从图中能够看出测量进程:输入待测信号通过脉冲形成电路形成计数的窄脉冲,时基信号发生器产生计数闸门信号,待测信号通过闸门进入计数器计数,即可取得其频率。

假设闸门开启时刻为T、待测信号频率为fx,在闸门时刻T内计数器计数值为N,那么待测频率为:fx = N/T假设假设闸门时刻为1s,计数器的值为1000,那么待测信号频率应为1000Hz 或1.000kHz,现在,测频分辨力为1Hz。

图1 测频原理框图和时刻波形二、方案设计2.1整体方案设计等频率计测频范围1Hz~100MHz,测频全域相对误差恒为百万分之一,故由此系统设计提供100MHz作为标准信号输入,被测信号从tclk端输入,由闸门操纵模块进行自动调剂测试频率的大小所需要的闸门时刻,如此能够精准的测试到被测的频率,可不能因闸门开启的时刻快慢与被测频率信号转变快慢而阻碍被测频率信号致使误差过大,被测信号输入闸门操纵模块后,在闸门操纵模块开始工作时使encnt端口输出有效电平,encnt有效电平作用下使能标准计数模块(cnt模块)和被测计数模块(cnt模块),计数模块开始计数,直到encnt 从头回到无效电平,计数模块就将所计的数据送到下一级寄放模块,在总操纵模块的作用下,将数据进行load(锁存),然后寄放器里的数据会自动将数据送到下一模块进行数据处置,最后送到数码管或液晶显示屏(1602)进行被测信号的数据显示。

PIN_84VCCreset INPUTPIN_31VCCtclk INPUTcnt_time 100Signed IntegerParameter Value Typeclken_1kHztclkclrloadencntcnt_eninst4cnt_w idth32Signed IntegerParameter Value Typeclkclrencntout[cnt_width-1..0]cntinst1cnt_w idth32Signed IntegerParameter Value Typeclkclrencntout[cnt_width-1..0]cntinst2cnt_w idth32Signed IntegerParameter Value Typeclken_1kHzclrlock_endata[cnt_width-1..0]regout[cnt_width-1..0]bcnt_reginst3cnt_w idth32Signed IntegerParameter Value Typeclken_1kHzclrlock_endata[cnt_width-1..0]regout[cnt_width-1..0]tcnt_reginst5clken_1kHzresetenencntclr_cntlockclr_regload_encntcontrolinst6clken_1kHzresetclearreset_cntinst16被测频率信号输入闸门信号控制器100M标准频率信号计数器被测频率信号计数器100M标准频率数据寄存被测信号频率数据寄存复位模块闸门、计数、寄存的总控制模块clk_100MHztclk1loadclk_100MHzen_1kHzclk_100MHzen_1kHzen_1kHzclk_100MHzloaden_1kHzclk_100MHzclk_100MHzen_1kHzset_f ashion[4]tclk1reset1cnt_numb[31..0]cnt_numt[31..0]两路数据送到下一级进行数据处理2.2理论分析采纳等精度测量法,其测量原理时序如图1所示从图1中能够取得闸门时刻不是固定的值,而是被测信号的整周期的倍数,即与被测信号同步,因此,不存在对被测信号计数的±1 误差,可取得:变形后可得:对上式进行微分,可得:由于 dn=± 1 ,因此可推出:从式(5)能够看出:测量误差与被测信号频率无关,从而实现了被测频带的等精度测量;增大T或提高fs能够提高测量精度;标准频率误差为dfs/fs,因为晶体的稳固度很高,再加上FPGA核心芯片里集成有PLL锁相环可对频率进一步的稳固,标准频率的误差能够进行校准,校准后的标准误差即能够忽略。

数字频率计用测频法测量的方法

数字频率计用测频法测量的方法

数字频率计是一种常见的测量设备,通常用于测量信号的频率。

测频法是一种常用的测量频率的方法,它可以通过测量信号的周期来确定信号的频率。

数字频率计通常使用测频法来测量信号的频率。

具体来说,数字频率计可以通过以下步骤来测量信号的频率:

1. 将信号输入到数字频率计中,数字频率计会对其进行处理,并显示信号的频率。

2. 测量信号的周期,数字频率计可以通过测量信号的持续时间来确定信号的周期。

3. 根据信号的周期,可以计算出信号的频率。

数字频率计使用测频法来测量信号的频率,具有准确、快速、方便等特点,适用于许多不同的应用场景。

拓展:

测频法是一种测量频率的方法,它可以通过测量信号的周期来确定信号的频率。

具体来说,测频法可以通过以下步骤来测量信号的频率:

1. 将信号输入到测频法仪器中,仪器会对其进行处理,并显示信号的频率。

2. 测量信号的周期,测频法仪器可以通过测量信号的持续时间来确定信号的周期。

3. 根据信号的周期,可以计算出信号的频率。

测频法仪器通常用于测量信号的频率,特别是在电子学、通信学等领域。

基于51单片机的方波频率计

基于51单片机的简易方波频率计1.测频原理:在单位时间内对被测信号进行计数。

2.可扩展性:(1)放大整形模块:放大电路是对待测信号的放大,降低对待测信号幅度的要求。

整形电路是对一些不是方波的待测信号转化成方波信号,便于测量。

添加了放大整形模块后可测更多波形对象。

(2)分频模块:考虑单片机外部计数,使用12 MHz时钟时,最大计数速率为500 kHz(理论值,实测为490kHz左右),因此需要外部分频。

分频电路用于扩展单片机频率测量范围,并实现单片机频率测量使用统一信号,可使单片机测频更易于实现,而且也降低了系统的测频误差。

(3)电源模块:为整个系统提供合适又稳定的电源,主要为单片机、信号调理电路以及分频电路提供电源,电压要求稳定、噪声小及性价高的电源。

(4)其他:显示部分程序可自行设计,达到通过按键开关功能,按键自行选档(显示单位)功能等。

3.软件系统:(1)编写环境:keil (u4)(2)烧写程序:STC-ISP (v6.85H)-- STC89C52RC/LE52RC(型号选择)(3)软件代码:---------------------------------------------------------------------------------------------------------------------------------#include<reg52.h>#define uint unsigned int#define uchar unsigned charsbit wr=P3^6; //数码管段选sbit lcdrs=P2^5; //数据/命令选择端sbit lcdrw=P2^6; //读写选择端sbit lcden=P2^7; //使能信号Euchar code table[]="KHz";uchar a[5];uint n=0;uint t=0;unsigned long f;void delay(uint z) //延时函数{uint x,y;for(x=z;x>0;x--)for(y=110;y>0;y--);}void write_com(uchar com) //1602液晶操作写指令函数{lcdrs=0;lcdrw=0;P0=com;delay(5);lcden=1;delay(5);lcden=0;}void write_data(uchar date) //1602液晶操作写数据函数{lcdrs=1;lcdrw=0;P0=date;delay(5);lcden=1;delay(5);lcden=0;}void init() //液晶显示初始化函数{wr=0; //关数码管段选lcden=0;write_com(0x38); //选择16×2屏幕显示write_com(0x0c); //开显示总开关光标不显示write_com(0x06); //光标右移屏幕所有文字不整体右移 write_com(0x01); //清屏write_com(0x80+0x01); //指针选择01位置}void display() //显示函数{uint i;init(); //调用初始化函数a[4]=f/10%10; //获取需要显示的各位数字a[3]=f/100%10;a[2]=f/1000%10;a[1]=f/10000%10;a[0]=f/100000;for(i=0;i<5;i++){write_data(a[i]+'0'); //写入各位数字if(i==2)write_data('.'); //写入小数点'.'}for(i=0;i<3;i++)write_data(table[i]); //逐位写入显示单位KHz}void main() //主函数{TMOD=0x51; //设置工作方式为T0计时,T1计数 TR0=0;TR1=0;TH0=(65536-50000)/256; //T0计时为溢出一次50msTL0=(65536-50000)%256;TH1=0; //T1从零开始计数TL1=0;EA=1; //开总中断ET0=1; //开T0中断ET1=1; //开T1中断TR0=1; //启动T0、T1TR1=1;write_com(0x01); //清屏while(1);}void T_0() interrupt 1 //T0计时中断服务程序{TH0=(65536-50000)/256; //计时初值重装TL0=(65536-50000)%256;t++; //计出50ms次数增长if(t==20) //计时50×20=1000(ms)=1(s){TR1=0; //关闭T0、T1TR0=0;f=n*65536+TH1*256+TL1; //算计此时频率fdisplay(); //调用显示函数t=0; //50ms次数置0n=0; //方波发生负跳变次数置0TH0=(65536-50000)/256; //T0、T1初值重装TL0=(65536-50000)%256;TH1=0;TL1=0;TR0=1; //再次启动T0、T1 以达实时更新效果TR1=1;}}void T_1() interrupt 3 //T1计数中断服务程序{TH1=0;TL1=0;n++; //计数溢出次数增长}---------------------------------------------------------------------------------------------------------------------------------4.系统实测:(1)实测环境:a.芯片:AT89C52b.方波信号输入:函数发生器选择CH1(信道1)Square(方波),CH1接口分别连接51开发板地端(GND)、AT89C51之14脚(T0外部输入端)。

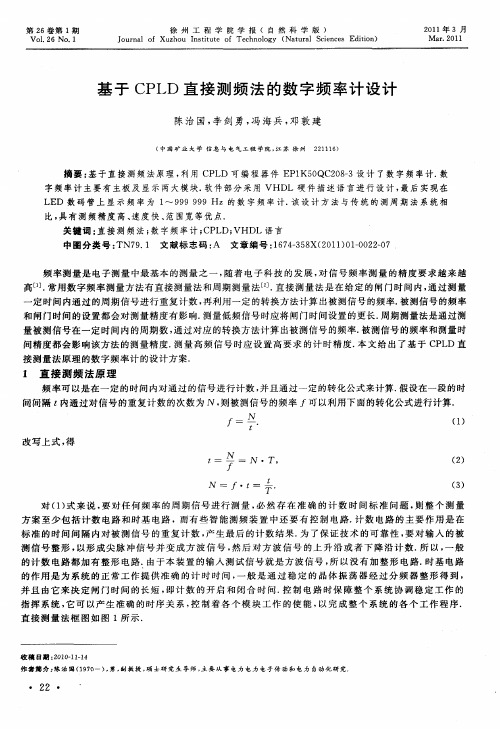

基于CPLD直接测频法的数字频率计设计

图( 3. 图 ) 此测 量模 块 的测量 位数 为 6 , 位 若想 改变频 率计 的测量位 数 , 可适 当 的改变 计数 器 的个数 , 则 并且 相 应模 块更 改相应 的参 数 , 如此就 可 以增 加或 者减 少频率计 的测量 范 围. 其顶层 电路仿 真 图见 图 4 .

器、 测频 控 制 信 号 发 生器 、 带有 时钟 使 能 端 的 计数 器 、 锁存 器 D G、 码 器 EN ODE 串联 动 态 扫描 模 块 RE 译 C 、

D MI 以及 6个 L D 显示 管组 成. 4 TS AO E 用 OMHz 的有 源 晶振作 为 F GA 的测 试标 准 频率 , P 经分 频 电 路最

过 计 算 在 一 定 时 间 内通 过 的 周 期 数 . 就 要 求 该模 块 的 能 产 生 一 个 周 期 为 1s的 技 术 使 能 信 号 E 这 NA,

并 且 还 要 同 步 对 每 一 个 计 数 器 的 使 能 端 进 行 控 制 . 数 器 在 使 能 端 为 高 电平 时 开 始 计 数 , 低 电 平 时 计 在 停 止 计 数 , 且 还要 保 持 计 数值 . 此 期 间 , 存 器 的 使 能 端 接 收 到 一 个 锁 存 的 上 升 信 号 , 且 将 计 数 并 在 锁 并 值 送 到 锁存 器 中 , 过 译 码 电路 译 码 再 经 显示 模 块 最 终 在 七 段 数 码 管 上 显 示 计 数 结 果 . 过 锁 存 器来 通 通

终得 到 1Hz 频率 . 信 号作 为 测频 控制 信 号发 生器 的输 入信 号 , 到 1s的 闸 门信号 用 来 控制 计 数 器计 1Hz 得

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书学生姓名:王耀辉专业班级:通信1304指导教师:陈适工作单位:信息工程学院题目: 采用测频原理的数字频率计初始条件:VHDL硬件描述语言,ISE Design Suite开发环境,Modelsim SE仿真环境要求完成的主要任务:1.采用测频法,设计一个4位十进制数字显示的数字频率计2.其测量的范围为1~9999KHz课程设计进度安排序阶段内容所需时间号1 方案设计1天2 软件设计2天3 系统调试1天4 撰写报告1天合计5天指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要----------------------------------------------------------------------- I Abstract --------------------------------------------------------------------- 21. FPGA、VHDL及ISE概述 ------------------------------------------------ 31.1 FPGA简介------------------------------------------------------- 31.2 VHDL 概述------------------------------------------------------- 31.3ISE --------------------------------------------------------------- 52频率测量原理及方案 ---------------------------------------------------- 62.1设计要求--------------------------------------------------------- 62.2 频率测量方法 ---------------------------------------------------- 62.2.1时间门限测量法 ------------------------------------------------- 62.2.2标准频率比较测量法 --------------------------------------------- 62.2.3 等精度测量法--------------------------------------------------- 7 2.3方案提出及确定----------------------------------------------------------- 72.4系统设计--------------------------------------------------------- 82.5 系统组成 -------------------------------------------------------- 92.6小结------------------------------------------------------------ 103数字频率计VHDL程序与仿真 ------------------------------------------- 113.1模块图---------------------------------------------------------- 113.1.1顶层模块图 ------------------------------------------------- 113.1.2顶层模块图 ------------------------------------------------- 113.2程序设计-------------------------------------------------------- 134 仿真测试------------------------------------------------------------- 174.1调试和器件编程-------------------------------------------------- 174.2频率计仿真结果------------------------------------------------------ 195 心得体会------------------------------------------------------------- 226 参考文献------------------------------------------------------------- 22摘要数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着现场可编程门阵列FPGA 的广泛应用,运用VHDL等硬件描述语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

采用FPGA现场可编程门阵列为控制核心,通过硬件描述语言VHDL编程,在QuartusII 仿真平台上编译、仿真、调试,并下载到FPGA芯片上,通过严格的测试后,能够较准确地测量方波、正弦波、三角波、矩齿波等各种常用的信号的频率,而且还能对其他多种物理量进行测量本文介绍了如何采用测频法,利用FPGA现场可编程门阵列为控制核心,通过VHDL 语言编程,在ISE仿真平台上仿真平台上编译、仿真、调试,设计一个4位十进制数字显示的数字频率计以此来巩固课堂理论学习,并能用所学理论知识正确分析硬件设计基本问题和解释数字电路的基本现象。

关键字:FPGA,数字电路,测频法,数字频率计AbstractDigital frequency meter is a digital circuit in a typical application, the actual hardware design of devices used in more complicated connection, but will have relatively large delay, caused by measurement error, poor reliability. With the FPGA field programmable gate array a wide range of applications to the development as a means of using the VHDL hardware description language such as language, will greatly simplify the whole system to improve overall system performance and reliability.Digital frequency meter is made by using a digital circuit system can achieve the cyclical changes in signal frequency measuring instruments. Frequency meter is mainly used for measuring frequency sine wave, square wave, triangle wave and spikes and other periodic signal. Its extended functionality can measure cycle and pulse width of the signal.This article describes how to use the frequency measurement method, usingof field programmable gate array FPGA for the control of the core and VHDL language programming, simulation in QuartusII development environment, the design of a four decimal digits displayed digital frequency meter in order to reinforce classroom learning theory and the theory of knowledge can be used to correctly analyze hardware the design and interpretation of the basic problems of the basic phenomena of digital circuits.Keywords: FPGA, Digital circuits, Frequency measurement method, Digital frequency meter1. FPGA、VHDL及ISE概述本章首先对设计所采用的可编程逻辑器件FPGA及VHDL以及仿真软件ISE进行简单的介绍,对设计有些基本的了解。

1.1 FPGA简介FPGA是20世纪80年代中期出现的高密度可编程逻辑器件,它一般由布线资源分隔的可编程逻辑单元构成阵列,又由可编程I/O单元围绕阵列构成整个芯片,排列阵列的饿逻辑单元由布线通道中的可编程内连线连接起来实现一定的逻辑功能。

一个FPGA包含丰富的具有快速系统速度的逻辑门、寄存器和I/O组成。

FPGA/CPLD芯片都是特殊的ASIC芯片,除了具有ASIC的特点外还有一下几个优点:随着超大规模集成电路VLSI工艺的不断提高,单一芯片内部可以容纳上百万个晶体管;FPGA/CPLD芯片出厂前100%都做过测试,不需要设计人员承担风险和费用;用户可以反复地编程、擦除、使用或者在外围电路不动的的情况下,用不同软件就可实现不同的功能,用FPGA/CPLD试制样片,能以最快的速度占领市场。

FPGA/CPLD软件包中有各种输入工具、仿真工具、版图设计及编程器等全线产品,使电路设计人员在较短的时间内就可以完成电路的输入、编译、优化、仿真,直至最后芯片的制作。

1.2 VHDL 概述VHDL语言是一种用于电路设计的高级语言。

它在80年代的后期出现。