PIC单片机等精度测量频率法

等精度频率计

end shuchu;

architecture a of shuchu is

begin

process (data1,data2,data3,data4,data5,data6,data7,data8,data9,data10)

signal c: std_logic;

begin

process (clk,nr)

begin

if nr = '1' then

f<=0;c<='0';

elsif (clk'event and clk = '1')then

if f<9999 then

f<=f+1;

else

f<=0;

c<= not c;

end if;

关键字:

频率、周期、标准时钟、乘除运算、分频、十进制显示、锁存

方案比较:

(1)用单片机实现:

等精度数字频率计涉及到的计算包括加,减,乘,除,耗用的资源比较大,用一般中小规模CPLD/FPGA芯片难以实现。因此,我们选择单片机和CPLD/FPGA的结合来实现。电路系统原理框图如图所示,其中单片机完成整个测量电路的测试控制,数据处理和显示输出;CPLD/FPGA完成各种测试功能;键盘信号由AT89C51单片机进行处理,它从CPLD/FPGA读回计数数据并进行运算,向显示电路输出测量结果;显示器电路采用七段LED动态显示,由8个芯片74LS164分别驱动数码管。

为了节省资源改进了除法器进制转化模块,说明如下:

被除数

序号

10进制

PIC单片机等精度测量频率法

PIC单片机等精度测量频率法单片机测量频率,是一个比较常见但又不好解决的问题。

主要是测量频率是高端和低端不能兼顾的问题。

测量频率无非两种方法:1.在一段固定的时间及脉冲的个数,然后除时间得到频率。

2.测量脉宽计算频率。

第一种方法,适合测频率在1KHz以上的脉冲信号。

因为要保证测量精度在0.1%,至少要保证脉冲个数在1000个,假设测10HZ左右的信号,则一个测试周期需要100秒,这显然不是我们所能接受的。

第二种方法,适合测频率小于1KHz的信号。

因为要保证测量精度在0.1%,在一个脉冲宽度(1ms)内,作为时标的定时器至少要走1000个数(此时PIC 的晶振理论上至少也要4MHz)。

事实上,想利用上述两种方法精确测量宽范围的频率,几乎是不可能的。

PIC系列特有的平级中断,也使其测量频率比51系列测量困难。

等精度数字测频基本框图等精度数字测频基本框图如下fx图中的闸门G1、G2分别用来控制输入信号周期计数和闸门时间宽度计时。

其中,G1与输入信号同步,这样可使计数器N1的量化误差dN1=0。

计数器N2对标准时标信号Tc进行计数,并以此来测量实际的闸门宽度Tg,则输入信号的频率可表示为:fx=N1/Tg=N1/(Tc*N2)标准时标信号采用单片机自身的工作时钟,可看作常数。

因此fx的相对误差为:dfx/fx=dN1/N1-dN2/N2=-dN2/N2式中,dN2为计数器N2产生的量化误差,最大为±1个Tc,在实际设计中,选择适当的时标Tc和闸门宽度Tg可是N2始终足够大,以次在fx的全频段范围内得到足够高的精度。

等精度测量法的实质就是一种变相的测脉宽法。

在实际使用时(PIC为例),可将Timer0作计数器N1,Timer1作计数器N2,外部中断INT0同T0连在一起,作为Tg信号,如图:fx T0INT0PIC首先打开INT中断,允许Timer0计数,当一个fx的上升沿来临时,触发INT中断。

第八讲 等精度测频

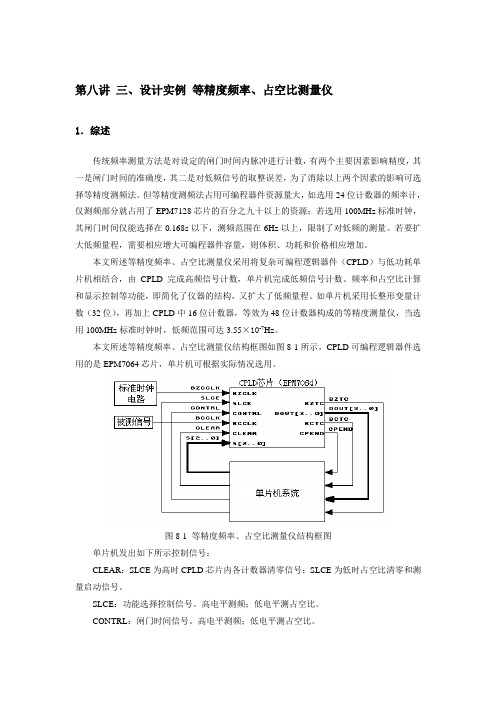

第八讲三、设计实例等精度频率、占空比测量仪1.综述传统频率测量方法是对设定的闸门时间内脉冲进行计数,有两个主要因素影响精度,其一是闸门时间的准确度,其二是对低频信号的取整误差,为了消除以上两个因素的影响可选择等精度测频法。

但等精度测频法占用可编程器件资源量大,如选用24位计数器的频率计,仅测频部分就占用了EPM7128芯片的百分之九十以上的资源;若选用100MHz标准时钟,其闸门时间仅能选择在0.168s以下,测频范围在6Hz以上,限制了对低频的测量。

若要扩大低频量程,需要相应增大可编程器件容量,则体积、功耗和价格相应增加。

本文所述等精度频率、占空比测量仪采用将复杂可编程逻辑器件(CPLD)与低功耗单片机相结合,由CPLD完成高频信号计数,单片机完成低频信号计数、频率和占空比计算和显示控制等功能,即简化了仪器的结构,又扩大了低频量程。

如单片机采用长整形变量计数(32位),再加上CPLD中16位计数器,等效为48位计数器构成的等精度测量仪,当选用100MHz标准时钟时,低频范围可达3.55×10-7Hz。

本文所述等精度频率、占空比测量仪结构框图如图8-1所示,CPLD可编程逻辑器件选用的是EPM7064芯片,单片机可根据实际情况选用。

图8-1 等精度频率、占空比测量仪结构框图单片机发出如下所示控制信号:CLEAR:SLCE为高时CPLD芯片内各计数器清零信号;SLCE为低时占空比清零和测量启动信号。

SLCE:功能选择控制信号。

高电平测频;低电平测占空比。

CONTRL:闸门时间信号。

高电平测频;低电平测占空比。

S[2..0]:输出选择控制信号。

000—CPLD 输出标准时钟信号四位计数值最低位;001—CPLD 输出标准时钟信号计数值次低位;010—CPLD 输出标准时钟信号计数值第三位;011—CPLD 输出标准时钟信号计数值第四位;100—CPLD 输出被测信号四位计数值最低位;101—CPLD 输出被测信号计数值次低位;110—CPLD 输出被测信号计数值第三位;111—CPLD 输出被测信号计数值第四位。

基于单片机的等精度测频法及其应用研究

基于单片机的等精度测频法及其应用研究一、研究背景在许多电子测量中,频率是一个基本参数。

然而,频率测量是非常复杂的,特别是对于高频率和低频率的测量。

精确的频率测量对于各种电子设备的研究和制造都非常重要。

传统测频法中常用的是时间差测量法和计数测量法,这两种方法都具有测量精度不够高及难于自动化等缺点。

因此,需要研究一种更高精度的测频方法,这就是等精度测频法。

二、等精度测频法的基本原理等精度测频法是一种基于数字信号处理技术的测频方法。

该方法基于两个相邻的周期振荡信号之间的相位差求得信号的频率。

其基本原理如下:在相邻的周期T1和T2之间,通过计算第一个周期的信号与第二个周期信号之间的相位差$\\Delta\\phi$,反推出第二个周期信号的频率f:$$ f = \\frac{1}{2\\pi}\\cdot\\frac{\\Delta\\phi}{T_2-T_1} $$由上式可知,等精度测频法只需要获取两个相邻周期信号的相位差和两个周期的时间,即可求出信号的频率,测量精度较高。

三、等精度测频法的软件实现等精度测频法的实现需要用到数字信号处理技术,可以通过单片机结合C语言软件实现。

主要步骤如下:1.信号采样将需要测量的信号经过高精度的AD采集电路进行采样,将信号转换成对应的数字信号。

2.相位差计算通过数字信号处理技术,计算出相邻周期信号之间的相位差。

3.频率计算根据相邻周期信号的相位差和两个周期的时间,计算出信号的频率。

4.结果输出将计算出的结果输出到数码显示管等输出模块中,实现信号的频率测量功能。

四、等精度测频法的应用等精度测频法在电子设备制造、通信领域、科研实验等方面都具有重要应用价值。

例如:1.信号频率稳定性测试将需要测试的信号经过等精度测频法测量其频率稳定性,可用于评估设备的性能。

2.信号调制解调信号的调制解调中需要精确测量信号的频率,等精度测频法可以实现这一功能。

3.相位锁定在数字信号处理中,需要实现相位锁定功能来避免信号相位偏差造成的误差。

基于单片机的等精度数字测频装置的原理及实现

其中 Ä®’ 为计数器 ®’ 产生的量化误差 Œ最大为 ? ‘ 个 ´Ã "在实际设计中 Œ选择适当的时标周期 ´Ã 和 闸门宽度 ´Ç 可使 ®’ 始终足够大 Œ 并在 ÆØ的全频段 范围内得到足够多的有效位数的显示结果 "

“ 基于单片机的等精度数字测频方案

- £³ • •‘ 系列单片机具有两个 ‘– 位的定时器• 计数器 ´‘ 和 ´• Œ它们可分别代替图 ’ 中的计数器 ®‘ 和 ®’ › 单片机的外部中断功能可方便地实现闸门开 关与被测信号的跳变沿同步 › 利用单片机的数据运 算能力可编制相应的乘除法程序 Œ 并实现测量结果 的等精度显示 "

基于单片机的等精度数字测频

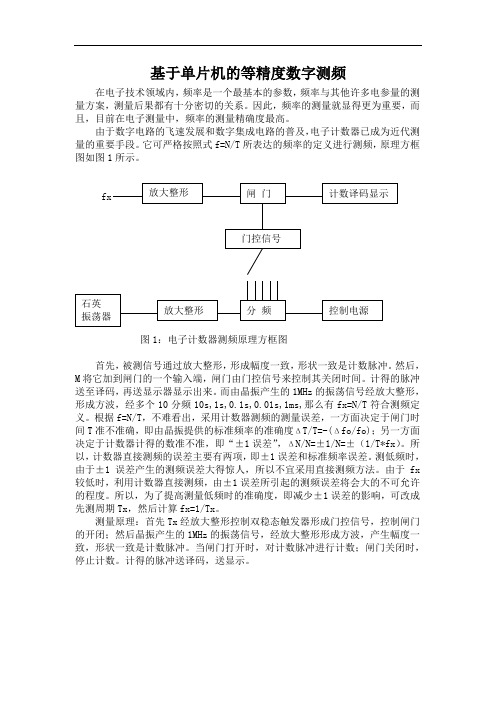

基于单片机的等精度数字测频在电子技术领域内,频率是一个最基本的参数,频率与其他许多电参量的测量方案,测量后果都有十分密切的关系。

因此,频率的测量就显得更为重要,而且,目前在电子测量中,频率的测量精确度最高。

由于数字电路的飞速发展和数字集成电路的普及,电子计数器已成为近代测量的重要手段。

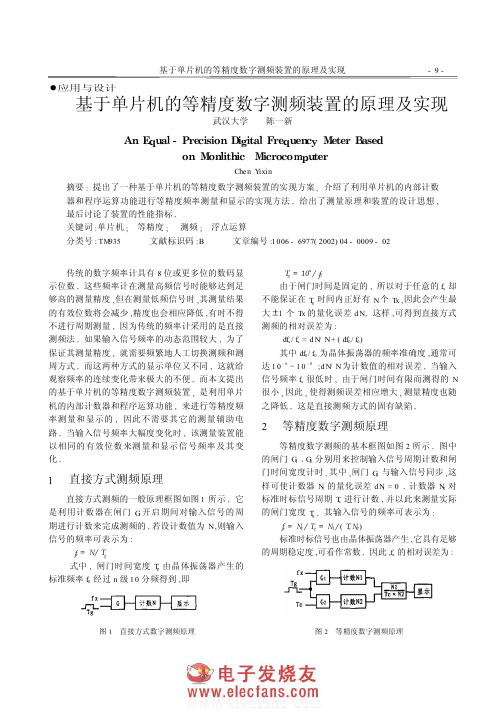

它可严格按照式f=N/T所表达的频率的定义进行测频,原理方框图如图1所示。

图1:电子计数器测频原理方框图首先,被测信号通过放大整形,形成幅度一致,形状一致是计数脉冲。

然后,M将它加到闸门的一个输入端,闸门由门控信号来控制其关闭时间。

计得的脉冲送至译码,再送显示器显示出来。

而由晶振产生的1MHz的振荡信号经放大整形,形成方波,经多个10分频10s,1s,0.1s,0.01s,1ms,那么有fx=N/T符合测频定义。

根据f=N/T,不难看出,采用计数器测频的测量误差,一方面决定于闸门时间T准不准确,即由晶振提供的标准频率的准确度ΔT/T=-(Δfo/fo);另一方面决定于计数器计得的数准不准,即“±1误差”,ΔN/N=±1/N=±(1/T*fx)。

所以,计数器直接测频的误差主要有两项,即±1误差和标准频率误差。

测低频时,由于±1误差产生的测频误差大得惊人,所以不宜采用直接测频方法。

由于fx 较低时,利用计数器直接测频,由±1误差所引起的测频误差将会大的不可允许的程度。

所以,为了提高测量低频时的准确度,即减少±1误差的影响,可改成先测周期Tx,然后计算fx=1/Tx。

测量原理:首先Tx经放大整形控制双稳态触发器形成门控信号,控制闸门的开闭;然后晶振产生的1MHz的振荡信号,经放大整形形成方波,产生幅度一致,形状一致是计数脉冲。

当闸门打开时,对计数脉冲进行计数;闸门关闭时,停止计数。

计得的脉冲送译码,送显示。

图2:电子计数器测周期原理图8XX51单片机的定时器T1由TH1,TL1组成,定时器T0由TH0,TL0组成。

51单片机测量频率的方法

51单片机测量频率的方法2012-12-10 11:1151单片机的测量频率方法有很多,这里谈的是,将被测量信号经过整形后转换成方波信号,利用单片机查询两个上升沿,在此期间根据晶体振荡器产生的周期为 Tc的脉冲送计数器进行计数,设计数值为N,则得被测量信号的周期值Tx=Tc×N,然后取其倒数即为被测量信号的频率。

当然如果利用单片机的捕捉功能,实现起来可能程序更加简练。

下面频率测量计数波形示意图程序代码如下/*-------------------------------------测量周期法的基本原理:在被测信号T内,对某一基准时间进行计数,基准时间与计数值的乘积便是被测周期. ---------------------------------------*/#include"at89x51.h"#define uint unsigned intuint count, period;bit rflag = 0; //设置周期标志void control(void){TMOD = 0x09; //T/C0为方式1,INT0 为1是启动定时器IT0 = 1; //脉冲方式(后沿负跳有效)进入中断TH0 = 0;TL0 = 0;P1_0 = 0; P1_0 = 1; //触发器清零TR0 = 1; //启动T/C0EX0 = 1; //只开外部中断1EA = 1; //开总中断}void INT_0(void) interrupt 0 using 1 //INTO中断服务{EA = 0;TR0 = 0;count = TL0 + TH0 * 256;//取计数值rflag = 1; //设标志EA = 1;}main(){control();while(rflag == 0); 、//等待一个周期period = count * 2; //fosc = 6MHz,2us计数增1,周期值单位us }。

等精度测频 (2)

毕业设计(论文)摘要频率是电子技术领域内的一个基本参数,同时也是一个非常重要的参数。

稳定的时钟在高性能电子系统中有着举足轻重的作用,直接决定系统性能的优劣。

随着电子技术的发展,测频系统使用时钟的提高,测频技术有了相当大的发展,但不管是何种测频方法,士1个计数误差始终是限制测频精度进一步提高的一个重要因素。

本设计采用等精度频率设计原理和8051软核做微处理器。

通过分析士1个计数误差的来源得出了一种新的测频方法:检测被测信号,时基信号的相位,当相位同步时开始计数,相位再次同步时停止计数,通过相位同步来消除计数误差,然后再通过运算得到实际频率的大小。

充分利用8051软核简化外围电路及降低系统设计的复杂度。

采用VHDL语言,成功的编写出了设计程序,并在Qutus II软件环境中,对编写的VHDL程序进行了仿真,得到了很好的效果。

最,给出了较详细的设计方法和完整的程序设计以及调试结果。

关键词:EDA、FPGA、全同步、数字频率计、VHDL语言、8051ABSTRACTFrequency is a basic parameter of elcetornics field,meanwhile,it’saver important Param ete.Stable clock is very important in high electronics syetem.determining the syetem perfermance directly.With the development of technology of electronics,the frequency measurement System using higher clock,the frequency measurement technology has very nice development .In despite of using all other advanced ftequency measurement methods,the Positive and negativel errors was a very important factor that stop frequency measurement precision improving all through. This design uses the design principle and the frequency of such precision 8051 soft nuclear do microprocessors.Through analyzing the origin of the Positive and negative got a new frequency measurement methods: checkingt measured and standard signal’s Phase,if the Phase is synchronous.then the counters start counting when the signal’s Phase is synchronous again. The counters to stopping working by Phase in一Phase to eliminate counting erors,then getting the real frequency through calculating. Make full use of the 8051 soft IP simplified peripheral circuit and reduce the complexity of the system design. the design of complete digital cymometer was successful using VHDL language, successful writing out design program, and in Qutus II software environment ,and procedures obtained good effect. The detail is presented, the design method and program design and commissioning of full results.Keywords:EDA、FPGA、、Complete ln-phase、DigtaICymomcter、VHDL、8051目录摘要..................................................................................................................................... I I ABSTRACT . (III)绪论 (1)第一章系统分析与方案论证 (3)第二章微处理器的简介 (5)2.1 FPGA简介 (5)2.1.1 FPGA的工作原理 (5)2.1.2 FPGA配置模式 (6)2.2 8051单片机IP软核应用系统构建 (7)2.2.1 8051单片机IP软核应用系统构建 (7)2.2.2 K8051单片机软核基本功能和结构 (7)第三章频率计的工作原理 (11)3.1 测频原理介绍 (11)3.2 测周原理 (13)第四章系统硬件的设计与实现 (14)4.1 系统的整体框图 (14)4.2 K8051单片机软核实用系统构建和软件测试 (14)4.3 测频模块的设计及调试 (15)第五章系统软件设计 (22)5.1 系统软件总体设计 (22)5.2 测频及测周程序设计 (22)5.3 显示程序设计 (24)第六章系统整体调试 (25)结束语 (26)致谢 (27)参考文献 (28)附录 (29)附件1.总体硬件图 (29)附件2 单片机控制程序 (30)绪 论随着 数 字 电路应用越来越广泛,传统的通用数字集成电路芯片已经很难满足系统功能的要求,而且随着系统复杂程度的不断增加,所需通用集成电路的数量呈爆炸性增长,使得电路板的体积迅速膨胀,系统可靠性难以保证。

利用PIC单片机CCP模块设计简易数字频率计的C语言程序

第 10章 利用 CCP 模块设计频率计#include <math.h>table[11]={0xc0 ,0xf9,0xa4,0xb0,0x99,0x92,0x82,0XD8 ,0x80,0x90,0xFF} ;//不带小数点的显示段码表const char table0[11]={0X40 ,0X79,0X24,0X30,0X19,0X12,0X02,0X78,0X00, 0X1 0 ,0xFF} ;//带小数点的显示段码表10.5 程序设计 10.5.4 #includ e #includ e 程序清单 <pic.h><stdio.h> //本程序利用 CCP1模块实现一个“简易数字频率计”的功能const charint cp1z[11];cp1 y1;unsignedcharcp1e[2];bank3 union {int //定义一个数组,用于存放各次的捕捉值 }cp1u ;unsigned unsigned unsigned char COUNTW ,COUNT ;char COUNTER , data ,k ;char FLAG @ 0XEF ; //定义一个共用体 //测量脉冲个数寄存器#define FLAGIT(adr ,bit) ((unsigned)(&adr)*8+(bit)) //绝对寻址位操作指令 staticbit FLAG1staticbit FLAG2staticbit FLAG3unsignedintdouble@ FLAGIT(FLAG , @ FLAGIT(FLAG , @ FLAGIT(FLAG , char s[4] ; T5 ,uo ; RE5; puad5; 0); 1); 2); //定义一个显示缓冲数组 double//spi 方式显示初始化子程序void SPIINIT(){PIR1=0;SSPCON=0x30;SSPSTAT=0xC0;〃设置SPI 的控制方式,允许SSP 方式,并且时钟下降沿发送,与"74HC595,当其 //SCLk 从低到高跳变时,串行输入寄存器 "的特点相对应TRISC=0xD7 ; //SDO 引脚为输出,SCK 引脚为输出 TRISA5=0; //RA5 引脚设置为输出,以输出显示锁存信号 FLAG1=0 ;FLAG2=0 ;FLAG3=0 ;COUNTER=0X01 ;}//CCP 模块工作于捕捉方式初始化子程序void ccpint( ){CCP1CON=0X05; T1CON=0X00 ; PEIE=1; CCP1IE=1; TRISC2=1; }//系统其它部分初始化子程序//为保证测试精度,测试 5 个脉冲的参数后//求平均值,每个脉冲都要捕捉其上升、下降沿,//故需要有 11 次中断TRISB1=0;TRISB2=0;TRISB4=1;TRISB5=1; RB1=0;RB2=0; }//SPI 传送数据子程序{SSPBUF=data ; do { }while(SSPIF==0) ;//首先设置 CCP1 捕捉每个脉冲的上升沿 //关闭 TMR1 震荡器//外围中断允许 (此时总中断关闭 ) //允许 CCP1 中断//设置 RC2 为输入void initial( ){COUNT=0X0B ; //设置与键盘有关的各口的输入、输出方式 //建立键盘扫描的初始条件void SPILED(data)//启动发送SSPIF=0;} //显示子程序,显示 4 位数 void display( ){RA5=0 ; //准备锁存for(COUNTW=0 ;COUNTW<4 ; COUNTW++){ data=s[COUNTW] ; data=data&0x0F ;if(COUNTW==k) data=tableO[data]; 〃第二位需要显示小数点 else data=table[data];SPILED(data); }for(COUNTW=0 ; COUNTW<4 ; COUNTW++){ data=0xFF ; SPILED(data); }RA5=1; } //键盘扫描子程序 void keyscan( ) {if((RB4==0)||(RB5==0)) else FLAG1 = 0 ;}//键服务子程序{ PORTB=0XFD ;if(RB5==0) data=0X01;if(RB4==0) data=0X03;PORTB=0XFB ;if(RB5==0) data=0X02;if(RB4==0) data=0X04; PORTB=0X00; if(data==0x01) { COUNTER=COUNTER+1 ; if(COUNTER>4)COUNTER=0x01 ; 〃若COUNTER 超过 4,则又从 1 计起void keyserve()//发送显示段码//连续发送 4个 DARK ,使显示好看一些 //最后给一个锁存信号,代表显示任务完成 FLAG1=1 ;//若有键按下,则建立标志 FLAG1//若无键按下,则清除标志 FLAG1//以上确定是哪个键按下//恢复 PORTB 的值//若按下 S9 键,则 COUNTER 加 1} if(data==0x02) { COUNTER=COUNTER-1 ; //若按下 S11 键,则 COUNTER 减 1 if(C0UNTER<1) COUNTER=0x04 ; 〃若 COUNTER 小于 1, } if(data==0x03) FLAG2=1 ; if(data==0x04) FLAG2=0 ; } //中断服务程序 void interrupt cp1int(void) {CCP1IF=0; cp1u.cp1e[0]=CCPR1L ; cp1u.cp1e[1]=CCPR1H ; cp1z[data]=cp1u.y1;CCP 1CON=CCPICONTOXOI ;data++;COUNT--;} //周期处理子程序//若按下 S10 键,则建立标志 //若按下 S12 键,则清除标志 //清除中断标志 则又循环从 4 计起 FLAG2 FLAG2 //存储 1 次捕捉值 //把 CCP1 模块改变成捕捉相反的脉冲沿 void PERIOD( ){T5=cp1z[1O]-cp1z[O] ;RE5=(double)T5;RE5=RE5/5;}//频率处理子程序 //求得 5 个周期的值 //强制转换成双精度数 〃求得平均周期,单位为卩s void FREQUENCY( ) {PERIOD( );RE5=1OOOOOO/RE5;//先求周期 //周期值求倒数,再乘以 1 000 000,得频率, //单位为 HZ }//脉宽处理子程序void PULSE( ) {int pu ;for(data=0, puad5=0;data<=9;data++) {pu=cp1z[data+1]-cp1z[data];puad5=(double)pu+puad5;data=data+2;}RE5=puad5/5;}//占空比处理子程序//求得5 个脉宽的和值//求得平均脉宽void OCCUPATIONAL( ) {PULSE( );puad5=RE5;PERIOD();RE5=puad5/RE5;} //主程序//先求脉宽//暂存脉宽值//再求周期//求得占空比main( ) {SPIINIT( ) ;while(1) { ccpint();initial() ;if(FLAG2==0) { s[0]=COUNTER ;s[1]=0X0A ;s[2]=0X0A ;s[3]=0X0A ;} display( );keyscan();data=0x00;TMR1H=0 ;TMR1L=0 ;CCP1IF=0;//SPI 方式显示初始化//CCP 模块工作于捕捉方式初始化//系统其它部分初始化//第一个存储COUNTER 的值//后面的LED 将显示"DARK"//调用显示子程序//键盘扫描//存储数组指针赋初值ei( );TMR1ON=1 ;while(1){if(COUNT==0)break ;//定时器1清0//清除CCP1 的中断标志,以免中断一打开就进入//中断//中断允许//定时器1 开//等待中断次数结束//禁止中断//关闭定时器//键盘扫描//若确实有键按下,则调用键服务程序 //如果没有按下确定键,则终止此次循环, //继续进行测量 //如果按下了确定键,则进行下面的数值转换和显示工作 if(COUNTER==0x01) FREQUENCY() ; //COUNTER=1 ,则需要进行频率处理 if(COUNTER==0x02) PERIOD() ;//COUNTER=2 ,则需要进行周期处理 if(C0UNTER==0x03) OCC UP A TIONAL() ; //COUNTER=3,则需要进行占空比处理 if(COUNTER==0x04) PULSE() ;k=5;if(RE5<1){RE5=RE5*1000;k=0x00;if(RE5<10){RE5=RE5*1000;k=0x00; if(RE5<100){RE5=RE5*100;k=0x01 ;if(RE5<1000){RE5=RE5*10;k=0x02;RE5=RE5;uo=(int)RE5;sprintf(s , "%4d" , uo);display(); } di(); TMR1ON=0 ; keyscan(); if(FLAG1==1) keyserve() ; if(FLAG2==0) continue//COUNTER=4 ,则需要进行脉宽处理 } else } else } else } else〃若RE5<10,则乘以1 000,保证小数点的精度 〃若RE5<100,则乘以100,保证小数点的精度 〃若RE5<1000,则乘以10,保证小数点的精度 〃把需要显示的数据转换成 4位ASII 码,且放入数//组 S 中〃若RE5<1,则乘以1 000,保证小数点的精度。

单片机测量信号频率的方法

单片机测量信号频率的方法

1.基于定时器的频率测量方法:

这是最常见的测量信号频率的方法之一、单片机内部的定时器可以作为频率计数器,通过设定定时器的预定数值,开始计数,当计数溢出时,说明已经计满一个周期,从而可以根据溢出的次数计算出信号的频率。

2.基于输入捕获的频率测量方法:

这种方法是通过输入捕获功能来测量信号频率。

单片机的输入捕获功能可以用于捕获外部信号的上升沿或下降沿,并记录下捕获到的时间。

通过连续捕获两个上升沿或下降沿之间的时间差,可以计算出信号的周期,从而获得信号的频率。

3.基于计数器的频率测量方法:

这种方法一般用于高频信号的测量。

通过将信号输入到单片机的一个计数器引脚,设置计数器在一定时间内累加该信号的脉冲数,然后通过计算脉冲数与时间的比值来获得信号的频率。

4.基于软件延时的频率测量方法:

这种方法适用于信号频率较低的情况。

通过在程序中使用软件延时的方式来计算指定时间内信号的脉冲数,并通过脉冲数与时间的比值来计算信号的频率。

需要注意的是,测量信号频率还需要考虑到一些细节问题,例如时钟的精度、测量时间的长度以及测量结果的误差等。

在实际应用中,还需要结合具体需求来选择合适的测量方法和相应的参数设置。

同时,根据不同的单片机型号和功能,可能还有其他特定的测量频率的方法,因此在实际应用中,需要根据具体的单片机型号和数据手册来选择合适的方法和配置参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PIC单片机等精度测量频率法

单片机测量频率,是一个比较常见但又不好解决的问题。

主要是测量频率是高端和低端不能兼顾的问题。

测量频率无非两种方法:

1.在一段固定的时间及脉冲的个数,然后除时间得到频率。

2.测量脉宽计算频率。

第一种方法,适合测频率在1KHz以上的脉冲信号。

因为要保证测量精度在0.1%,至少要保证脉冲个数在1000个,假设测10HZ左右的信号,则一个测试周期需要100秒,这显然不是我们所能接受的。

第二种方法,适合测频率小于1KHz的信号。

因为要保证测量精度在0.1%,在一个脉冲宽度(1ms)内,作为时标的定时器至少要走1000个数(此时PIC 的晶振理论上至少也要4MHz)。

事实上,想利用上述两种方法精确测量宽范围的频率,几乎是不可能的。

PIC系列特有的平级中断,也使其测量频率比51系列测量困难。

等精度数字测频基本框图

等精度数字测频基本框图如下

fx

图中的闸门G1、G2分别用来控制输入信号周期计数和闸门时间宽度计时。

其中,G1与输入信号同步,这样可使计数器N1的量化误差dN1=0。

计数器N2对标准时标信号Tc进行计数,并以此来测量实际的闸门宽度Tg,则输入信号的频率可表示为:

fx=N1/Tg=N1/(Tc*N2)

标准时标信号采用单片机自身的工作时钟,可看作常数。

因此fx的相对误差为:

dfx/fx=dN1/N1-dN2/N2=-dN2/N2

式中,dN2为计数器N2产生的量化误差,最大为±1个Tc,在实际设计中,选择适当的时标Tc和闸门宽度Tg可是N2始终足够大,以次在fx的全频段范围内得到足够高的精度。

等精度测量法的实质就是一种变相的测脉宽法。

在实际使用时(PIC为例),可将Timer0作计数器N1,Timer1作计数器N2,

外部中断INT0同T0连在一起,作为Tg信号,如图:

fx T0

INT0

PIC

首先打开INT中断,允许Timer0计数,当一个fx的上升沿来临时,触发INT中断。

在INT中断中,打开Timer1计数器,同时禁止INT中断。

延时0.5秒,打开INT中断,当INT中断再次发生后,关闭Timer1、Timer0计数器。

此时的频率为:

fx =fc* N1/N2

式中,fc为PIC的工作时钟,当时用4HMz晶体时,fc=1MHz。